Table of Contents

Intel Z600 User Manual

Displayed below is the user manual for Z600 by Intel which is a product in the Processors category. This manual has pages.

Related Manuals

Document Number: 325310-001

Intel® Atom™ Processor Z6xx

Series

Datasheet

For the Intel® Atom™ Processo r Z670 on 45-nm Process

Technology

April 2011

Revision 001

2 Datasheet

INFORMATION IN THIS DOCUMENT I S PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR

IMPLIED, BY ESTOPPEL OR OTHERWI SE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT

AS PROVIDED IN INTEL'S TER M S AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY

WHATSOEVER, AND IN TEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL

PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS F OR A PARTICULAR PURP OSE, MER CHAN TABILI TY,

OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIG HT.

UNLESS OTHERWI SE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS AR E NOT DESIGNED NOR INTEN D ED FOR ANY

APPLI CATI ON IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR

DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the

absence or character i stics of any featur es or inst ructi ons marked "res er ved" or "undefined. " Int el r eserves thes e for future

definitio n and shall have no responsibili t y w hatso ev er for conflicts or incompatibili ti es arising from future changes to them. The

informatio n here is subject to change without notice. Do not finaliz e a design with this information.

The Intel® A tom™ Pr ocessor Z670 component may contain d esign defec ts or errors known as errata which may cause the

product to deviate from published specifications. Current characterized errata are available on request.

For Enhanced Intel SpeedStep® Technology : See the Process o r Spec Finder at http://ark.intel.com or contact your Intel

repr e s e n t a tive for mor e information

Intel, Intel Atom and the Intel logo are trademarks of Intel Corporation in the U. S. and other countries.

*Other names and brands may be claimed as the property of others.

Copyright © 2011 Intel Corporation. All rights reserved.

Datasheet 3

Contents

1 Introduction ................................................................................................... 6

1.1 Processor Features ...................................................................................6

1.2 Interfaces ...............................................................................................7

1.2.1 System Memory Support .............................................................7

1.2.2 Disp la y Con tr oller .......................................................................7

1.2.3 cDMI .........................................................................................7

1.2.4 cDVO ........................................................................................8

1.2.5 LVDS ........................................................................................8

1.3 Terminology ............................................................................................8

1.4 Reference Docum ents ...............................................................................9

2 Signal Descriptions ....................................................................................... 11

2.1 Sign al Descr iption .................................................................................. 11

2.1.1 System Memory Interface .......................................................... 11

2.1.2 cDMI Interface ......................................................................... 13

2.1.3 cDVO Interface ......................................................................... 13

2.1.4 LVDS Display Port Interface ....................................................... 14

2.1.5 LGI/LGIe (Legacy) Signals ......................................................... 15

2.1.6 Debu g a nd Miscellaneous Signa ls ................................................ 16

2.1.7 Power Signals .......................................................................... 17

3 Power Manageme nt ...................................................................................... 18

3.1 Proc essor Cor e Low Powe r F e a tures ......................................................... 18

3.1.1 Cx State D efinition s .................................................................. 20

4 Electrical Speci f i c ati ons ................................................................................ 22

4.1 Pow er and Gr ound Balls .......................................................................... 22

4.2 Decoupling Guidelin es ............................................................................ 22

4.3 Voltage Rail D ecoup ling .......................................................................... 22

4.4 Voltage Ide ntifica tion (VID) ..................................................................... 23

4.4.1 VID Enable .............................................................................. 23

4.4.2 VID Table ................................................................................ 24

4.5 Absolute Maximum R atings ..................................................................... 25

4.6 DC Specific a tions ................................................................................... 26

5 Thermal Specif icati ons and Design Considera t ions ....................................... 31

5.1 Tempe r a ture Monitoring ......................................................................... 32

5.2 Intel® Ther m al Monitor ........................................................................... 32

5.2.1 Digital Th e r m a l Sensor .............................................................. 34

5.2.2 Out of Specification Dete c tion .................................................... 35

5.2.3 Catastrophic Th e r m al Prot ection ................................................. 35

5.2.4 PROCHOT# Signal Pin ............................................................... 35

4 Datasheet

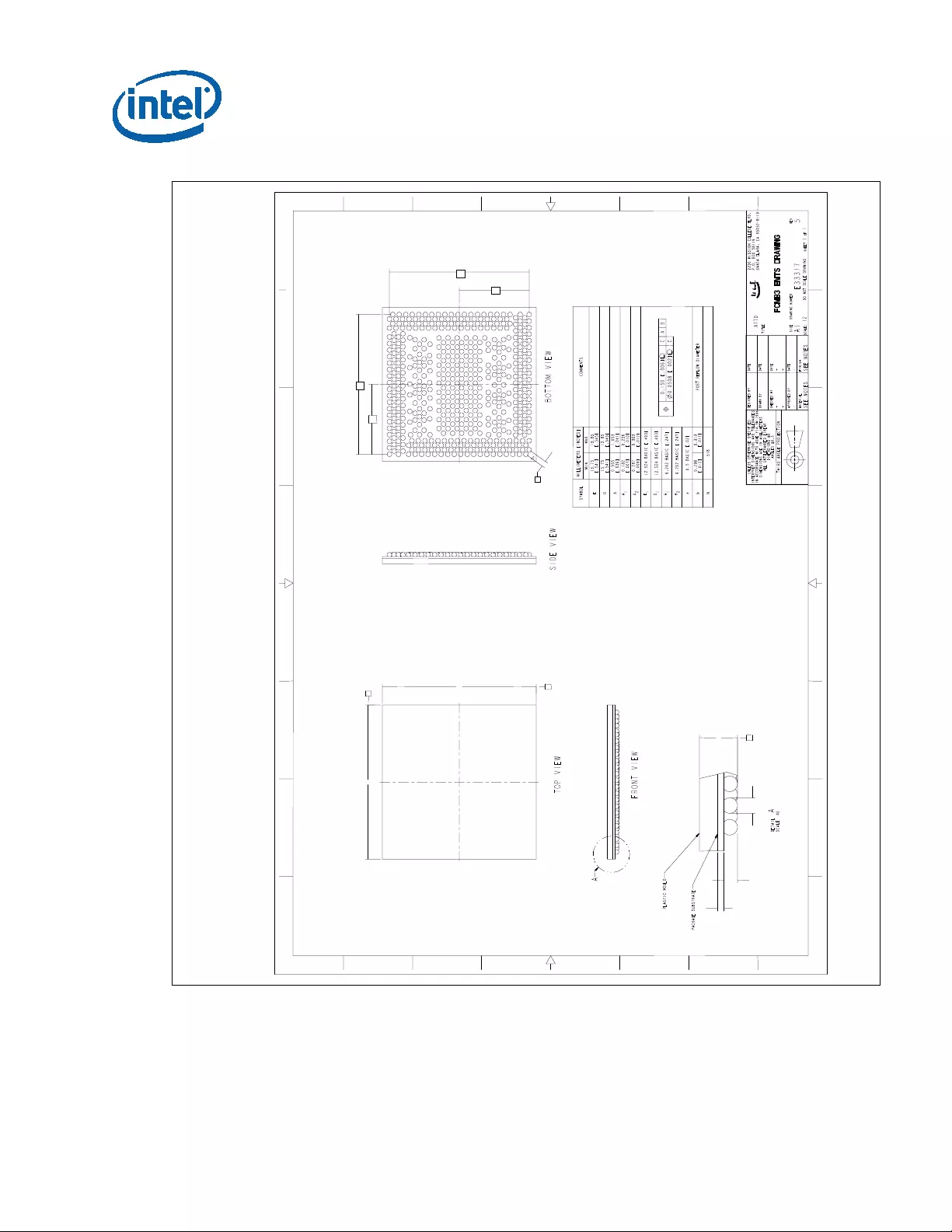

6 Package M echa nical S pecif i c a tions and Pi n Information ............................... 37

6.1 Package Mechanical Specifications ........................................................... 37

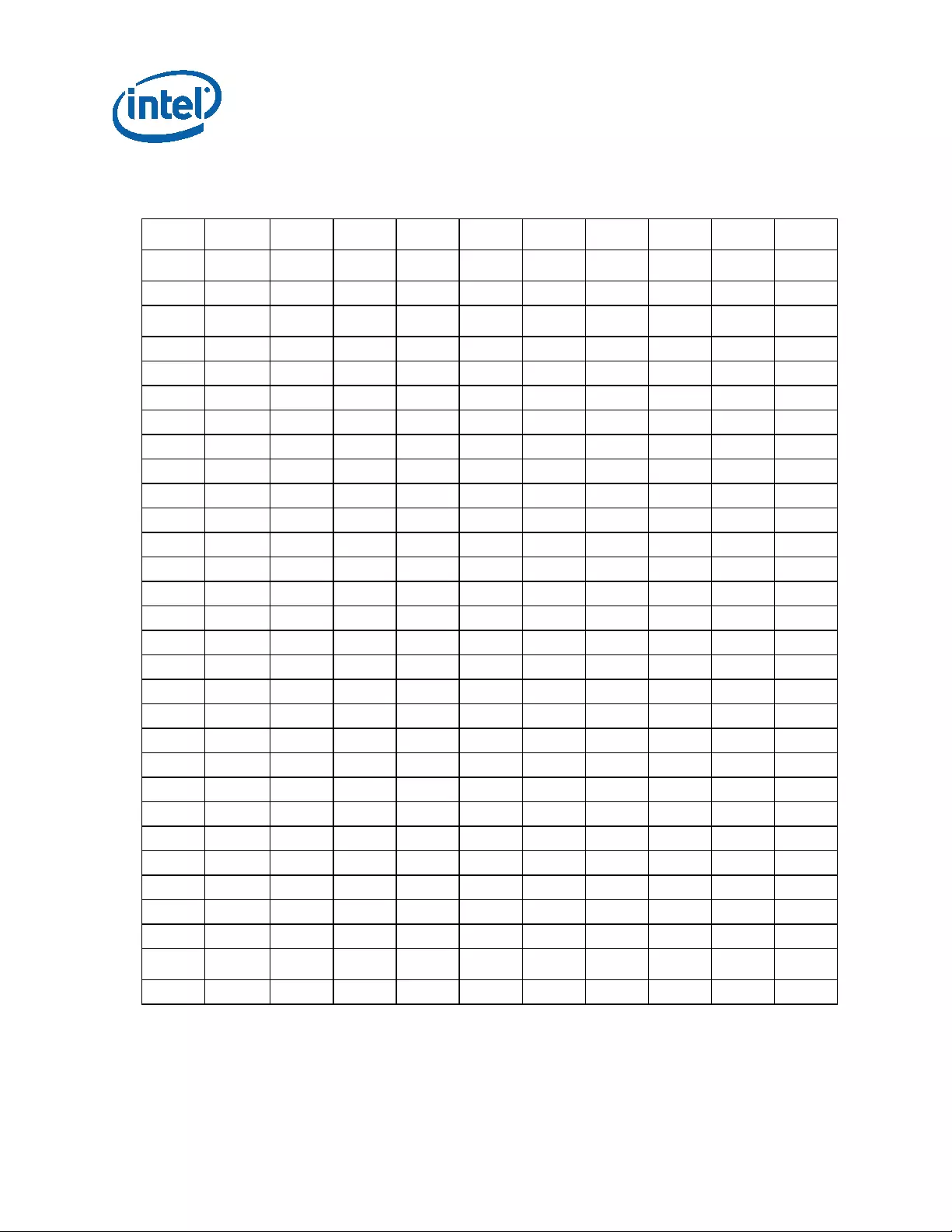

6.2 Proc essor Pinout Assignm ent ................................................................... 39

Figures

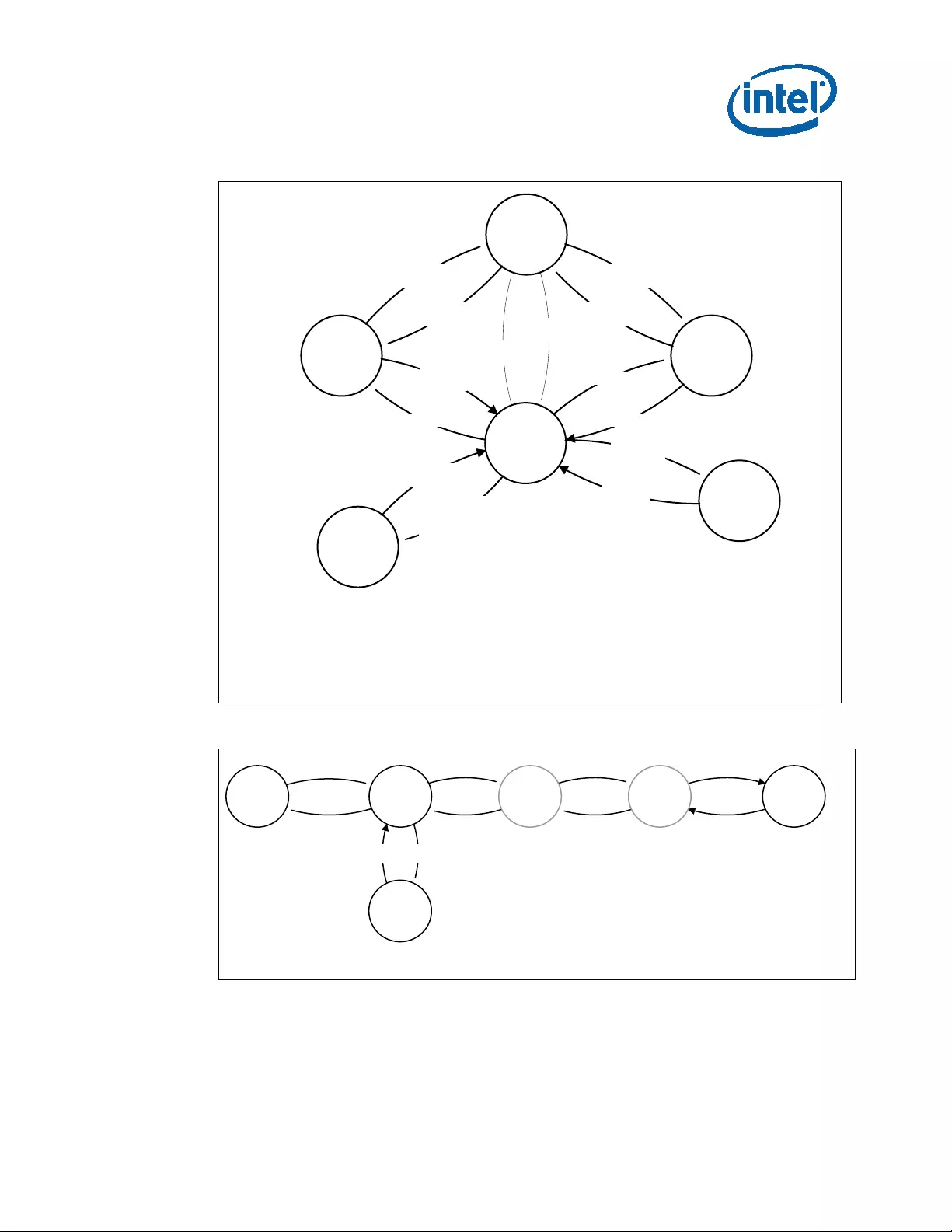

Figure 3-1. T hread Low Power States .................................................................. 19

Figure 3-2. P a c kage Low Power S tates ................................................................ 19

Figure 6-1. Package Mechanical Drawing ............................................................. 38

Tables

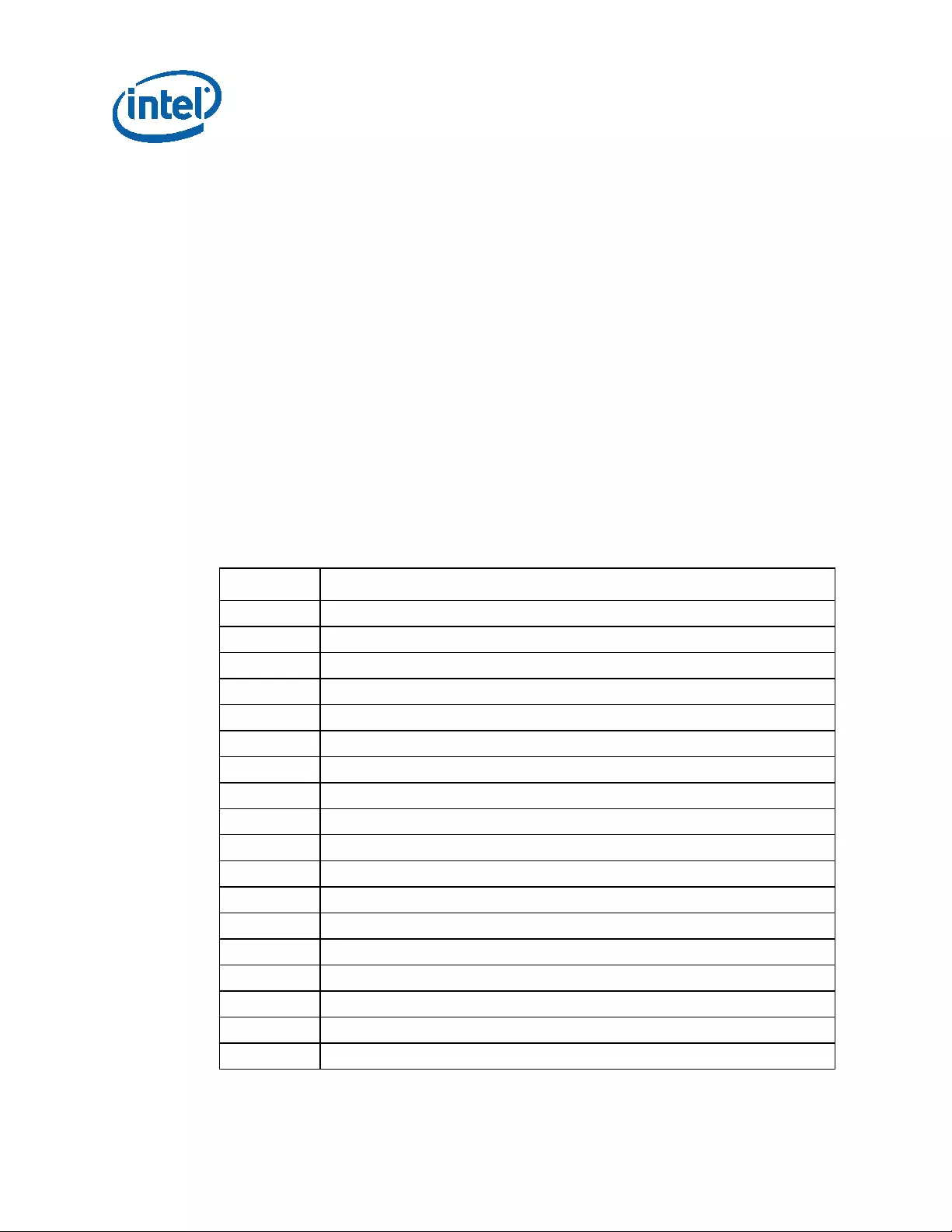

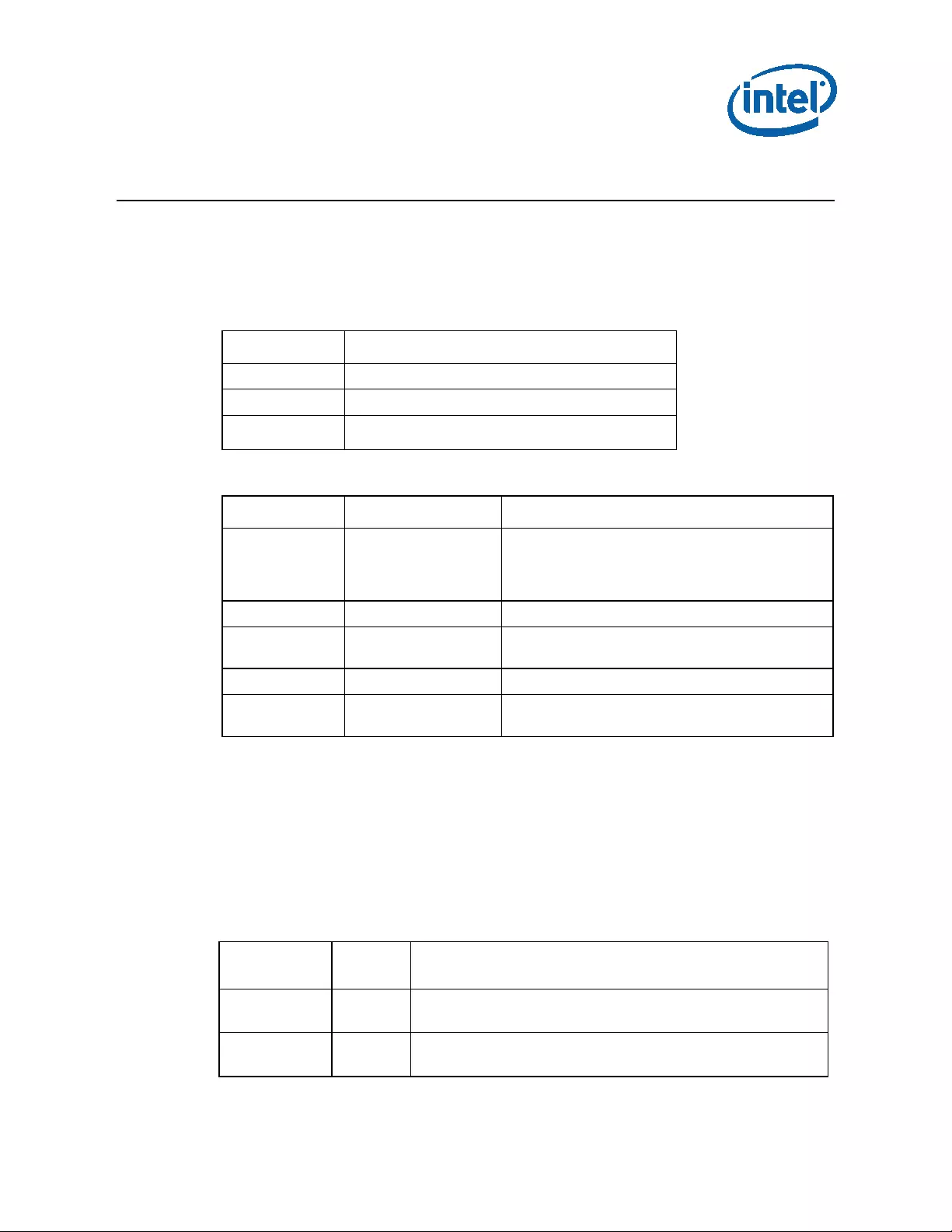

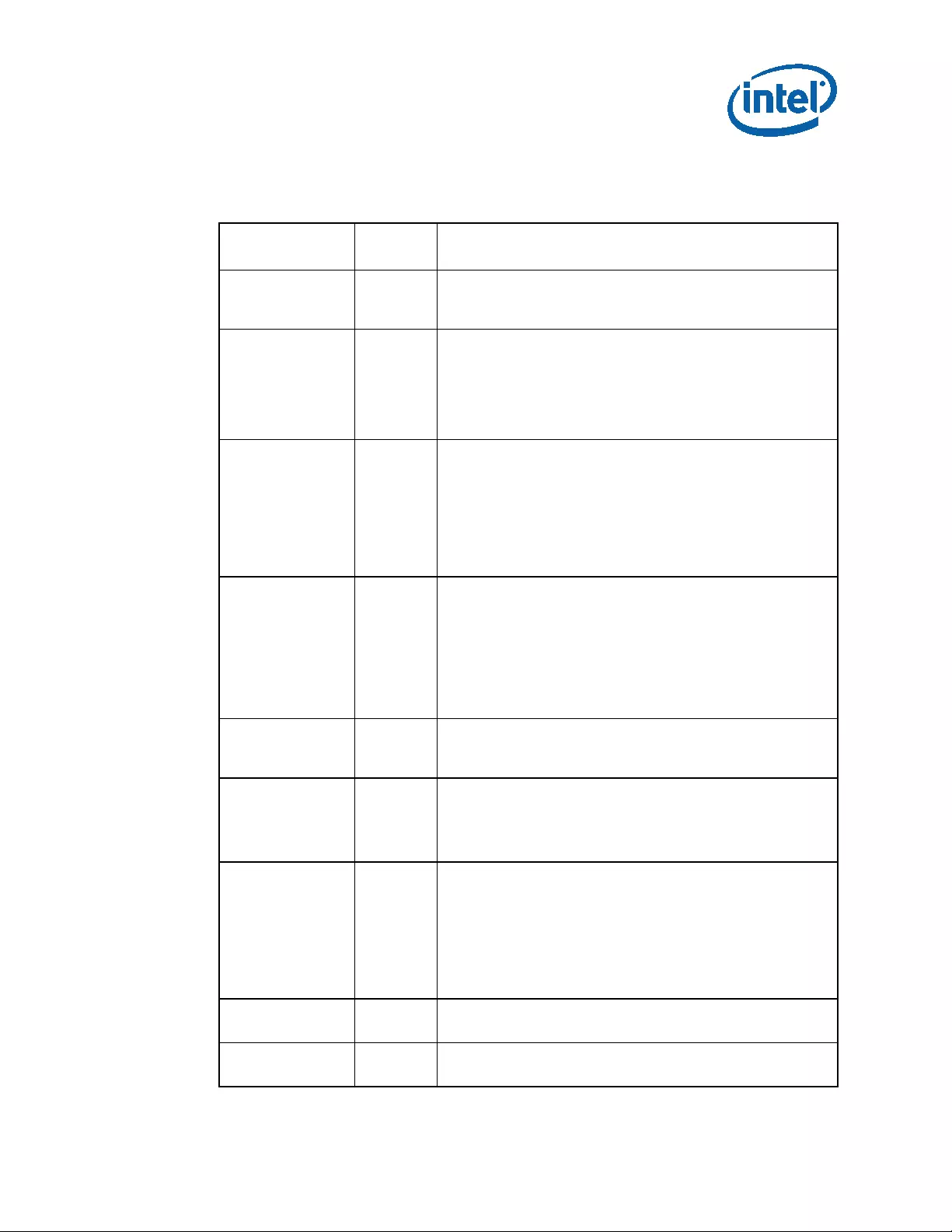

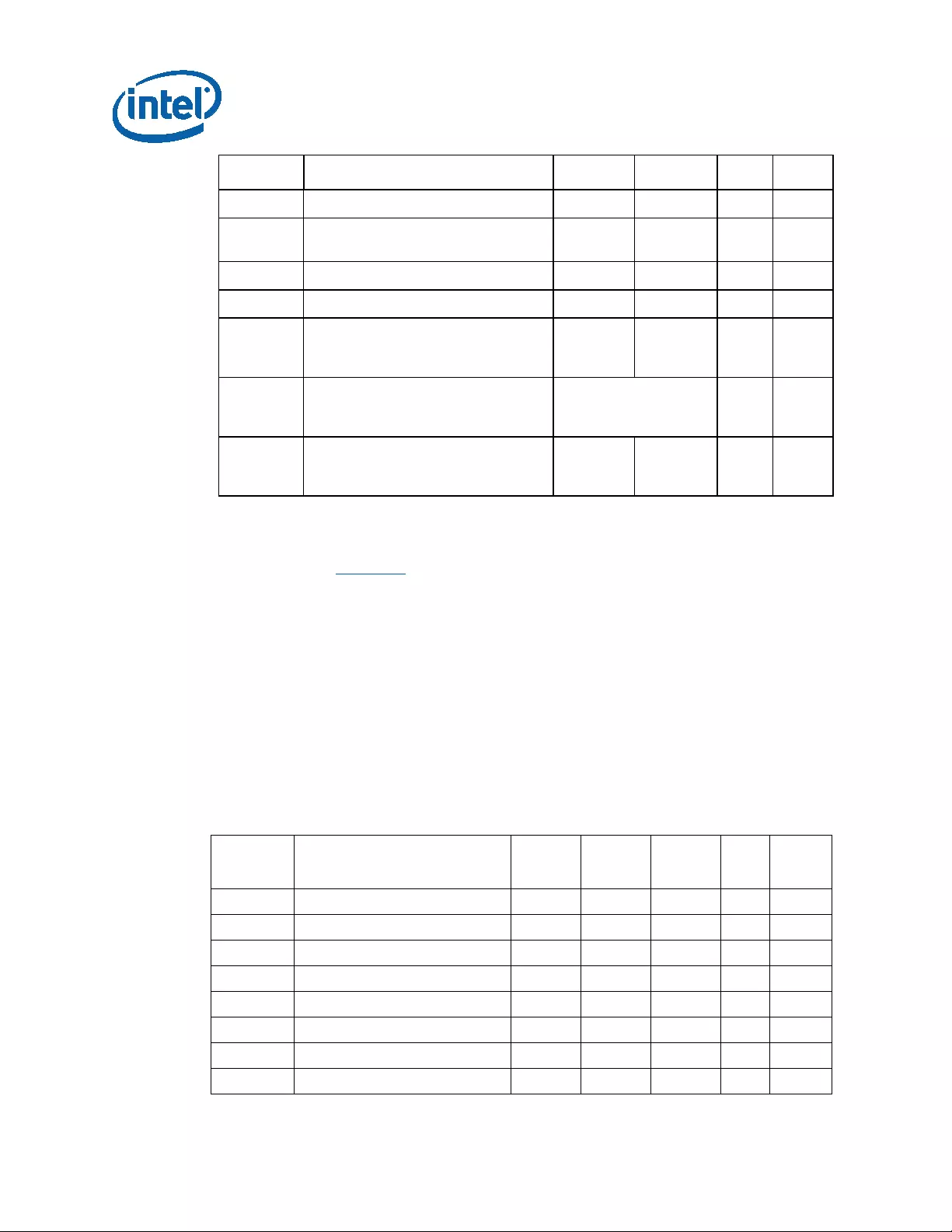

Table 2-1. Signal Types ..................................................................................... 11

Table 2-2. Buffer Types ..................................................................................... 11

Table 2-3. System Memory Interface Sign a ls ....................................................... 11

Table 2-4. cDMI Interface Signal ........................................................................ 13

Table 2-5. cDVO Interface Signals ...................................................................... 13

Table 2-6. LVDS Display Port Interface Signals ..................................................... 14

Table 2-7. LGI/LGI e Lega c y Signals .................................................................... 15

Table 2-8. Debu g a nd Miscellan eous Signals ........................................................ 16

Table 2-9. Power Signals ................................................................................... 17

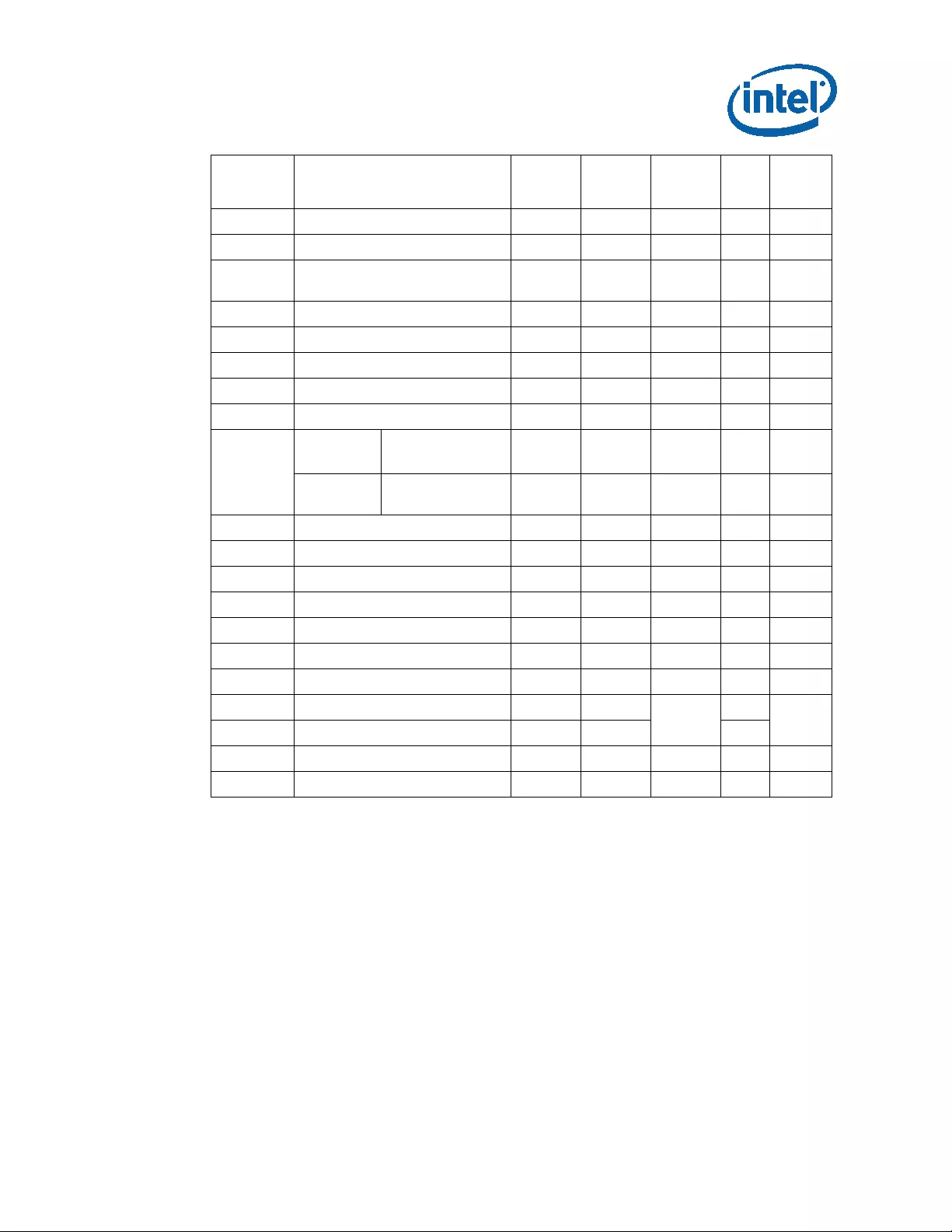

Table 4-1. VIDEN Encoding ................................................................................ 23

Table 4-2. VID Table ......................................................................................... 24

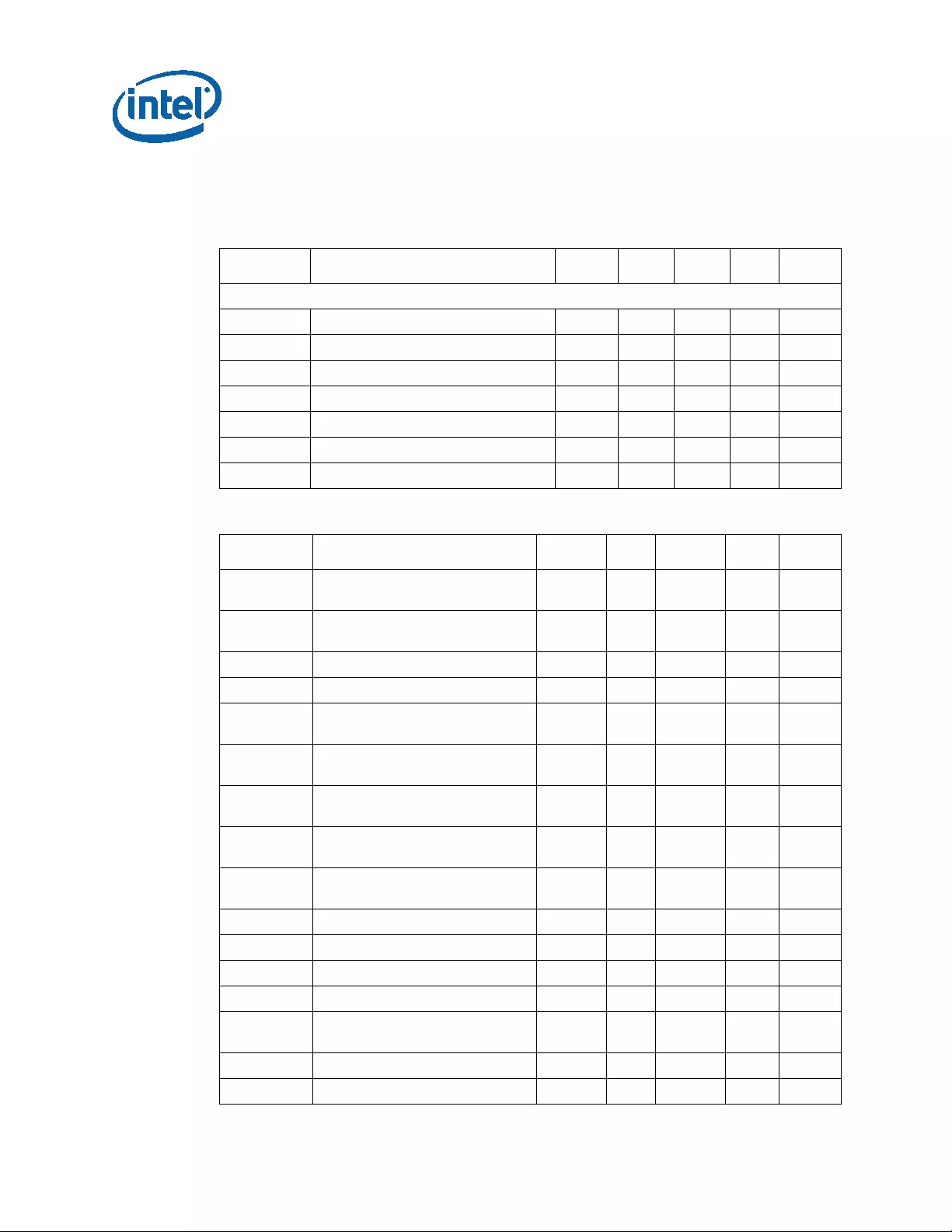

Table 4-3. Absolute Maximum Ratings ................................................................. 25

Table 4-4. Voltage a nd Cu rre nt Specificati ons ...................................................... 26

Table 4-5. Differential Clock DC Spec ificati ons ...................................................... 28

Table 4-6. AGTL+, CM O S , and C MOS Open Drain Signal Group D C Specifications ..... 28

Table 4-7. CMOS1 .8 Sign a l Group DC Specification s .............................................. 29

Table 4-8. LVDS S ignal Group DC Specific ations ................................................... 29

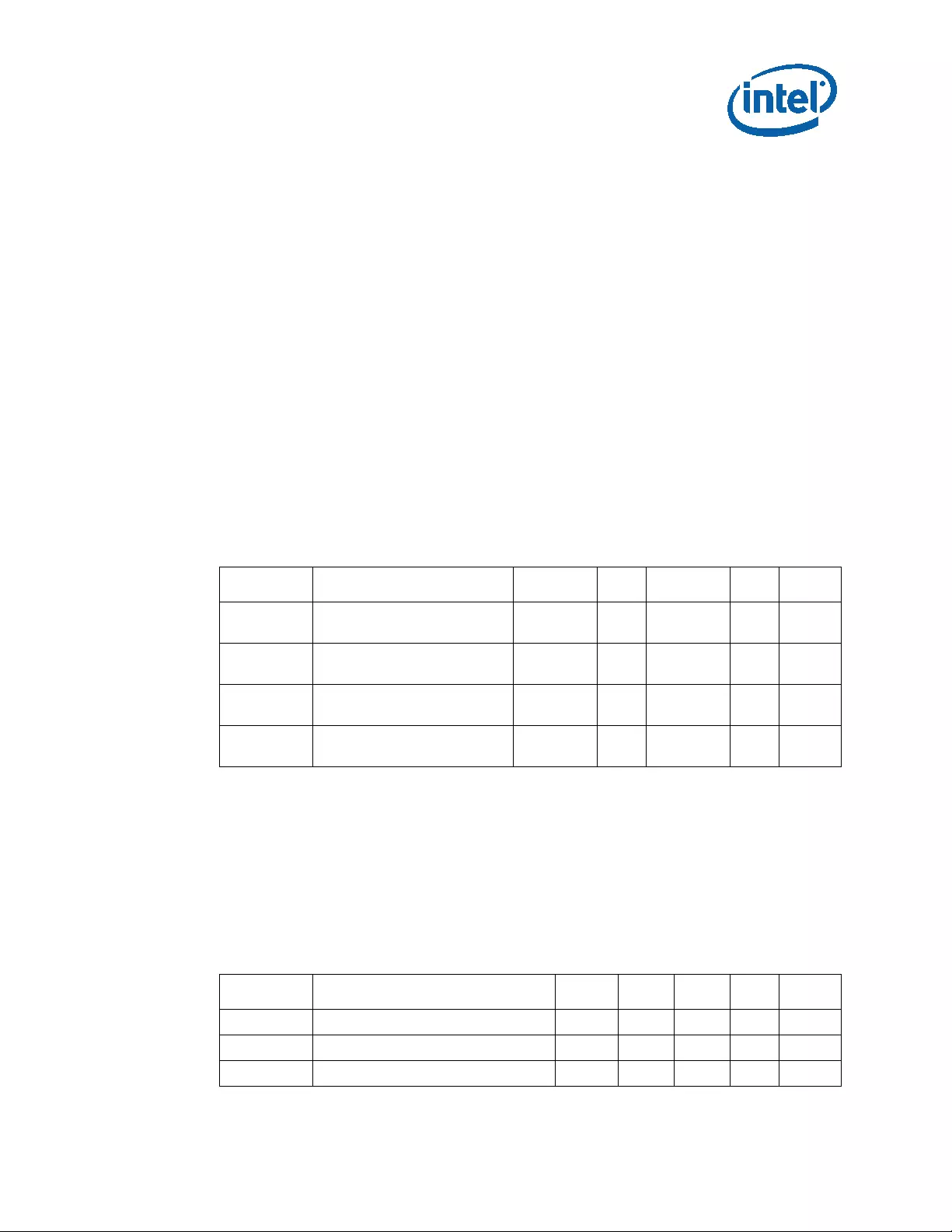

Table 5-1. Thermal Design Power Specifications ................................................... 31

Table 5-2. Support for PRO CHOT #/THERM TRIP# in Ac tive and Idle Sta tes ............... 34

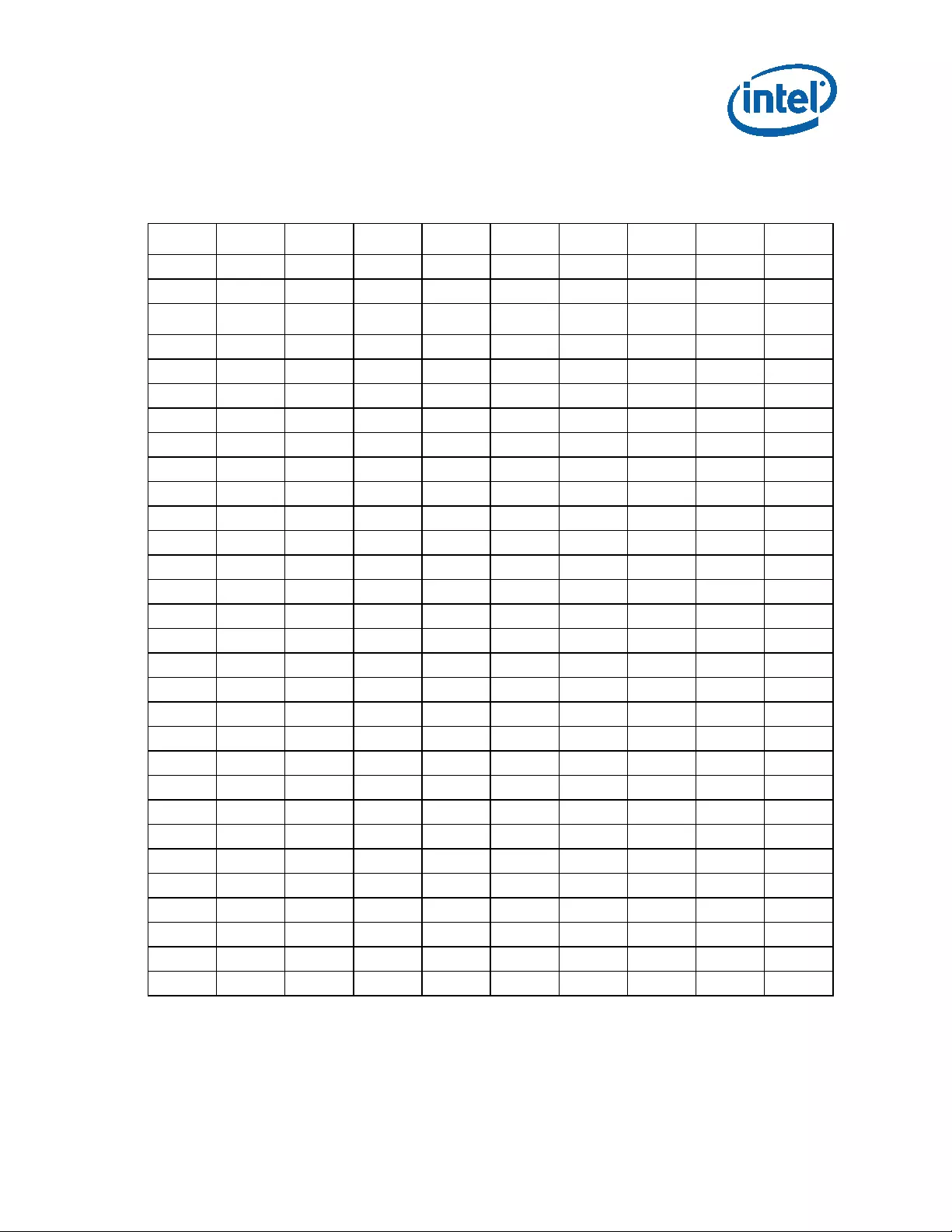

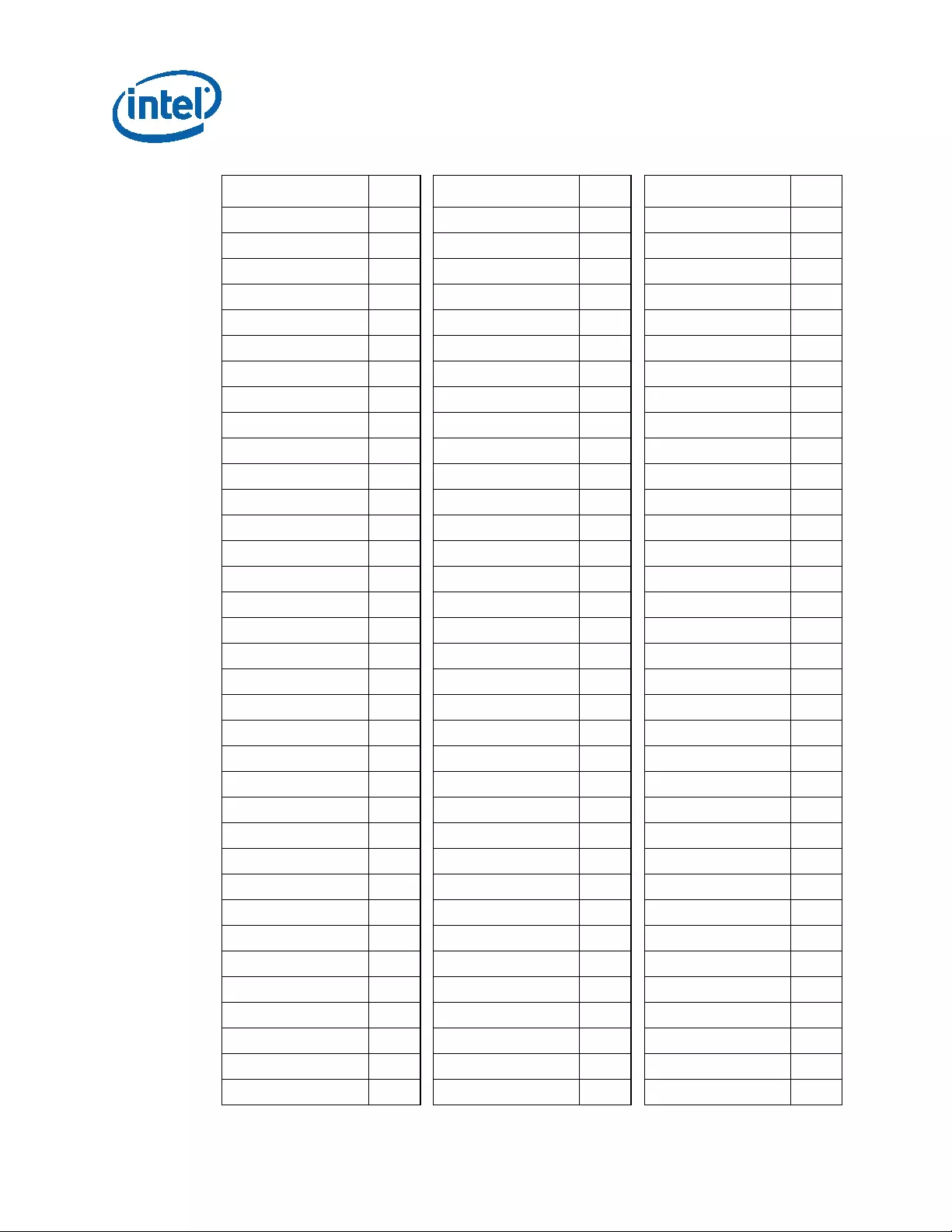

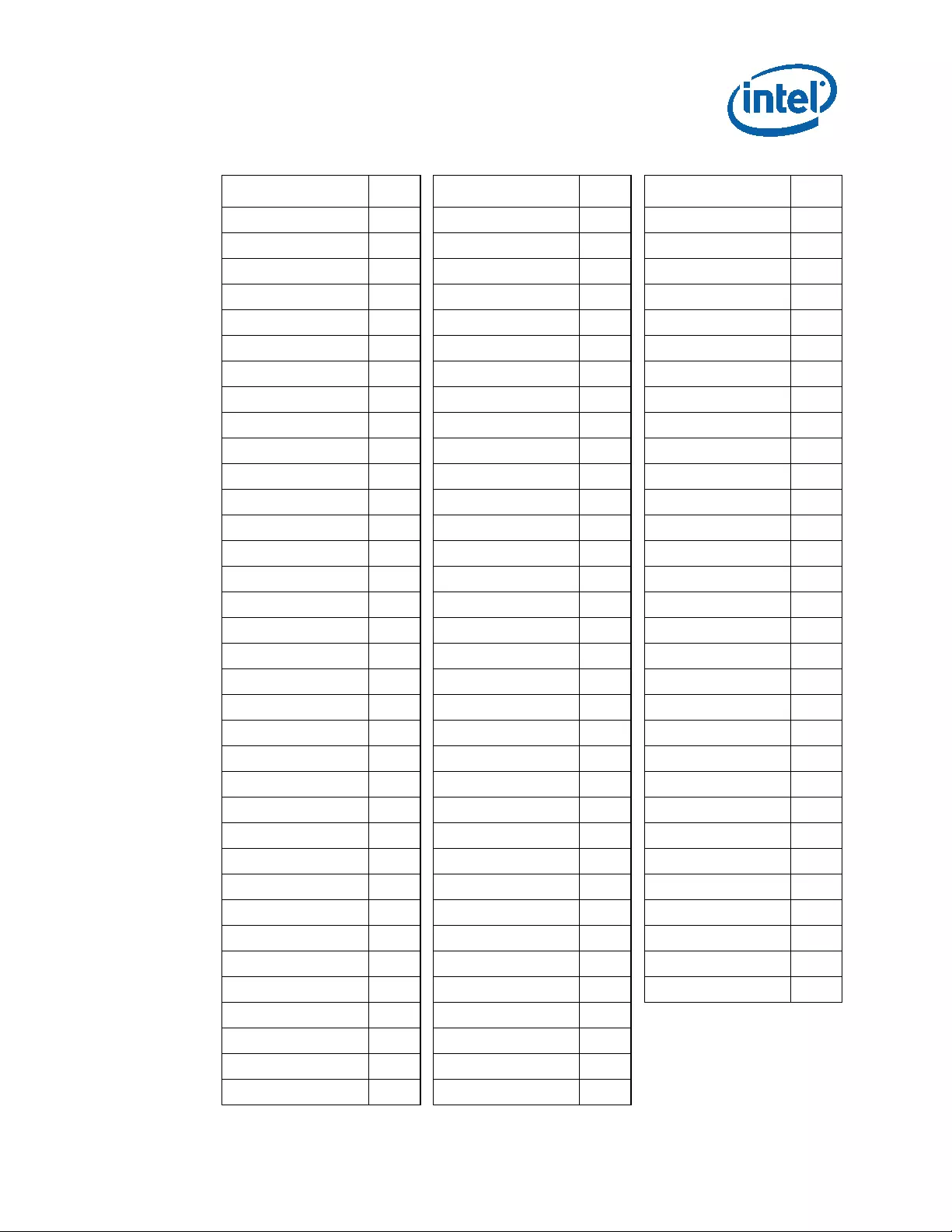

Table 6-1. P rocessor Pinout (Top View—Columns 21–31) ....................................... 40

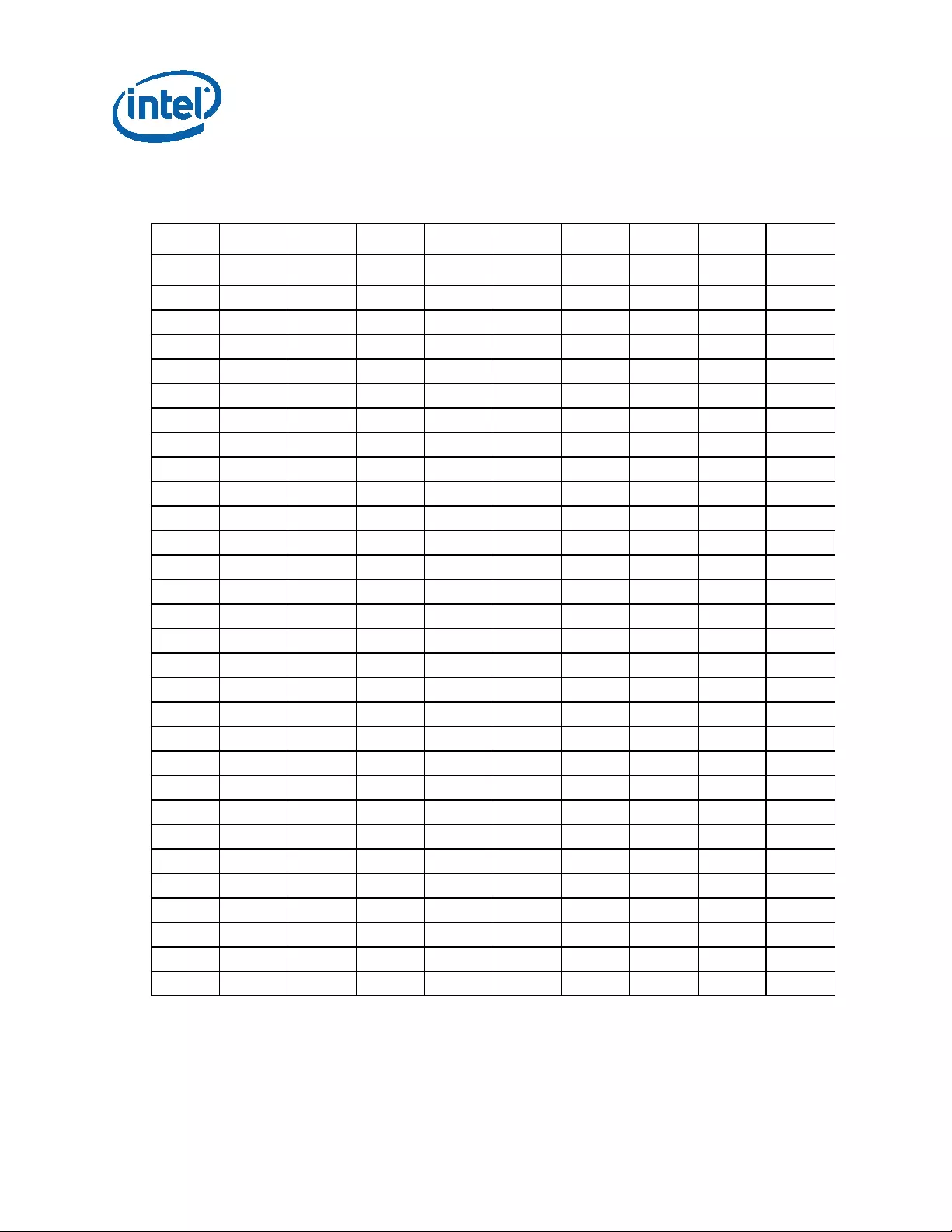

Table 6-2. P rocessor Pinout (Top View—Columns 11–20) ....................................... 41

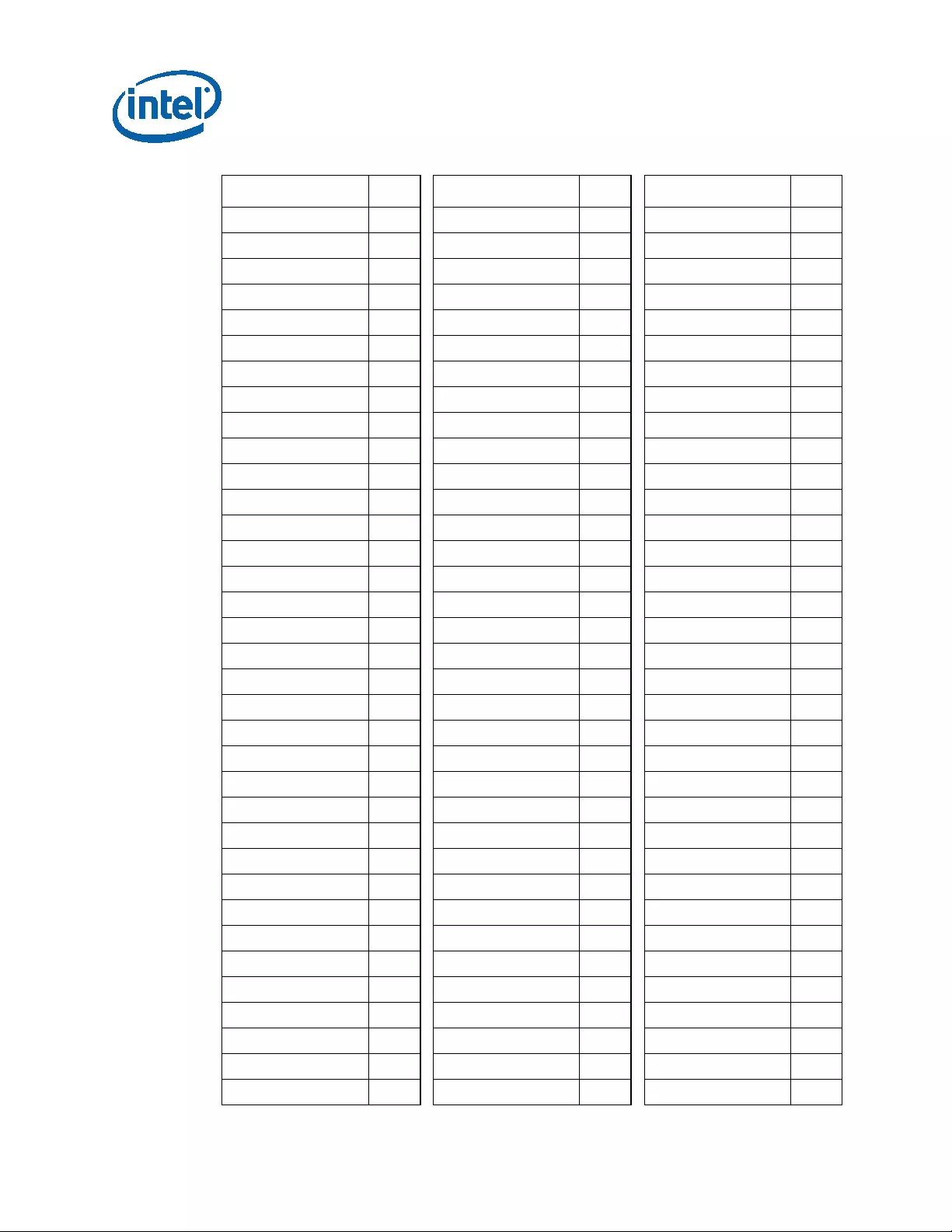

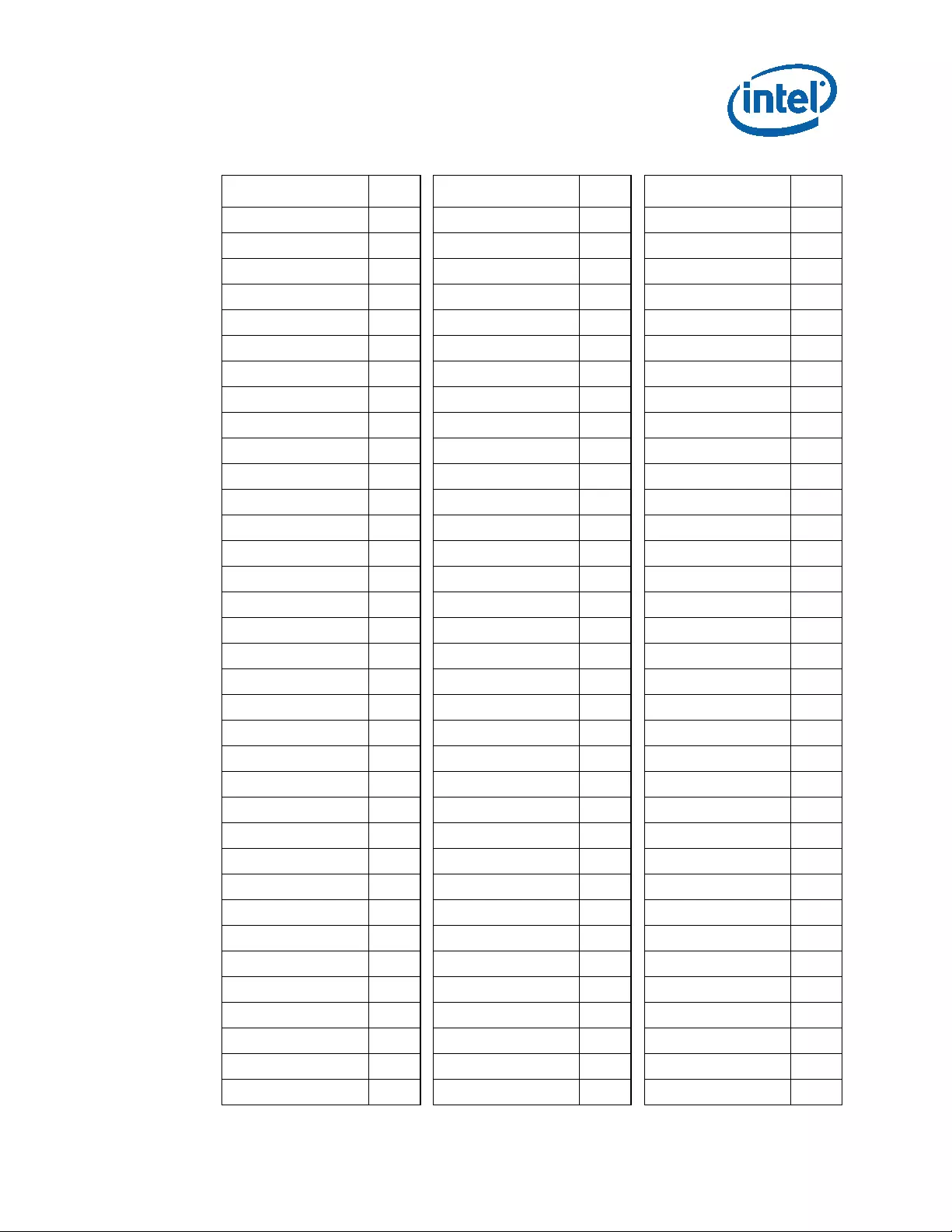

Table 6-3. P rocessor Pinout (Top View—Columns 1–10) ........................................ 42

Table 6-4. Pinout—Ordered by Signal Name ......................................................... 43

Datasheet 5

Revision History

Document

Number Revision

Number Description Revisio n Da te

325314 001 • Initia l r e l e as e . April 2011

§

Introduction

6 Datasheet

1 Introduction

The datasheet describes the architecture, fea tures, bu ffers, sign a l desc r iptions, pow er

managem ent, pin states, operating para m eters, and specifications for the Intel®

Atom™ Process or Z670 (Core Processor and North Compl e x).

Inte l® Atom™ Processor Z670 is the nex t ge nerati on low pow e r IA-32 processor that

is based on th e new re-partitioning arch ite cture targeted for tablets and sleek

netbooks. Th e main components of In tel® Atom™ Proc essor Z6 70 are: an IA-

compatible processor c ore derived f r om the Intel® Atom™ processor, a single-channel

32-bit DDR 2 m emory controller, a 3-D graphics engine, video decode engines , a 2-D

display c ontroller, a cDMI interfa c e link to the Intel® SM35 Expr es s Ch ips et, and an

LVDS interface to su pp or t a prim a r y display interface link. An addition a l cDVO

interface is used for pixel data to the Intel® SM35 Expres s C hipset.

Throughout this document, the Intel® Atom™ Proces s or Z670 is r ef er r ed a s the

processor and Intel® S M35 Expres s Ch ipset is referred to a s th e c hipset.

1.1 Processor Features

The following list provides s ome of the key fe a tures on th is p r oc e s sor:

• Supports Intel® Hyper-Threading Tech nology

• 2-wide instruction dec ode and in -order execution

• 512 KB, 8 way L2 cache

• Support for IA 32-b it a r chitecture

• FCM B3 packaging technology

• Ther ma l m a nagement support using TM1 and TM2

• On die D igital Thermal Sensor ( D TS) f or thermal management sup por t using

Intel® Th er m al Monitor 1 (TM1) and Intel® Thermal M onitor 2 (TM2)

• Adva nced power management f ea tures including Enhanc ed Intel® SpeedStep®

Technology

• Supports C0/C1(e)/C2(e)/C4(e) power states

• In tel Deep P ow er Down Technology (C 6)

Introduction

Datasheet 7

1.2 Interfaces

1.2.1 System Memory Support

• One channel of DDR2 memory

• 32-bit data bus

• Memory DDR2 transfer rates of 800 MT/s

• Supports 1 G b, and 2 Gb devices

• Su pp or ts total memory size of 1 GB, and 2 GB

• Provides a ggres s ive power man a gement to reduce power c onsumption when idle

• Provides proa c tive page cl os ing policies to c lose un used pa ges

1.2.2 Display Controller

• Seven display plan es : Display Plane A, Display Plane B, Display C/sprite, Overlay,

Cursor A, Cursor B, and VGA

• Display Pipe A: Supports L VDS dis pla y interface

• Display Pipe B: Supports HDMI via chipset

• Maximum r e s olution (L VDS display):

1366 x 768 @ 18 bpp an d 60 f ps

• Supports 18 bpp

• Su pp or ts Non-Power of 2 Tilin g

• Output pixel width: 24 -b it RGB

• Suppor ts N V12 video data f or m a t

• Supports 3 x 3 panel fitter

• Dynamic P ower Sav ing Technology (DPST) 3.0

• Support 16 x 256 byte tile s iz e

• Su pp or ts overlay

• Su pp or ts g lobal con stant alpha b lending

1.2.3 cDMI

• Peak ra w B W of cDMI link per direction = 400 MT / s using a quad-pumped 8-bit

transmit and an 8-bit receive data bu s

• Supports low pow er m a nagement sc hemes

• Su pp or ts CMOS interfa ce

Introduction

8 Datasheet

1.2.4 cDVO

• Peak ra w B W of 800MT/s

• Supports low pow er m a nagement sc hemes

• Supports AGTL+ interface

1.2.5 LVDS

• Maximum r e s olution (inter nal displa y) of:

• 1366 x 768 @ 18 bpp a nd 60 fps

• Dot cl ock range from 2 0 –83 M Hz

• Four differential signal pairs: Three data pairs (up to 581 Mbps on each data link)

and one clock pair

• Supports 18 bpp pa c ked an d 18 bpp loosely pack ed pixel formats

• Supports 24 bpp with a limited num ber of validated panels.

1.3 Terminology

Acronym Description

ACPI Advanced Configuration and Power Interface

AGTL+ Assis te d Gunning Transceiver Log ic Plus

CKE Clock enable

CMOS Co mple me nta ry metal-oxide semiconductor

cDMI CMOS Direc t Media I nterface

cDVO CMOS Digital Vid eo Output

DDR2 Second-generation Double Data Rate SDRAM memory technology

DQ Memory data

DQS Memory data strobe

DTS Digital thermal sensor

FSB Front side bus

GPIO General purpose input/output

GTL Gunning Tr ans c e ive r Logic

HPLL Host phase lock loop

IERR Internal error

iFSB Internal front side bus

LFM Low Frequency Mode

LGI Legacy interface

Introduction

Datasheet 9

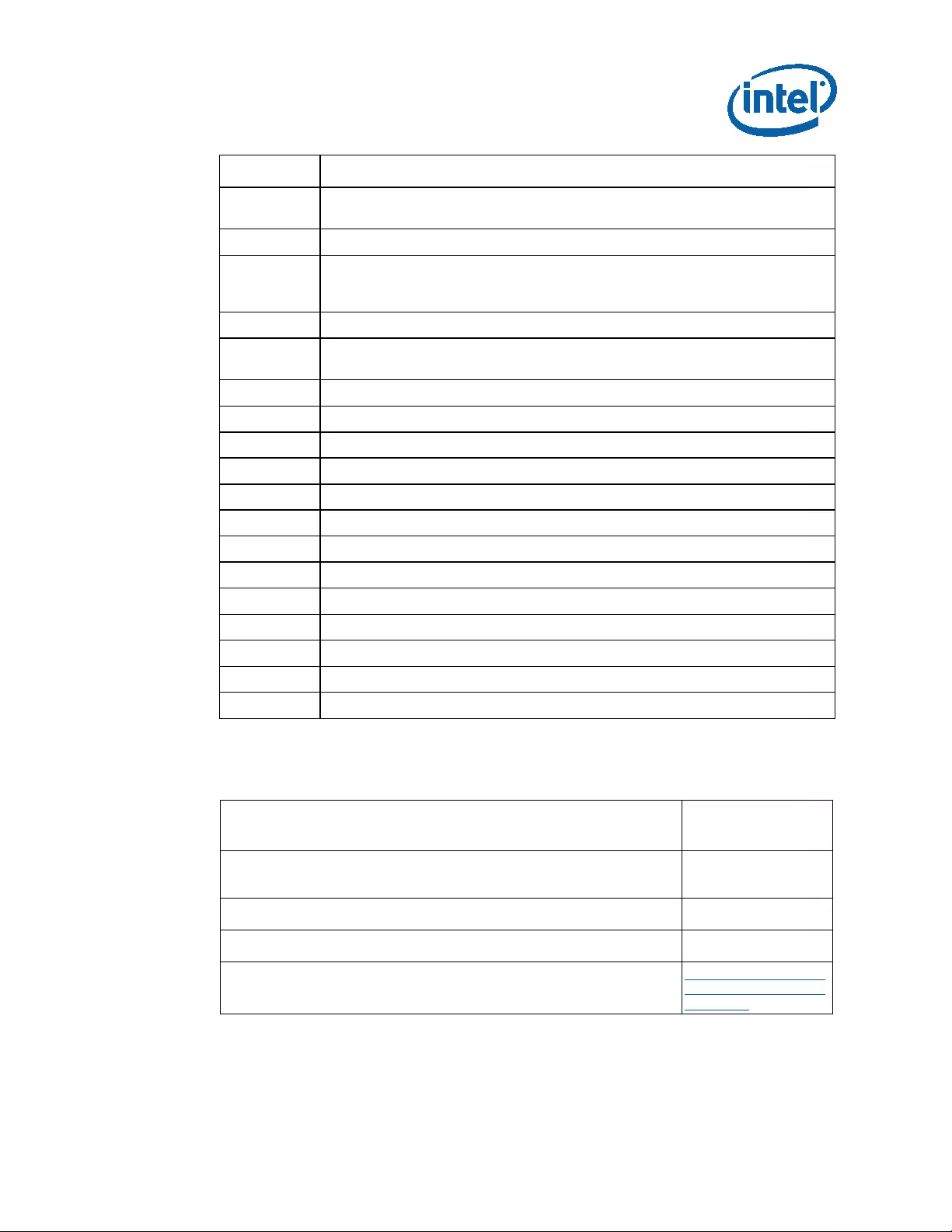

Acronym Description

LVDS Low Voltage Differential Signaling, a high speed, low powe r data tr ans mi s s ion

standar d used for disp l ay connectio ns to LCD pane ls

MSR Model-specific register

NCTF Non-Critic al to F unc tion. NCTF locatio ns ar e typic ally redundant ground or

non-critic al reserved, so the los s of solder joint continuity at end of life

conditions will not affect the over a ll product functionality.

NMI Non-maskable interrupt

North

Complex Processor unicore which processor memory controller, Power Management

Unit and inter nal FSB Logic

ODT On Die Termination

PCH Platfo rm Controlle r Hub

PMIC Pow er Manag eme nt Inte gr ated Circuit

PMU Power Mana g ement Unit

RCOMP Resistor compensation

SCK System clock

SR Self-Refresh

TAP Test access point

TCC Thermal control circuit

TDP Thermal Design Power

TM1 Thermal Monitor 1

TM2 Thermal Monitor 2

VR Voltage regulator

1.4 Reference Documents

Document Location/

Comments

Intel® Ato m ™ Processor Z6xx Series Specification Update For the

Intel® Atom™ Processor Z670 on 45-nm Process Technology 325309-001

Intel® SM35 Express Chipset Datasheet 325308-001

Intel® SM35 Expre ss Chip s e t Spe c ific ation Update 325307-001

AP-485, Intel® Proce s so r Identification and the CPUID Instruction

http://www.intel.com/

Assets/PDF/appnote/2

41618.pdf

Introduction

10 Datasheet

Document Location/

Comments

Intel® 64 a n d I A-32 Architectures Software Developer's Manuals

Volume 1: Basic Architecture

http://www.intel.com

/products/processor/

manuals/index.htm

Volume 2A: Instr uc tion Set Reference, A-M

Volume 2B: Instruction Set Reference, N-Z

Volume 3A: Syste m Progra mming G uide

Volume 3B: Syste m Programming G uid e

NOTES:

1. Contact your Intel representative for the latest revision and document number of this

document.

§

Signal D escriptions

Datasheet 11

2 Signal Descriptions

This chapter describes the processor signals. They are arranged in functional groups

accord ing to their ass oc ia ted interface or c ategory. The following notations are used

to describe th e s ign a l ty pe.

Table 2-1. Signal T y pes

Notations Signal Type

I Input Pin

O Output Pin

I/O Bi-directional Input/Output Pin

Table 2-2. Buffer Types

Buffer Type Interface Description

AGTL+ cDVO, cDMI

Assisted Gunni ng Tr a nsc e i ve r Logic Plus:

CMOS open drain interf a ce signals that r e q uire

terminatio n. Refer to the AGTL+ I/O Specification

for complete details.

CMOS, CMOS_OD cDMI, cDVO, LGI, LGIE 1.05-V CMOS buffer or CMOS open drain.

Analog All Analog r ef er ence or out put: This may be used

as a threshol d voltage or for buffer compensati o n.

LVDS LVDS Low-voltage differential signal output buffers

CMOS1.8 DDR2 1.8-V CMOS buffer: These buffers can be

configured as Stub Series Termination Lo g ic .

2.1 Signal Description

This s ection provides a detailed d e s cription of Processor signals. The signals are

arranged in functional groups according to their associated interface.

2.1.1 System Memory Interface

Table 2-3. System Memory Interface Signals

Signal Direction

Type Description

SM_CK0 O

CMOS1.8 Differential DDR clock

SM_CK0# O

CMOS1.8 Complementary differential DDR clock.

Signal D escriptions

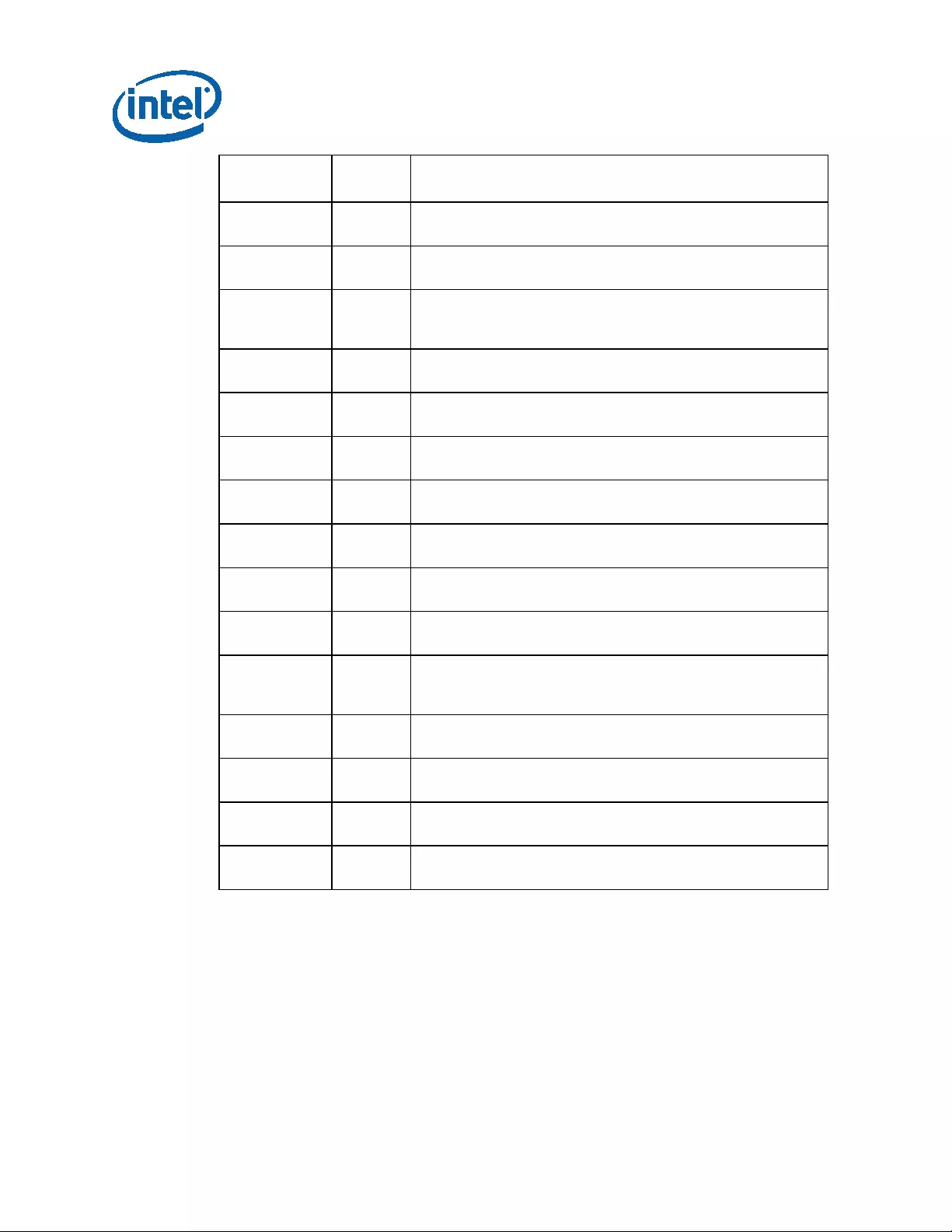

12 Datasheet

Signal Direction

Type Description

SM_SREN# I

CMOS1.8 Self-refresh enable: Signal from the chipse t asserted aft er

processor places DDR in self-refresh.

SM_CKE[1:0] O

CMOS1.8 Clock enable: SM_CKE is used for power control of the DRAM

devices. There is one SM_CKE per rank.

SM_CS[1:0]# O

CMOS1.8

Chip select: These signals determine whether a command is

valid in a given cyc le for the devic e s connec te d to it. Ther e is

one chip selec t s ignal for e ac h rank .

SM_RAS# O

CMOS1.8 Row address strobe: This signal is used with SM_CAS # and

SM_WE# (along w ith S M_C S#) to def ine commands.

SM_CAS# O

CMOS1.8 Column address strobe: This sig nal is used with SM_ W E#,

SM_RAS#, and S M_CS# to define com mands .

SM_WE# O

CMOS1.8 Write enable: This signal is used with SM_CAS#, SM_RAS#,

and SM_CS# to define com mands .

SM_ODT[1:0] O

CMOS1.8 On Die Termination: Active Termination Control.

SM_BS[2:0] O

CMOS1.8 Bank select: The s e sig nals def ine which banks are being

addres sed within e ac h Rank.

SM_MA[14:0] O

CMOS1.8 Multiplexed address: SM_MA signals provide multip le xed row

and column addr ess to memory.

SM_DQ[31:0] I/O

CMOS1.8 Data lines: SM_DQ signals interface to the DRAM data bus.

SM_DQS[3:0] I/O

CMOS1.8

Data strobes: These signals are used during wr ite s and are

center ed with r esp ect to da ta. During re ads, the s e signals are

driven by memory device s and are edge aligned with data.

SM_DM[3:0] O

CMOS1.8 Data mask: One bit per byte indicating which bytes should be

written.

SM_RCVENIN I

CMOS1.8 Receive enable in: This input enables the SM_DQS input

buffers during reads.

SM_RCVENOUT O

CMOS1.8 Receive enable out: Part of the feedback used to enable the

DQS input buffers during reads.

SM_RCOMP I

Analog RCOMP: Connected to high-pre c i s io n resis tor on the

motherboard. Used to dynamically calibrate the driver stre ngths.

Signal D escriptions

Datasheet 13

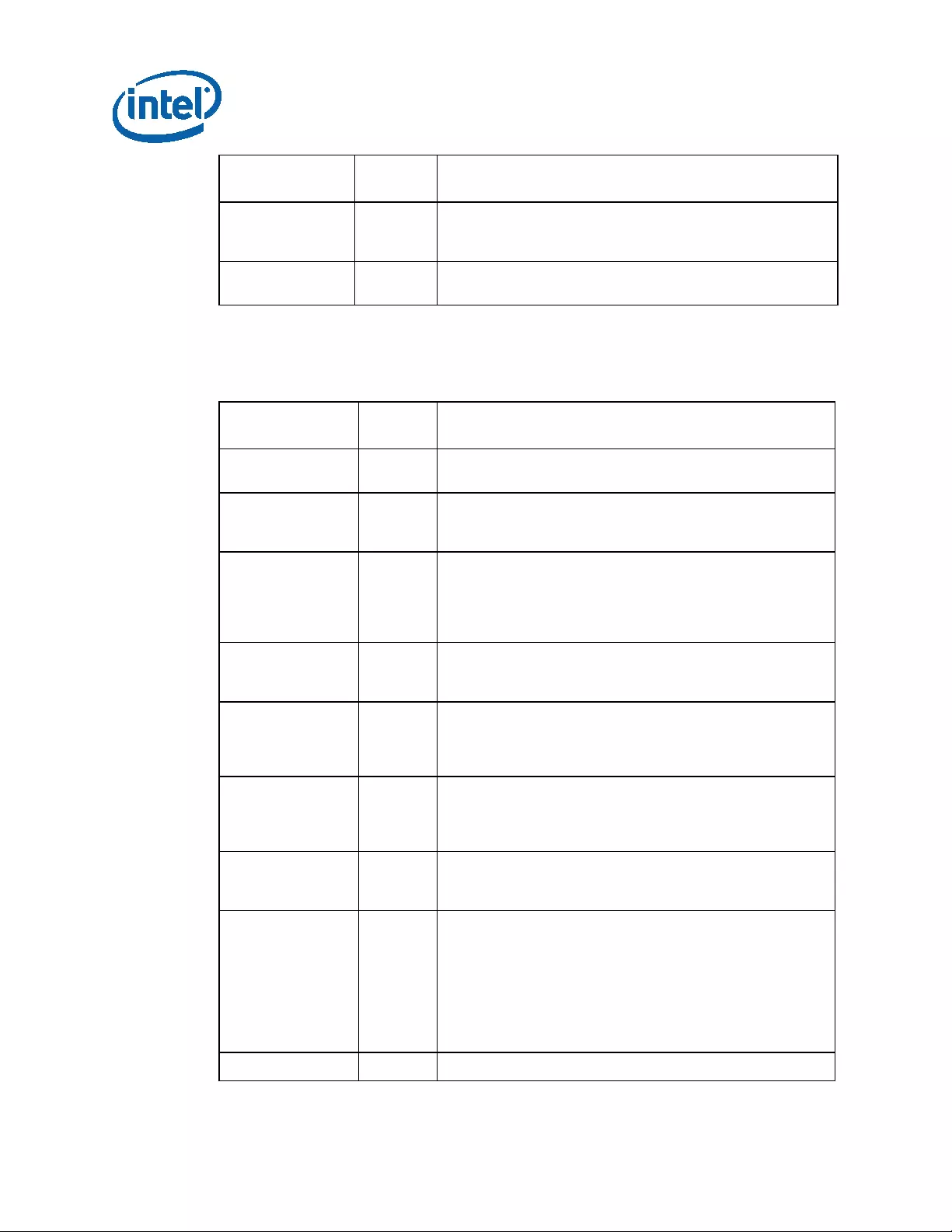

2.1.2 cDMI Interface

Table 2-4. cDMI Int erface Si gna l

Signal Direction

Type Description

CDMI_RCOMP[1:0] I

Analog

CDMI_RCOMP: Connected to hig h-precision resistors on

the motherb o ard. Used for compensating cDMI pull-up/pull-

down impedances.

CDMI_TX[7:0] O

CMOS Data output: quad-pump (strobed) data bus from

Processor to PCH.

CDMI_TXCHAR# O

CMOS

Data control character data control character output:

Quad-Pump (s trobe d) indication that CDMI _ T X [7:0]

contains a control character inste a d of da ta.

CDMI_TXDPWR# O

CMOS

Line wakeup for output: When asserte d, the PCH will

power-up its receivers on CDMI_TX[7:0] and

CDMI_ TXCH AR#, and CDMI_TXSTB[0].

CDMI_TXSTB_ODD#,

CDMI_TXSTB_EVEN# O

CMOS Data strobe output: Strobes for CDMI _TX[7:0] and

CDMI_TXCHAR#.

CDMI_RX[7:0] I

CMOS Data input: Quad-Pump (strobed) data bus from PCH to

Intel® Atom™ Processor Z670.

CDMI_RXCHAR# I

CMOS

Data control character input: Quad-pump (stro bed)

indicatio n that C DMI_RX[7:0] contains a control character

instead of data.

CDMI_RXDPWR# I

CMOS

Line wakeup for input: Power enable from PCH. Used to

enable Recei ve rs on CDMI_RX[ 7:0], CDMI_RXCHAR#, and

CDMI_RXSTB_ODD#.

CDMI_RXSTB_ODD#,

CDMI_RXSTB_EVEN# I

CMOS Data strobe input: Strobes for CDMI_RX[7:0] and

CDMI_RXCHAR#.

CDMI_GVREF I

Analog

Strobe Signals' Reference Voltage for DMI: Externally

set by means of a passive voltage divider. Voltage should be

1/2 VCCP when conf ig ured for CMOS.

CDMI_CVREF I

Analog

Non-Strobe Sign als' Referenc e V oltage f or DMI:

Externa lly set by means of a passive voltage divider.

Voltag e sho uld be 1/2 VCCP when configured for CMOS.

2.1.3 cDVO Interface

Table 2-5. cDVO Interface Signals

Signal Direction

Type Description

CDVO_RCOMP[1:0] I

Analog

CDVO_RCOMP: Connected to hig h-precision resistors on

the motherb o ard. Used for compensating pull-up/pull-

down impedances.

CDVO_TX[5:0] O

AGTL+ Data output: Quad-pump (strobed) data bus from Intel®

Atom™ Pr oces sor Z6 70 to PCH.

Signal D escriptions

14 Datasheet

Signal Direction

Type Description

CDVO_STALL# I

AGTL+ Stall: Allows PCH to throttle the se nd i ng of display data.

CDVO_TXDPWR# O

AGTL+

Line wakeup for output: When asserte d, the PCH will

power-up its receivers on CD V O_TX[5:0] and

CDVO_TXSTB_ODD#.

CDVO_TXSTB_ODD#,

CDVO_TXSTB_EVEN# O

AGTL+ Data strobe output: Str obes for CDVO_TX[ 5:0].

CDVO_VBLANK# I

AGTL+ Vertical blank: Indication from PCH indicating the s tart of

the vertical b lank p er iod .

CDVO_GVREF I

Analog

Strobe signals' reference voltage for CDVO: Externally

set by means o f a passive voltage divider. Voltage should

be 2/3 VCCP when configured for GTL.

CDVO_CVREF I

Analog

Non-Strobe Sign als' Referenc e V oltage f or CDVO:

Externa lly set by means of a passive voltage divider.

Voltag e sho uld be 2/3 VCCP when configured for GTL.

2.1.4 LVDS Display Port Interface

Table 2-6. LVDS Display Port Interface Signals

Signal Direction

Type Description

LA_DATAN[3:0] O

LVDS Differential Data Output (Negative)

LA_DATAP[3:0] O

LVDS Differential Data Output (Positive)

LA_CLKN O

LVDS Differential Clock Output (Negativ e)

LA_CLKP O

LVDS Differential Clock Output (Positive)

LA_IBG I

Analog External Voltage Ref BG: Connecte d to high-precision

resis tor on motherb oard to VSS.

LA_VBG I

Analog External Voltage Ref BG: Requires external 1.25 V ±2%

supply.

Signal D escriptions

Datasheet 15

2.1.5 LGI/LGIe (Legacy) Signals

Table 2-7. LGI/LGIe Legacy Signals

Signal Direction

Type Description

VID[6:0] O

CMOS

Voltage ID: Connects to PMIC. Indicates a desired vo ltag e

for either VCC or V NN depending on the VIDEN[] pins.

Resolution of 12.5 mV.

VIDEN[1:0] O

CMOS

Voltage ID enable: Connec ts to PMIC. Indicates which

voltag e is being spe c if i ed on the VID pins:

00 = VID is invalid

01 = VID = VCC

10 = VID = VNN

11 = RS VD

THERMTRIP# O

CMOS_OD

Catastrophic Thermal Trip: Th e pr ocessor protects itself

from catastr op hic ov er he ating by us e of an inter nal the rmal

sensor. This sens or is set well abo ve the normal operating

temperature to ensure that there ar e no false trip s . The

proce ssor will sto p all exe c uti o n w he n the junc tio n

temperatur e exc eeds approxim at el y 120° C. This condition is

signaled to the sys tem by the THERMTRI P# (Ther ma l Trip )

pin.

PROCHOT#

I/O

O:

CMOS_OD

I: CMOS

Processor hot: As an output, PROCHO T# (processor hot)

will go activ e whe n the proce ssor temperature monito ring

sensor detects that the processor has reached its maximum

safe oper a ting tempe r a tur e . This indicate s that the proc ess or

Thermal Control Circuit (TCC) has been activated, if e nab led.

As an input, asserti o n of PROCHO T# by the syste m will

activate the TCC , if enable d . The TC C will re ma in ac tive until

the system de-ass erts PR OCHOT# .

VSSSENSE,

VCCSENSE,

VNNSENSE

O

Analog

Voltage sense: Connects to PMIC. Voltage Regulator must

connect feedback lines for VCC, VSS, and VNN to these pins on

the packag e .

BSEL1 O

CMOS

BSEL1: Selects external reference clock for DDR 2, cDMI, and

cDVO frequencies.

1 = Reserved

0 = 100 MHz, for cDVO/DDR2-800MT/s.

IERR O

CMOS

IERR: Internal error indic a tion (de bug). Positive l y asserted.

Asserte d whe n the proce ssor has had an inter nal error and

may have unexpecte dly stopped executing. A s ser tion of IERR

is usually ac co mpanie d by a SHUTDOWN tra ns ac tion internal

to Processor which may result in assertion of NMI to the

proce ssor . The pro ces sor w ill ke ep IERR as ser ted until the

POWERMODE[] pins take Processor to reset or Processor

receives a reset message over cDMI.

GTLREF0 I

Analog Voltage reference for BPM[3:0]#: 2/3 VCCP by mean s of an

external voltage divider: 1k Ω to VCCP, 2 KΩ to VSS.

GTLREF1 I

Analog Voltage reference: 2/ 3 V CCP by me a ns of external volta g e

divider: 1 KΩ to VCCP, 2 KΩ to VSS.

Signal D escriptions

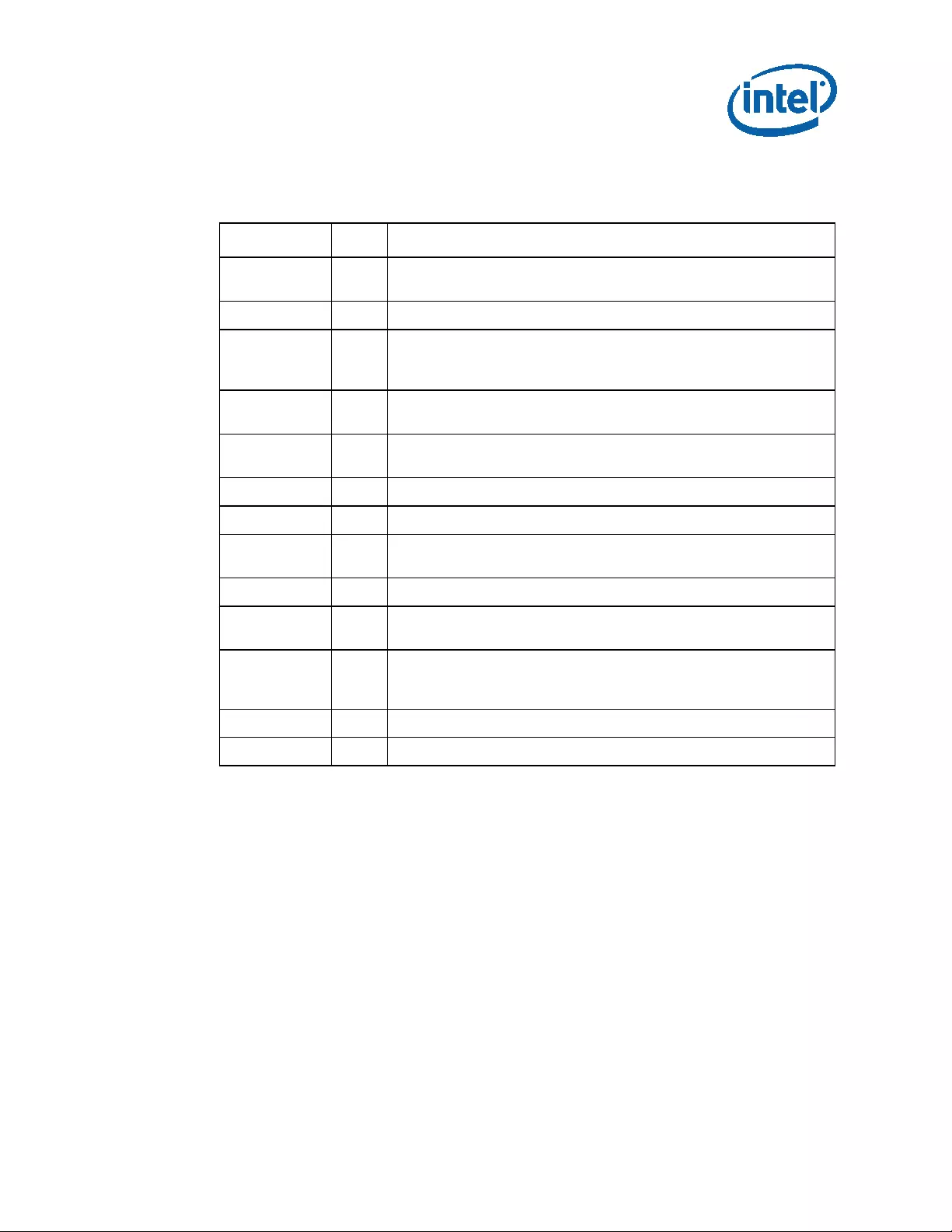

16 Datasheet

Signal Direction

Type Description

PWRMODE[2:0] I

CMOS

Power mode: The chipset is expected to sequence Processor

throug h var ious sta te s using the PO WERMO DE[] pins to

facilitate c o ld res e t, and warm reset.

BCLK_P/N I

CMOS Reference clock: D ifferential 100 MHz.

2.1.6 Debug and Miscellaneous Signals

Table 2-8. Debug a nd Miscellaneous Signals

Signal Direction

Type Description

BPM[3:0]# I/O

AGTL+ Break/perf monitor: Various debug input and output

functions.

PRDY# I/O

AGTL+

Probe mode ready: The processor’s respons e to a PRDY#

asser tion. This signal indic a tes that the processor is in probe

mode. Input is unused.

PREQ# I/O

AGTL+

Probe mode request: Assertion is a request for the

proce ssor to enter pro be mode. Pr oc e ssor will r e spond with

PRDY# assertion once it has entered. PREQ# ca n be enabled

to cause the processor to break from C4 and C6. Internal

51 Ω pull up, so no external pull-up req uired.

TCK I

CMOS

Processor JTAG test clock: This s ignal provides the clo ck

input for the pro ces so r Tes t Bus (also known as the Test

Access Port). Requi r es an external 51 Ω resistor to Vss.

TDI I

CMOS

Processor JTAG test data input: This s ignal transfers

serial te s t data into the proc ess or . T DI prov ides the serial

input needed for JTAG specification support. Requires an

external 51 Ω resistor to VCCP.

TDO O

OD

Processor JTAG test data output: This sig nal transfers

serial te s t data out of the process or . TDO prov id es the seri al

output nee ded for JTA G spec ific ation support. Requires an

external 51 Ω resistor to VCCP.

TMS I

CMOS

Processor JTAG test mode select: A JTAG spe c ific ati o n

support signal used by debug tools. Requires an external 51

Ω resistor to VCCP.

TRST# I

CMOS

Processor JTAG test reset: As y nc hro nous ly rese ts the Test

Access Por t (TAP) lo g ic . TRST# must be driv e n asserted

(low) during processor power on reset.

Processor has an internal 51 Ω pull-up to VCCP, unlik e the

Pentium M proc ess or , the Intel® Core™2 processo r , and the

Intel® Atom™ Z5xx processor. The Processor pull-up

matches the Intel® Pentium® 4 processor and the IEEE

specification.

RSVD These pins shou l d be treat ed a s no connection (NC).

Signal D escriptions

Datasheet 17

2.1.7 Power Signals

Table 2-9. Power Si gnals

Signal Type Description

VCC PWR Processor core supply voltage: Power supply is required for

processor cycles.

VNN PWR North Complex logic and graphics supply voltage.

VCCP PWR cDMI, cDVO, LGI, LGIe, JTAG, RCOMP, and power gating

supply voltage. Needed fo r most bus a ccesses. Cannot be

connec te d to VCCPAOAC during Standby or Self-Refresh states.

VCCPDDR PWR DDR DLL and logic supply voltage: Required for memory bus

accesses . Requires a separate rail with nois e isola tio n.

VCCPAOAC PWR JTAG, C6 SRAM supply voltage: Needs to be on in Active or

Standby.

LVD_VBG PWR LVDS band gap supply voltage: Needed for LVDS display.

VCCA PWR HPLL Analog PLL and thermal sensor supply voltage.

VCCA180 PWR LVDS analog supply voltage: Neede d for LVD S disp lay. Requires a

separate rail w ith no is e isolation.

VCCD180 PWR LVDS I/ O supply voltage: Needed for LVDS display.

VCC180SR PWR DDR2 self-refresh supply voltage: P owered during Active,

Standby, and Self-Refresh states.

VCC180 PWR DDR2 I/ O supply voltage Required for memory bus acces ses.

Cannot be conne c ted to VCC180SR during Standby or Self-Refresh

states.

VMM PWR I/O supply vol tage.

VSS Ground pin

§

Power Man ageme nt

18 Datasheet

3 Power Management

Processor supports fine grain pow er ma nagement by having s evera l pa r tit ion s of

voltage islan ds created through on-die power switches. T he Intel® Sm art Powe r

Tech nology (Intel® SPT) softw a r e determ ines the m ost power efficient sta te for the

platform at any g iven point in time a nd then provides guid a nce to tu r n ON or OFF

differ e nt voltage islands on processor. For the scenario w here In te l® SPT has directed

the processor to go in to an Intel® SIT idle mode, the processor waits for all partitions

with s hared voltage to reach a s af e point and then turns them off.

3.1 Processor Core Low Power Features

When the proc e s s or core is idle, low-power idle s tates (C-states) are used to save

power. More power savings actions are taken for numerica lly high e r C-states.

However , higher C-states have longer exit and e ntry laten c ies.

Figure 3-1 shows the thread low power states. Figure 3-2 shows the package low

power states.

Note: STPCLK#, DPSLP#, and DPRSTP are internal sig nals on ly.

Power Man ageme nt

Datasheet 19

Figure 3-1. Thread Low Power States

C2

†

C0

Stop

Grant

Core state

break

P_LVL2 or

MWAIT(C2)

C1/

MWAIT Core state

break

MWAIT(C1)

C1/Auto

Halt

Halt break

HLT instruction

C4

†

/C6

Core State

break

P_LVL4 or

P_LVL6

ø

MWAIT(C4/C6)

STPCLK#

de-asserted

STPCLK#

asserted

STPCLK#

de-asserted

STPCLK#

asserted

STPCLK#

de-asserted

STPCLK#

asserted

halt break = A20M# transition, INIT#, INTR, NMI, PREQ#, RESET#, SMI#, or APIC interrupt

core state break = (halt break OR Monitor event) AND STPCLK# high (not asserted)

† — STPCLK# assertion and de-assertion have no effect if a core is in C2 or C4.

Ø

— P_LVL6 read is issued once the L2 cache is reduced to zero.

Figure 3-2. Package Low Power Sta t es

DPRSTP# de-asserted

DPRSTP# asserted

Snoop

serviced

Snoop

occurs

STPCLK# asserted

STPCLK# de-asserted

SLP# asserted

SLP# de-asserted DPSLP# de-asserted

DPSLP# asserted

Stop

Grant

Snoop

Normal Stop

Grant

Deep

Sleep

††

Deeper

Sleep

†

Sleep

††

† — Deeper Sleep includes the C4 and C6 states

†† — Sleep and Deep Sleep are not states directly supported by the processor, but rather sub-states of Silverthorne’s C4/C6

Power Man ageme nt

20 Datasheet

3.1.1 Cx State Definitions

• C0 State—Full On

This is the only s tate that r uns s oftwar e. All clocks are running and the processor

core is active. The processor can service snoops and maintain cache coherency in

this state. All pow er m a nagement f or interfaces, cloc k gating , are contr olled at the

unit level.

• C1 State—Auto-Halt

The first lev el of power reduction occurs when the core processor executes an

Auto-Halt instru c tion. This stops the execution of the instru ction stre a m and greatly

reduces th e c or e pr oces s or’s power consumption. The core processor can service

snoops and maintain cache coherency in this state . The Processor North Complex

logic does not d is tinguis h C1 f r om C0 explic itly.

• C2 State—Stop G r a nt

The next lev el of power r e duction occurs when the core processor is placed into the

Stop Grant state. The core processor can service snoops and maintain cache

cohere ncy in this s ta te. The Nor th Comple x only s upports rece iving a single Stop

Grant.

Entr y into the C2 state w ill occur a fter the core processor requests C 2 ( or d ee per).

C2 state will be exited, entering the C 0 s ta te, when a break event is detecte d.

Processor must ensure that the DLLs a r e a w a ke and the memory will be out of self-

refresh at this point.

• C1E and C2E States

C1E and C2E states are transpar ent to the n or th complex logic. The C1E state is

the same as the C1 state, in that the core processor emits a HALT cycle when

entering the sta te . Ther e a r e no other visible ac tions from the c or e pr ocessor.

The C2E state is the same as the C2 state, in th a t the core proce s s or emits a Stop

Grant c y c le wh en entering the state. There are no other visible actions from th e

core processor.

• C4 State—Deeper Sleep

In this state, the core pr ocessor shu ts d own its P L L an d c annot ha ndle sn oop

reques ts. Th e c or e pr ocessor voltage r eg ulator is also told to reduce the process or ’s

voltage. Du ring the C4 s ta te, the Nor th Comple x will c ontinu e to handle tr a ffic to

memory so long as this traffic does not require a snoop (i.e., no coherent traf fic

requests are serviced).

The C4 state is entered by r ec eiv ing a C4 requ es t f r om the core processor / O S . The

exit from C4 occurs when the North Com plex detects a s noopable event or a br eak

event, wh ic h would ca use it to wak e up the core processor and initiate the C0

sequence.

Power Man ageme nt

Datasheet 21

• C4E

The C4E sta te is essentially the same as the C4 state except that th e c or e

process or will tra nsition to the Low Fr e quency Mode (LFM ) frequency a nd voltage

upon entry and exit of this state.

• C6—Deep Po wer Down

Prior to entering the C6 state, the c or e pr ocess or will flush its cache and save its

core context t o a s p ecial on-die SRAM on a differen t power plane. Onc e the C6

entry sequence h a s completed, the core pr oces s or ' s voltage can be completely shut

off.

The key dif ference f or the North C om plex logic betw een the C4 state and the C6

state is that sin ce the cor e proces sor's c ache is em p ty, there is no need to perform

snoops on the in ter nal FS B. This means that bus ma ster e vents ( which would ca use

a popup from the C4 state to the C2 state) can be allowed to flow un im peded

during the C6 state. However, the core processor m ust still be retur ned to the C0

state to servic e interru pts.

A residenc y counter is r ead by the core processor to enable an intelligent

promotion/d em otion based on energy awareness of transitions and history of

residencies/transitions.

§

Electrical Specifications

22 Datasheet

4 Electrical Specifications

This chapter contains signal gr oup descr iptions, a bs olute maximum r atings, voltage

identification and power sequen cing. Th is chapter a lso includes DC s pe c ificati ons.

4.1 Power and Ground Balls

The processor has Vcc and Vss (groun d) in puts for on -c hip power distribution . All

power balls mu s t be c on nected to their r es pective pr oces s or pow er planes, while all

Vss balls m ust be connec ted to th e s ystem groun d plane. Us e of multiple powe r a nd

ground planes is recomm ended to reduc e I*R drop. T he Vcc balls mus t be s upplied

with the voltage d etermined by the proc e s s or Volta g e Identification (VID) signals.

4.2 Decoupling Guidelines

Due to lar g e number of transistors and high inter nal clock speeds, th e pr oc essor is

capable of gen er a ting larg e c urrent swings between low and fu ll power s ta tes. This

may c ause voltag es on po wer plan e s to sag below their minimum values, if bulk

decouplin g is not adequate. Larger bulk storage (CBULK), such as electrolytic

capacitors, supply current during lon ger las ting chan ges in current demand (for

examp le, comin g out of an idle cond ition ) . Simila r ly, cap a citors ac t a s a stora ge well

for curren t when en tering an idle condit ion from a runn ing cond ition. To keep

voltages with in specif ic a ti on, output decoupling m ust be properly designed.

Caution: Design the boa r d to ens ure tha t the voltag e provided to the pr oc essor r emains within

the spec ification. F ailure to do s o can re s ult in timing violations or r e duced lifetime of

the processor.

4.3 Voltage Rail Decoupling

The voltage regulator s olution needs to pr ovide:

• Bulk capacitance with low effective series resistance (ESR).

• A low pa th impedance fr om the regulator t o the pro c e s sor.

• Bulk decoupling to compensate for large current swings gener a ted during power-

on, or low-power idle state entry/exit.

The power deliv er y solution m ust en su r e that the voltage and c urren t s p ec ifications

are met, as defined in Table 4-4.

Electrical Specifications

Datasheet 23

4.4 Voltage Identification (VID)

The VCC and VNN voltage inputs use two encoding pins ( VIDEN[1:0] ) to en a ble the VID

pin inputs a nd seven voltage iden tification pins (V ID[6:0]) to selec t th e power supply

voltage. The V ID/VIDEN pin s for th e p r oc e s sor are CM O S outpu ts driven b y the

processor VID circuitry. Table 4-2 specifies the v oltage level corresponding to the

state of VID[ 6:0]. A “1” in this r e fers to a high-v oltage level an d a “0” refer s to a

low-voltage level. F or m ore details abou t PMIC design to s upport th e processor power

supply requirements, r efer to the ven dor’ s s pec ification .

4.4.1 VID Enable

Both VCC and VNN are va r iable in Intel® Atom™ Proces sor Z670. Processor implements

a new VI D mec ha nism that minimiz es th e number of r equired pins. T he VID for VNN

and VCC are multiplexed on to the same set of pins and a separa te 2-bit enable/ ID is

defined to specify what the d r iven V ID corr es p onds to. O ne of th e combina tions is

used to notify that the VID is in valid. T his is used when th e processor is in C6/Standby

to tri-state th e VID pins to save power .

Table 4-1. VIDEN Encod ing

VIDEN[1:0] Description

00b VID is invalid

01b VID for VCC

10b VID for VNN

11b Reserved

Electrical Specifications

24 Datasheet

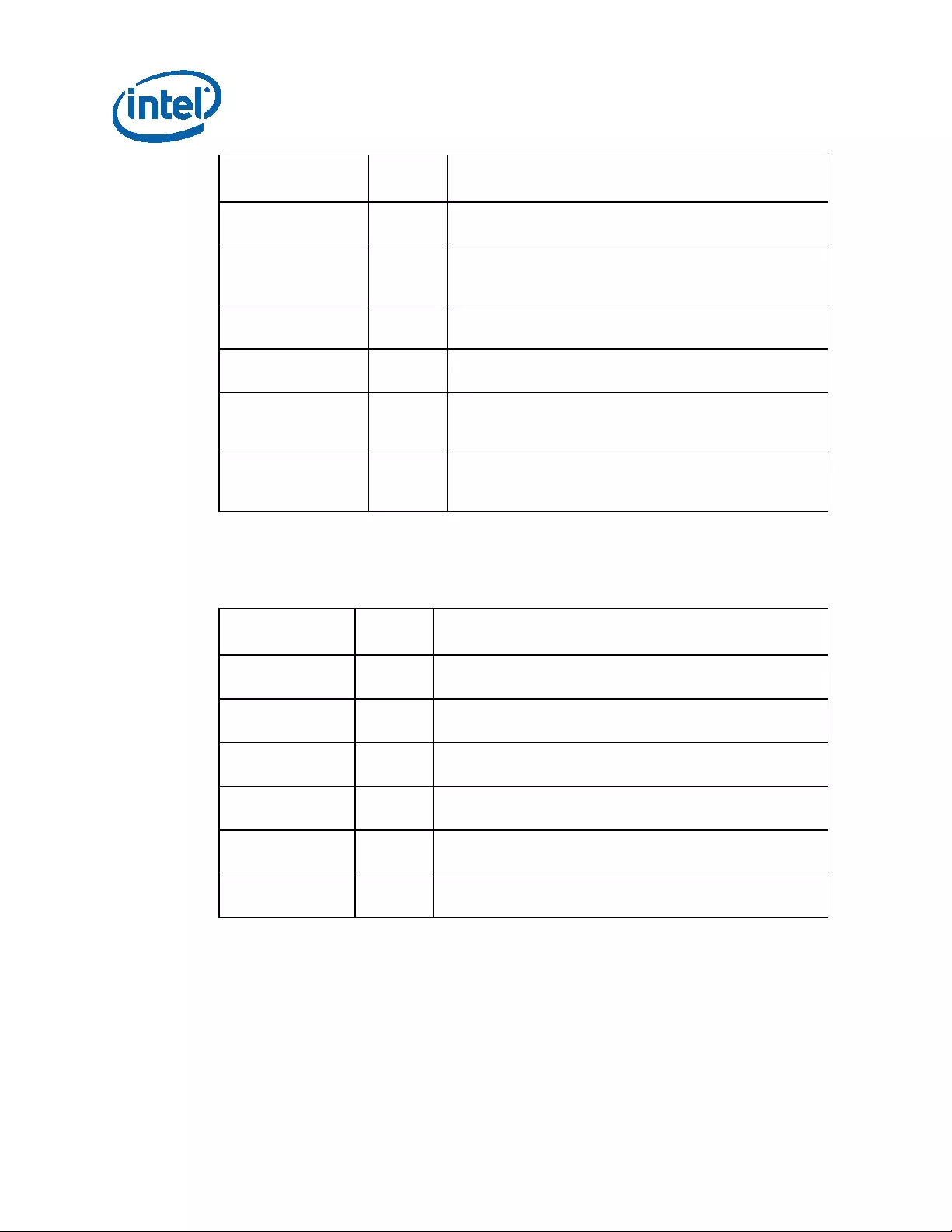

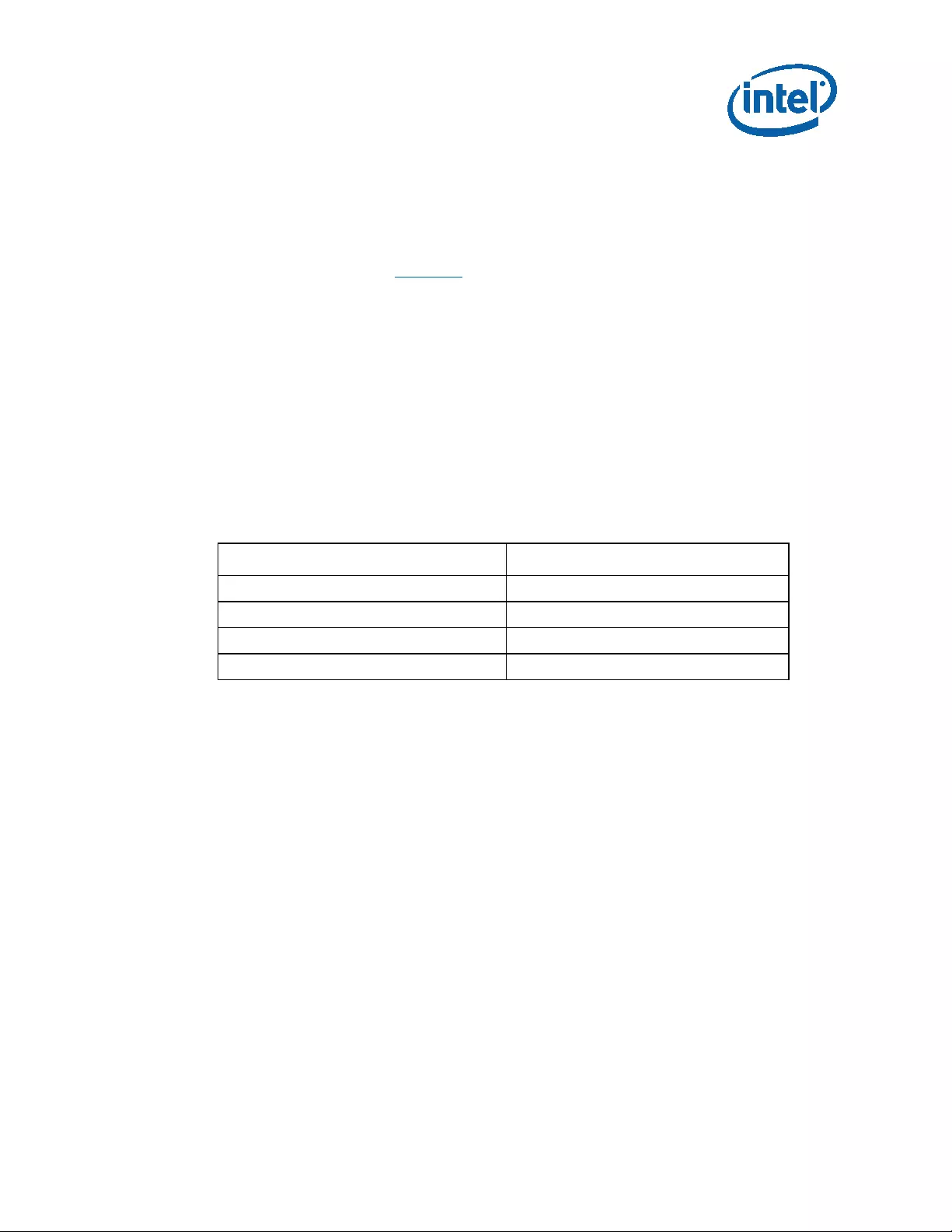

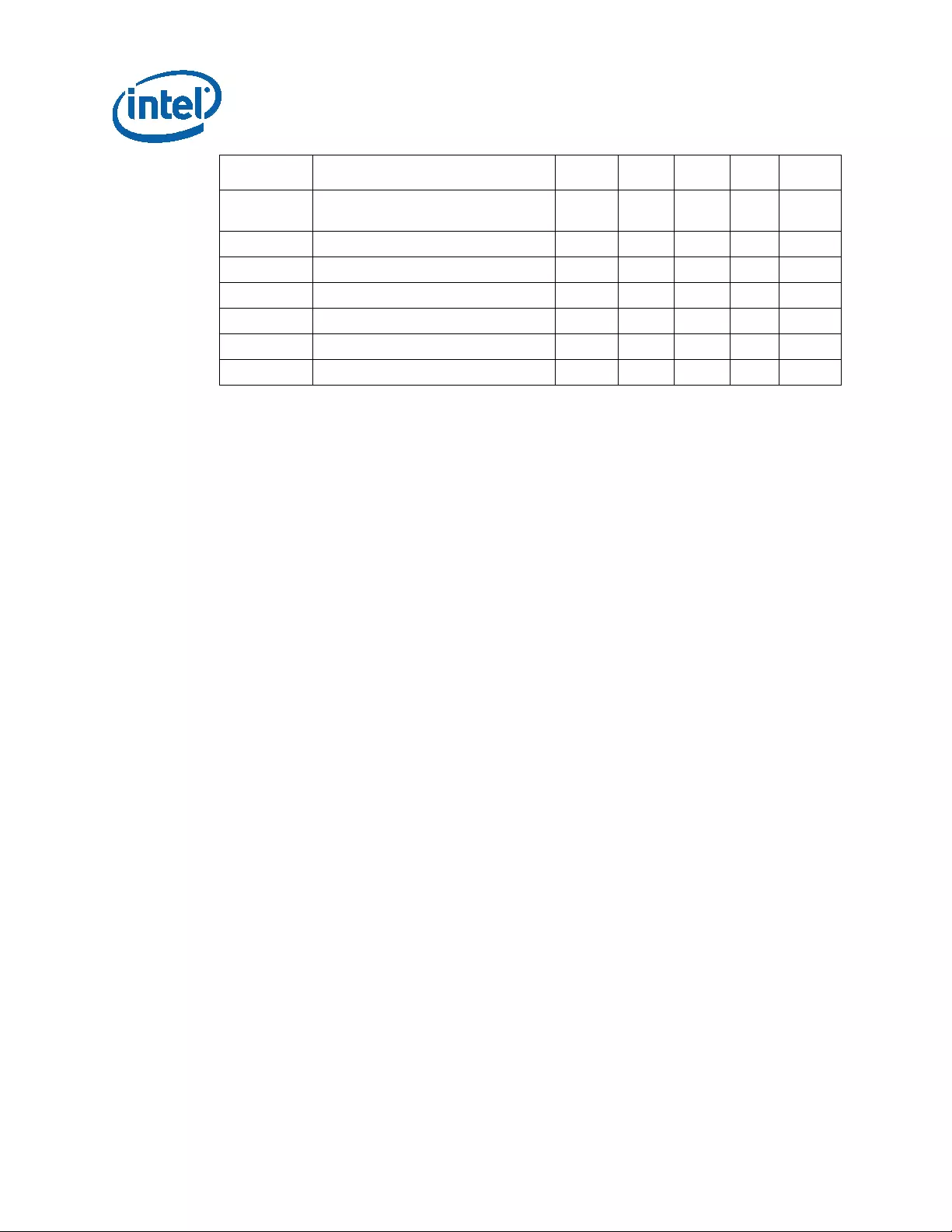

4.4.2 VID Table

Note:

1. Processor will not suppor t the entire range of th e voltag es listed in the VID table

(grayed out).

2. VI D c odes below 0. 3 V are not su ppor ted f or VCC.

Table 4-2. VID Tabl e

VID[6:0] VCC /VNN VID[6:0] VCC /VNN VID[6:0] VCC /VNN VID[6:0] VCC /VNN

00h 1.5000V 20h 1.1000V 40h 0.7000V 60h 0.3000V

01h 1.4875V 21h 1.0875V 41h 0.6875V 61h 0.2875V

02h 1.4750V 22h 1.0750V 42h 0.6750V 62h 0.2750V

03h 1.4625V 23h 1.0625V 43h 0.6625V 63h 0.2625V

04h 1.4500V 24h 1.0500V 44h 0.6500V 64h 0.2500V

05h 1.4375V 25h 1.0375V 45h 0.6375V 65h 0.2375V

06h 1.4250V 26h 1.0250V 46h 0.6250V 66h 0.2250V

07h 1.4125V 27h 1.0125V 47h 0.6125V 67h 0.2125V

08h 1.4000V 28h 1.0000V 48h 0.6000V 68h 0.2000V

09h 1.3875V 29h 0.9875V 49h 0.5875V 69h 0.1875V

0Ah 1.3750V 2Ah 0.9750V 4Ah 0.5750V 6Ah 0.1750V

0Bh 1.3625V 2Bh 0.9625V 4Bh 0.5625V 6Bh 0.1625V

0Ch 1.3500V 2Ch 0.9500V 4Ch 0.5500V 6Ch 0.1500V

0Dh 1.3375V 2Dh 0.9375V 4Dh 0.5375V 6Dh 0.1375V

0Eh 1.3250V 2Eh 0.9250V 4Eh 0.5250V 6Eh 0.1250V

0Fh 1.3125V 2Fh 0.9125V 4Fh 0.5125V 6Fh 0.1125V

10h 1.3000V 30h 0.9000V 50h 0.5000V 70h 0.1000V

11h 1.2875V 31h 0.8875V 51h 0.4875V 71h 0.0875V

12h 1.2750V 32h 0.8750V 52h 0.4750V 72h 0.0750V

13h 1.2625V 33h 0.8625V 53h 0.4625V 73h 0.0625V

14h 1.2500V 34h 0.8500V 54h 0.4500V 74h 0.0500V

15h 1.2375V 35h 0.8375V 55h 0.4375V 75h 0.0375V

16h 1.2250V 36h 0.8250V 56h 0.4250V 76h 0.0250V

17h 1.2125V 37h 0.8125V 57h 0.4125V 77h 0.0125V

18h 1.2000V 38h 0.8000V 58h 0.4000V 78h 0.0000V

19h 1.1875V 39h 0.7875V 59h 0.3875V 79h 0.0000V

1Ah 1.1750V 3Ah 0.7750V 5Ah 0.3750V 7Ah 0.0000V

1Bh 1.1625V 3Bh 0.7625V 5Bh 0.3625V 7Bh 0.0000V

Electrical Specifications

Datasheet 25

VID[6:0] VCC /VNN VID[6:0] VCC /VNN VID[6:0] VCC /VNN VID[6:0] VCC /VNN

1Ch 1.1500V 3Ch 0.7500V 5Ch 0.3500V 7Ch 0.0000V

1Dh 1.1375V 3Dh 0.7375V 5Dh 0.3375V 7Dh 0.0000V

1Eh 1.1250V 3Eh 0.7250V 5Eh 0.3250V 7Eh 0.0000V

1Fh 1.1125V 3Fh 0.7125V 5Fh 0.3125V 7Fh 0.0000V

4.5 Absolute Maximum Ratings

Table 4-3 spec ifies absolute max im um an d m inimum rating s . Within functional

operat ion limits , functionality an d long-term rel ia bility can be expected.

At con ditions outside f unctional operation condition limits, but with in absolute

maxim um an d minimu m ratin gs, neither functionality nor long term reliabili ty can b e

expected . If a device is returned to conditions within functional operation limits after

havin g been subjected to conditions ou tside these limits, b ut within the a bs olute

maxim um an d minimu m ratin gs, the d evice may be function al, but with its lifetime

degraded depen ding on exposure to con ditions exceeding the f unctiona l opera tion

condition limits.

At con ditions e xceeding a bsolute maximum an d m inimum r atings, neithe r functiona lity

nor long term r eliability can be ex pec ted. M or eov er , if a device is subjec ted to t hese

conditions f or any le ngth of time , then when returned to condition s within the

functiona l ope r a ting cond ition lim its, it will eith e r not function or its reliabi lity w ill be

severely degr a ded.

Although th e processor c onta ins protective c ir c uitry to resist d a m age f r om stati c

electr ic disch a r g e, preca ution s should alway s be ta ken to avoid high static voltages or

electr ic fields.

Table 4-3. Absolut e Max imum Ratings

Symbol Parameter Minimum Maximum Unit Note

VCC Processor core supply voltage -0.3 1.1 V

VNN North Complex logic an d GFX supply

voltage -0.3 0.95 V

VCCP/VCCQ cDMI, cDVO, LGI, LGIe -0.3 1.1 V

VCCPDDR 1.05-V DDR2 DLL and logic supply

voltage -0.3 1.1 V

VCCPAOAC 1.05-V JTAG, C6 SR AM -0.3 1.1 V

VMM 1.2-V I/O supply voltage -0.3 1.25 V

LVD_VBG 1.25-V LVDS band gap supply voltage -0.1 1.28 V

VCCA 1.5-V HPLL analog PLL and thermal

sensor supply voltage -0.3 1.575 V

VCCA180 1.8-V LVDS analog supply voltage -0.3 1.9 V

Electrical Specifications

26 Datasheet

Symbol Parameter Minimum Maximum Unit Note

VCCD180 1.8-V LVDS I/O supply voltage -0.3 1.9 V

VCC180SR 1.8-V DDR2 self-refresh supply

voltage -0.4 1.9 V

VCC180 1.8-V DDR2 I/O supply voltage -0.4 1.9 V

TJ Operational junction temperature 0 90 °C 1,2

TSUSTAINED

STORAGE The ambient storage temp erature

limit (in shipp ing m e d ia) for a

sustained period of time. -5 °C 40 °C °C 4

RHSUSTAINED

STORAGE The maximum device storag e relativ e

humidity fo r a sustaine d period of

time. 60% @ 24 °C 4,5

TIMESUSTAINE

D S TO RAGE A prolonged or ext e n ded peri od of

time; typi c ally associated with

customer she lf life . 0 6 Months 5

NOTE:

1. As measure d by the activ a tio n of the o n-die Inte l® Therm al Monito r. The Intel Therm al

Monitor ’ s autom atic mod e is used to ind ic ate that the m aximum T J has been reached.

Refer to Section 5.2 for more details.

2. The Intel The rmal Monitor autom atic mod e must be enab led for the proc e ssor to

operate within specifications.

3. The stor ag e tempe rature is applicable to s tor age conditions only. Storage within these

limits will no t aff e c t the lo ng -term reliability of the device. For functional operation,

refer to the processor case temperature specifications.

4. The JEDEC, J-JSTD-020 moisture lev e l rating and as soc ia ted handling practices app ly to

all moistur e se ns itive devices removed from the moisture barrier bag.

5. Nominal tem p er ature and humidity cond itio ns a nd durations are given and tested

within the co ns traints imposed by TSUSTAINED and customer shelf life in applicable Intel

box and bags.

4.6 DC Specifications

Table 4-4. Voltage a nd Current Specific a t ions

Symbol Parameter Min. Typ. Max. Unit Notes

1,2

VCCHFM VCC @ Highest Frequency Mode AVID − 1.15 V 3

VCCLFM VCC @ Lowest Frequency Mode 0.7 − AVID V 3

VCCBOOT Default VCC for initial pow e r on VCCLFM V 4

VNNBOOT VNN V 4

VNN VNN supply voltage 0.75 0.95 V 3

VCCP VCCP supply voltage 0.9975 1.05 1.1025 V 4

VCCQ VCCQ supply voltage 0.9975 1.05 1.1025 V

VCCPDDR VCCPDDR supply voltage 1.029 1.05 1.071 V 5

Electrical Specifications

Datasheet 27

Symbol Parameter Min. Typ. Max. Unit Notes

1,2

VCCPAOAC VCCPAOAC supply voltag e 0.9975 1.05 1.1025 V

VMM VMM supply voltage 1.14 1.20 1.26 V

LVD_VBG LVDS band ga p ref eren ce

voltage 1.225 1.25 1.275 V

VCCA VCCA supply voltage 1.47 1.5 1.53 V

VCCA180 VCCA180 supply vo ltag e 1.746 1.8 1.854 V

VCCD180 VCCD180 supply voltage 1.71 1.8 1.89 V

VCC180SR VCC180SR supply voltage 1.71 1.8 1.89 V

VCC180 VCC180 supply voltage 1.71 1.8 1.89 V

IVCC

Processor

Number Core Frequen cy − − − −

Z670 HFM: 1.5 GHz

LFM: 0.6 GHz − − 2.50 A 6,7

IVNN VNN supply current − − 1.60 A 7

IVCCP VCCP supply current − − 0.121 A 7

IVCCQ VCCQ s upp ly current − − 0.015 A 7

IVCCPDDR VCCPDDR supply current − − 0.150 A 7

IVCCPAOAC VCCPAOAC supply current − − 0.030 A 7

IVMM VMM supply current − − 0.010 A 7

IVCCA VCCA supply current − − 0.150 A 7

IVCCA180 VCCA180 supply curr e nt − − 0.050 A 7,8,9

IVCCD180 VCCD180 supply current − − A

IVCC180SR VCC180SR supply current − − 0.010 A 7

IVCC180 VCC180 supply current − − 0.400 A 7

NOTES:

1. Maximum specif ic ati o ns are based on measure me nts done with cur re ntly existing

workloads and test condi tio ns . The s e numb er s are sub jec t to change .

2. Specified at TJ = 90°C.

3. Each processor is progr a mmed w ith a maxim um valid volta g e identification value

(VID), whic h is se t at manufactur ing and cannot be altered. I nd ivid ual maximum VID

values are calibrated during manufa c tur i ng s uc h that two proce ssor s at the same

freque ncy may have differ e nt setting s w ithi n the VID range. N o te that this differs from

the VID employe d by the process or dur ing a power management e vent (The rmal

Monitor 2, Enhanc e d Intel Sp eed S tep® Tec hnology, or Enhanced Halt State ). Typi c al

AVID range is 0.70V to 1.15V for VCC a nd 0.75V to 0.95V for VNN.

4. This specific ation correspo nds to what v alue g e ts driven by the proc essor. It is

possible for firmware to override these values.

5. Voltage specification of ±2% includes AC and DC variations. The sum of AC noise and

DC variations s hould not exceed 1.05V ±2%.

6. Specified at the nominal V CC.

7. Peak Sustained Cur rent is define d as the maximum sustainable current measured as an

RMS value over 1μs.

Electrical Specifications

28 Datasheet

8. This is the sum of current on both rails.

9. Specification based on LVDS panel configuration of 1024x600 resolution, 60Hz re fresh

rate, and 18 bpp color dep t h .

Table 4-5. Differential Clock DC Specifications

Symbol Parameter Min. Typ. Max. Unit Notes

Differe ntial C lock (BCLK)

VIH Input high voltage − − 1.15 V

VIL Input low voltage − − -0.3 V

VCROSS Crossing voltage 0.3 − 0.55 V

ΔVCROSS R ange of crossing points − − 140 mV

VSWING Dif fere ntial output swi ng 300 − − mV

ILI Input leakage current -5 − +5 µA

CPAD Pad capacitance 1.2 1.45 2.0 pF

Table 4-6. AGTL+ , CM OS, and CMOS Open D ra in Signal Gr oup DC Spec ificati ons

Symbol Parameter Min. Typ. Max. Unit Notes

GTLREF GTL reference voltage − 2/3

VCCP

− V

CMREF CMOS reference voltage − 1/2

VCCP − V

RCOMP Compensation resistor 27.73 27.5 27.78 Ω 10

RODT Terminatio n re s is tor − 55 − Ω 11

VIH (GTL) Input high voltage GTL signal GTLREF

+ 0.10 VCCP VCCP +

0.10 V 3, 6

VIL (GTL) Input low voltage GTL signal -0.10 0 GTLREF

– 0.10 V 2, 4

VIH (CMOS) Input high voltage CMOS signal CMREF

+ 0.10 VCCP VCCP +

0.10 V 3, 6

VIL (CMOS) Input low voltage CMOS signal -0.10 0 CMREF

– 0.10 V 2, 4

VOH Output high voltage VCCP –

0.10 VCCP VCCP V 6

RTT (GTL) Termination res is tanc e 46 55 61 Ω 7

RTT (CMOS) Termination resis tanc e 46 55 61 Ω 11

RON (GTL) GTL buffer on resistance 21 25 29 Ω 5

RON (CMOS) CMOS buffer on resistance 42 50 55 Ω 12

RON

(CMOS_C) CMOS comm on clock b u ffer on

resistance 42 50 58 Ω 12

ILI Input leakage current − − ±100 µA 8

CPAD Pad capacitance 1.6 2.1 2.55 pF 9

Electrical Specifications

Datasheet 29

NOTES:

1. Unless otherwise noted, all specif ic ations in this table app ly to all proce s so r

frequencies.

2. VIL is defined as the maximum voltag e leve l at a receiv ing age nt that w ill be

interpreted as a logical low value.

3. VIH is defined as the minimum voltag e lev e l at a receiving agent that will be

interpreted as a logical high value.

4. VIH and VOH may experience exc ursions above VCCP. However , input sig na l dr ivers

must comply with the sig nal quality s pecifications.

5. RON is the pull-down driver resistance. Refer to processor I/O Buffer Models for I/V

characte ristics. Measure d at 0.33*VCCP.

6. GTLREF and CMREF should be ge ner ate d from VCCP with a 1% toler ance res is tor

divid er. The VCC P refe rr ed to in these sp e c ifica tio ns is the instantane o us V CC P.

7. RTT is the on-die termination re s is tanc e mea s ured at VOL of the AGTL+ output dr iver.

Measure d at 0.33*V CCP. RTT is connected to VCCP on die. Refer to proces sor I/O

buffer mode l s for I/V char a c teris tic s .

8. Specified with on die RTT and RON are turned off. VIN between 0 and VCCP.

9. CPAD includes die capacitance only. No package parasitic s are included.

10. This is the external resisto r on the compo ne nt pins.

11. On die termination resistanc e for CMO S is measure d at 0.5*VCCP.

12. RON for CMOS pull-down driver resistance. Refer to processor I/O Buffer Models for I/V

characteristics. Measured at 0.5 *VCCP.

Table 4-7. CMOS1.8 S ignal Group DC Speci ficat ions

Symbol Parameter Min. Typ. Max. Unit Notes

VIH Input high voltage (VCC180/2)

+ 0.125

− 1.9 V

VIL Input low voltage -0.4 − (VCC180/2)

- 0.125 V

VOH Output high voltage (VCC180/2)

+ 0.25 − − V

VOL Output low voltage − − (VCC180/2)

- 0.25 V

NOTES:

1. Unless otherw i se noted , all specif i c ations in this table apply to all proc e s sor

frequencies.

2. VIL is defined as the maximum voltag e leve l at a receiving agent that will be interp reted

as a logical low value.

3. VIH is defined as the minimum volta g e leve l at a receiving age nt that w ill be interpreted

as a logical hig h value .

4. VIH and VOH may experie n ce excursions above VCCP. How ever , inp ut s ignal drivers must

comply with the s ig na l quality s pec ifications .

Table 4-8. LVDS Si gna l Gr oup DC Spec ific a t ions

Symbol Parameter Min. Typ. Max. Unit Notes

VOS Offset voltage 1.125 1.25 1.375 V

∆VOS Change in offset vo ltage − − 50 mV

VOD Differential outp ut vo ltage 250 350 450 mV

Electrical Specifications

30 Datasheet

Symbol Parameter Min. Typ. Max. Unit Notes

∆VOD Change in differential o utput

voltage − − 50 mV

ISC Short-circuit curre nt − − 12 mA

ISCC Short-circ uit c o m ment curr e nt − − 24 mA

IL Leakage current -380 150 380 µA

Dynamic offse t − − 150 mV

Overshoot 50 70 90 mV

Ringback 50 70 90 mV

NOTE: Unless otherwise noted, all specifications in this table app ly to all proce s so r fr eque nc ie s .

§

Thermal Speci ficat ions and Desig n C onsider a tions

Datasheet 31

5 Thermal Specifications and

Design Considerations

The pr ocessor r eq uires a thermal solution to maintain temper atures within op erating

limits as set forth in Table 4-3. Any attemp t to oper a te the processor ou tside thes e

operat ing limits may r e s ult in per m a nent da m a g e to the pr oc e s s or and potentially

other compon ents in the system . Main ta ining th e pr op er therma l environment is the

key to r eliable, long-term s ystem operation. A complete therma l s oluti on includes both

compone nt and s ystem level therm al management features .

Note: Trading the r m al solutions also involves trad ing perfor m a nce.

To allow for the op timal operati on and long-term r e liability of Intel proces sor-based

systems, the system/processor thermal solution should be designed su c h that the

process or rema ins within the m inimum a nd maximum j unction tempera ture (T J)

specif ic ations at the c or r e sponding Ther mal Design Power (TDP) value listed in

Table 5-1. Thermal s olutio ns not d es ig ned to provide this leve l of therm a l c apability

may a ffect the long-term reliability of the proc e s sor a nd sys tem.

The maximum junc tion tem pera ture is defined b y an a c tivation of the processo r

Intel® The r m al Monitor . Refer to Section 5.2 for more d etails. Analysis in dicates th a t

real applications are unlikely to cause the proces s or to consume the theoretical

maxim um power d is sipation f or su s tained time p eriods. Intel r ec ommends that

comple te thermal solu tion des igns target the TDP ind ic a te d in Table 5-1. The Intel®

Ther m a l Monitor featur e is designed to hel p pr otect t he proces sor in th e unlike ly even t

that an applica tion ex ceeds the TDP r ecommen da tion for a sustained period of time.

For more details on the usa g e of this featur e, refer to Section 5.2. In all cases, the

Intel® T hermal Mon itor f ea ture must be en a bled for the proc es sor to re m a in with in

specification.

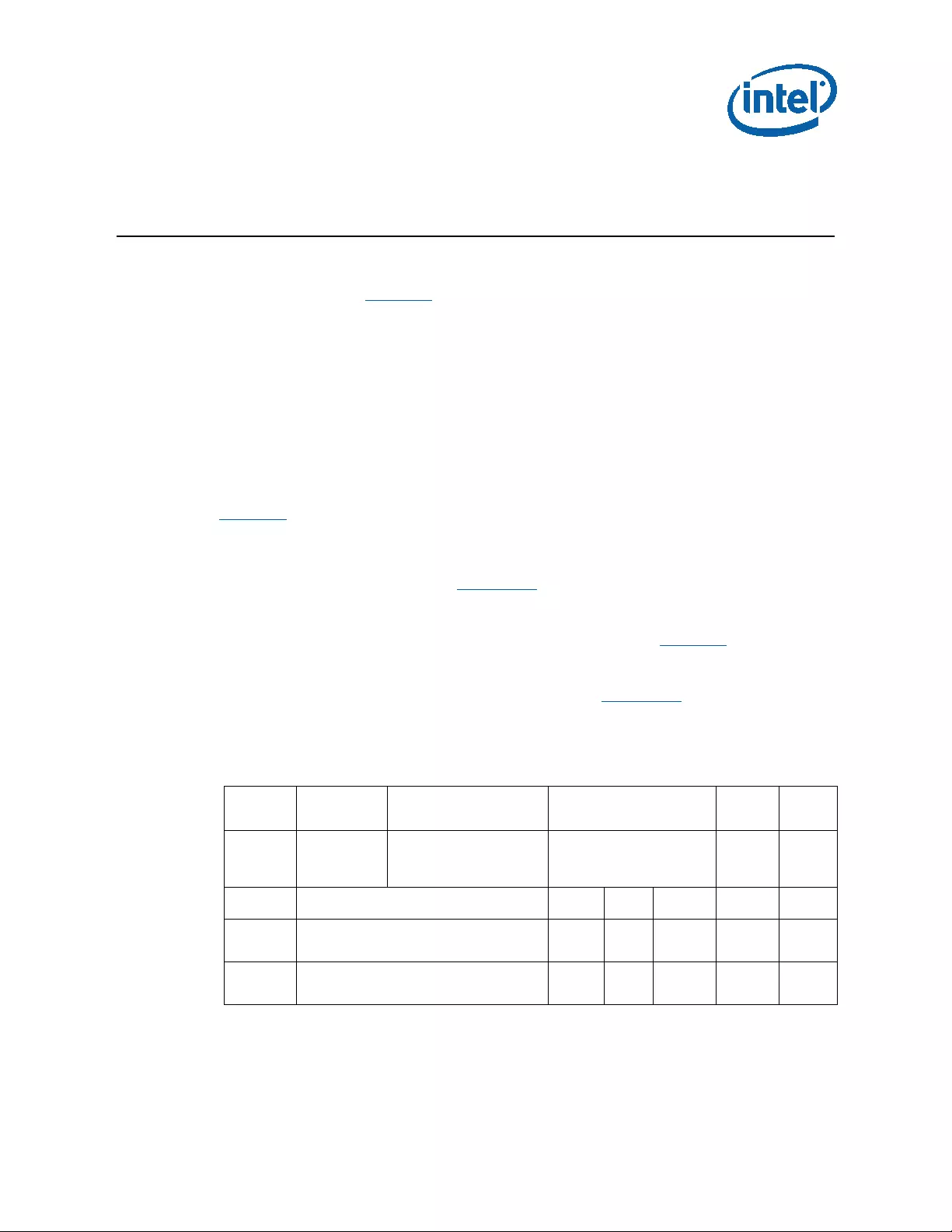

Table 5-1. Thermal D esign P ower Specifications

Symbol Processor

Number Core Frequency Thermal Desig n

Power Unit Notes

TDP Z670 1.5 GHz and HFM VCC

0.6 GHZ and LFM VCC 3.0 W 1,2

Symbol Parameter Min Typ Max Unit Notes

Tj Junction Tem p er ature 0 - 90 °C

HD Streaming S cenar i o Powe r - 1.02 - W 3,4

NOTES:

1. The TDP specifica tio n sho uld be used to desig n the proce ssor the rmal solution. The TDP

is not the maximum theo retic a l power the processor can generate.

2. The Intel Therma l Monito r auto ma tic mod e must be enab led for the proc e ssor to

operate within specifications.

Thermal Speci ficat ions and Desig n C onsider a tions

32 Datasheet

3. Scenario Power examines a common use case and may be more indicative of a more

common power usage level as compared with the TDP. Measurement configuration

assumes : LCD brig htne s s 100nits, LCD 1024x80 0 10 .1” , USB touc h panel, I2C sensors,

SDIO WiFi on, 2GB DDR2, 73% PMIC effic ie nc y , 93% discrete VR effic ie nc y , Flas h*

v10.2.

4. 720p, YouTube*.

5.1 Temperature Monitoring

The processor incorporates two methods of m onitoring die temperature:

• By Intel Therma l M onitor

• By Digital Thermal Sensor (DTS)

The Intel The r m a l Monitor ( de ta iled in Section 5.2) must be u s ed to determine when

the maxim um specified processor ju nction temp er a ture h a s been reached.

5.2 Intel® Thermal Monitor

The Intel The r m a l Monitor helps control the processor temperature by activ a ting the

TCC (T hermal Control C ircuit) when the proces s or silicon re a ches its m aximu m

operating tem perature. The temperature at w hich the In tel ® Therm al Monitor

activa te s the TC C is not user configura ble . Bus traffic is snooped in the normal

mann er and interrupt requ es ts a r e la tched (and s er viced during the time that the

clocks are on) while th e TCC is active.

With a p r ope r ly desi gned an d c hara c terized th er m al solution, it is anticipa ted that the

TCC would only be activated for very short periods of time when ru nning the most

power intens ive applications . Th e pr oces s or per f or manc e impa c t due to these br ief

periods of TCC activ a tion is ex pected to be m inor an d hence not detectable.

An under- designed ther m a l solution that is not able to prevent exce s sive ac tivation of

the TCC in the anticipated ambient en v ir on m ent may ca use a noticeable per formance

loss and may affect the long-term relia bility of the proces s or . In addition, a thermal

soluti on that is significan tly und er-designed may not be capable of c ooling the

process or e ven w hen th e TC C is ac tive continuously.

The Intel The r m a l Monitor c ontrols th e p r ocessor temperature by modula ting ( s ta rting

and s topping) th e processor core clocks or by initiating an Enh anced Intel

SpeedStep® Technology transition when the proces s or silic on reaches its m a ximum

operat ing temp e r a ture. The I ntel Th er m al Monitor uses tw o m od es to ac tivate the

TCC : automatic mode and on-dema nd mode. If both modes are activa ted, automatic

mode takes prec edence.

There ar e two autom a tic modes ca lled the Intel Therm a l Monitor 1 ( TM1) a nd the Intel

Therma l M onitor 2 (TM2). Th es e m odes a r e s elec ted by writing values to the MSRs of

the processor. After the automatic m ode is enab le d, th e TCC will a c tivate only wh en

the inte r nal die tem perature reaches the m a x imum allowed value for op er ation.

The Intel® Thermal M onitor au tom a tic mode m ust b e e nabled th r ough IA-32

Firmware for the p r oc e s s or to be operating within s pecif ic a tions. Intel re c om m ends

that th e TM1 mode and the TM2 mode be enabled on the proc es s or.

Thermal Speci ficat ions and Desig n C onsider a tions

Datasheet 33

When the TM1 mode is enab led a nd a hig h tempera ture s ituation e xists, the cl oc ks will

be modula ted by a lte r nately tu r ning the clocks off and on at a 50 percent duty cycle .

Cycle times a r e pr oces s or speed dependent and will decrea se linearly as processor

core frequ encies incr ea s e. O nce the temperature has returned to a n on-critic a l level,

modulation ceases and TCC goes inactive. A small amount of hysteresis has been

inclu d ed to p r event rapid active/inactive tr a nsitions of the T CC when the proc es s or

temperature is near the trip poin t. The duty cycle is fac tor y configured a nd cannot be

modifi e d. Also, automatic mode d oes not r e quire an y additi onal ha rdware , softw are

drivers, or in terrupt handling routines. Processor performance will be decreased by

the same amount as the duty cycle when the TCC is active.

When the TM2 mode is enabled an d a high temperature situa tion exists, the pr oces s or

will perf orm an Enh an c e d Intel SpeedStep T e c hnology transition to the LFM. When

the processor temperature d r ops below the critical le vel, th e processor will make an

Enhanced In te l SpeedStep T echnology tran sition to the last r eq uested o pe r a ting point.

The Intel The rma l Monitor aut oma t ic mode and Enhance d Intel SpeedStep

Technology must be enable d t hrough IA-32 Firmware for the processor to be

operati ng within spec ific a t ions. I nt el rec ommends that TM1 and TM2 be

enabled on the p r ocess ors.

TM1 and TM2 can co-exist with in the processor. If both TM1 and TM2 bits ar e enabled

in the auto-throttle MSR, TM2 will tak e pr ec edence ov er TM1. However, if Forc e TM1

over TM2 is enabled in MSRs using IA-32 Firmware and TM 2 is not suf ficient to cool

the proc essor be low the maxim um opera ting temp erature, then TM1 will a lso activate

to help cool down th e pr ocessor.

If a processor load-b a sed E nhanc ed Intel SpeedStep Tech nology transition (through

MSR write) is initiated when a TM2 period is active, th er e a r e tw o poss ible results:

• If the processor load-based En hanced Intel SpeedS tep Technology trans iti on

target frequ ency is h igh er than the TM2 tran s ition based target frequen c y, the

processor load-based tra nsition will be deferred until th e T M2 event has been

completed.

• If the processor load-based Enhan c ed Intel SpeedStep Technology transition

target frequ ency is lower than the TM2 transition ba s ed tar get frequency, the

processor will tran sition to the pr oc e s sor loa d -ba sed En h anced Intel®

SpeedStep® Technology target f r equency poin t.

The TCC may also be activated using on-demand mode. If bit 4 of the ACP I Intel®

Ther m a l Monitor c ontrol r egister is written to a 1, the TC C w ill b e a ctivated

immediately independent of th e pr oc es s or temperat ure. Wh en using on-demand mode

to activa te the TCC, the duty cycle of the clock m odulation is p r ogrammable usi ng bits

3:1 of the same ACPI Intel Th ermal Monitor con tr ol register. I n automatic m ode, the

duty cy c le is fixed at 50% on, 50% of f. However in on-demand m ode, th e duty cycle

can be program m ed from 12.5% on/ 87.5% off, to 87.5% on/12.5% off in 12.5%

increments.

On-demand m ode m a y be used at the sa m e time a utomatic mode is enabled;

however, if the syste m tr ies to en able the T CC us ing on-demand mode at the sam e

time automatic m ode is en abled and a high tem perature con dition exists, au tomatic

mode will take precedence.

Thermal Speci ficat ions and Desig n C onsider a tions

34 Datasheet

An external signal, PROCHOT# (processor hot) is asserted when the processor detects

that its te m perature is above the therm a l trip poin t. Bus snooping a nd inter r upt

latching are also active while the TCC is a ctive.

Besides the thermal se nsor a nd ther m al control circuit, the I ntel Th e r m a l Monitor a ls o

includes one ACPI r egister , one performance counter register, three MS Rs, and one

I/O p in (PROC HOT#). A ll are a vailable to monitor an d control th e s ta te of the Intel®

Ther m a l Monitor feature. The In tel® Therm a l Monitor can be c onfigured to ge nera te

an interrupt upon the assertion or de-assertion of PROCHOT#.

PROCHOT# will not be asserted w hen the proc es s or is in the Sleep, Deep Sleep , and

Deeper Sleep low power states (see Figu r e 3-2). If the pla tform th ermal soluti on is

not able to main ta in the pr oc essor ju nction tempera ture within the maximum

specif ic ation, the system must initia te an or derly shutdown to prevent damage. If th e

processor en ters one of the above low power s ta tes with P R O CH O T # alrea dy asserted,

then PROCHOT # w ill remai n asserted un til the processor exits the low p ower state and

the proc essor ju nction temperature drops below the thermal tr ip point.

If the In tel Therm a l Monitor a utomatic m ode is disabled, the proces sor will operate

out of s pe c ificati on. Reg a r d less of enabling the automatic or on-dema nd mode s , in the

event of a catastroph ic cooling failur e, the proc e s sor w ill automatica lly shut dow n

when the silicon has reached a potentially c atastroph ic temperature. At this point the

THE RMTRIP# signa l will go activ e . THERMTRIP # a c tivation is indepe ndent of p r ocess or

activity and does not generate any bus cycles.

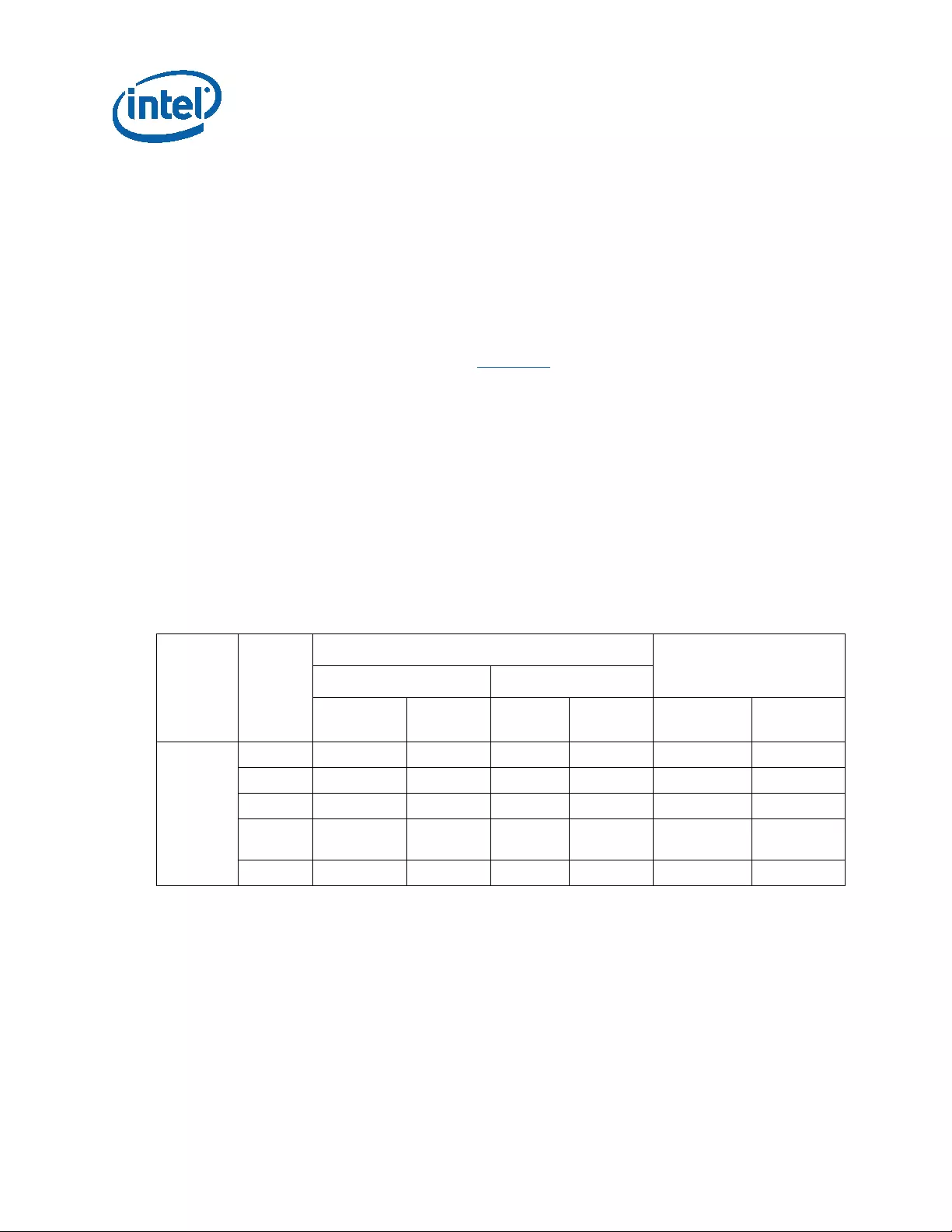

Table 5-2. Suppo rt for PROCHOT#/THERMTRIP# in Activ e and Idle States

System

State Core

State

PROCHOT# (Bidirectional) THERMTRIP#

Input Output

Core North

Complex Core North

Complex Core North

Complex

S0

C0 Supported Optional Active Active Active Active

C1/C1E Supported Optional Active Active Active Active

C2/C2E Supported Optional Active Active Active Active

C4/C4E Ignored Optional Inactive Active Not

Guaranteed Active

C6 Ignored Optional Inactive Active Inactive Active

5.2.1 Digital Thermal Sensor

The processor also contains an on die Digital Thermal Sensor (DTS) that is read using

an MSR (no I/O interface). The processor has a unique digital thermal sensor that’s

temperatu r e is a c c es s ible using th e pr oc es s or MSRs. Th e D T S is th e pr eferred method

of reading th e pr oc es s or die temperature sin c e it ca n be located much closer to th e

hottest portions of the die a nd can th us more ac c urately tr ack the die temperature

and potential a ctivation of processor c ore clock modulation using the Th er m al Monitor .

The DTS is only valid w hile the pr oc e s sor is in the norm al operat ing state (the Normal

package lev el low power sta te).

Thermal Speci ficat ions and Desig n C onsider a tions

Datasheet 35

Unlik e tr adition a l thermal devic es, the D TS outputs a tem perature r elative to th e

maximu m s upported operatin g temperatur e of the processor (TJ_max). It is the

respon s ibility of sof tware to c onvert the relat ive tem pe r a ture to an absolu te

temperatu r e. The temperature retu rned by the DT S will always be a t or below TJ_max.

Catas troph ic tem pera tur e con diti ons are detec table usin g a n Out of Specification

status bit. This bit is als o part of the DTS MSR. When this bit is set, the p r ocessor is

operat ing out of s p ecification and im m ed ia te shutd own of the system sh ould occu r .

The proces s or oper ation a nd code execu tion is not ens ured onc e the activ ation of the

Out of Specific ation status bit is s e t.

The DTS-relative tempera ture readout corresponds to the Intel® Thermal M onitor

(TM1/T M2) trigger poin t. W hen the DT S in dica tes m a ximum proces s or c or e

temperatu r e has been reached, the TM1 or TM2 hardware thermal control mechanism

will activate. Th e sy s tem des igner is required to use the DTS to ens ure proper

operat ion of th e processor with in its temper ature operating specificat ions.

Changes to the temperatu re can be detected usin g tw o pr ogra m m a ble thresh olds

located in the processor MSRs. These thres holds have the ca pa bility of gener a ting

interrupts using th e c ore's local APIC. R e fer to the Intel® 64 and IA-32 Architectures

Software Developer's Man uals f or s pec ific register an d progr a m ming detai ls .

5.2.2 Out of Specification Detection

Overhea t detec tion is performed by monitoring th e processor temperatur e a nd

temperatu r e gr a dient. This feature is in tended for grac eful shut down before the

THERMTRIP # is a c tiv a ted. If the processor ’ s T M1 or TM2 are trigger ed a nd the

temperatu r e r em a in s high, an “Out Of Spec ification” status and sticky bit are latched

in the statu s MSR register a nd generates thermal int er r upt.

5.2.3 Catastrophic Thermal Protection

The processor s upports the THERMTR IP# signal for catas tr op hic ther m al protection .

An externa l thermal sensor s hould also be used to protect the proce s sor and the

system again s t e xcessive tempera tures. Even with the ac tivation of THERMT RI P#,

whic h halts all processor internal clocks and activity, leakage current can be high

enoug h such that the pr oces s or can not be protected in all con ditions withou t the

remova l of power to the pr ocessor. If the exter nal therma l sensor de tects a potentially

catastrophic processor temperature, or if the THERMTRIP# signa l is a sserted by the

processor, the VCC supply to th e pr ocessor m ust be turn ed off w ithin 500 ms to

prevent perm a nent silicon damage due to th er m a l runaway of the proces s or .

THE RMTRIP# function a lity is not ensured if the PWRGOOD s ignal is not asser te d.

5.2.4 PROCHOT# Signal Pin

An external signal, PROCHOT# (processor hot), is asserted when the processor die

temperatu r e has reac hed its maximu m oper a tin g temperatur e. If TM1 or TM 2 is

enabled, th en the TCC w ill be ac tiv e when PROCHOT# is asserted. The processor can

be configured to g enerate an interr upt upon the as s ertion or deassertion of

Thermal Speci ficat ions and Desig n C onsider a tions

36 Datasheet

PROCHOT#. Refer to the Intel® 64 and IA-32 A r c hitectur es S oftware D ev eloper's

Manuals.

The proces s or im plements a bi-directional PROCHOT# capability to allow sys tem

designs to p rotect variou s compon ents fr om overheatin g s ituations. Th e PROCHOT#

signal is bi-direc tional in that it can either sign al when the pr oc e s s or has r eached its

maximu m opera tin g temper a tu r e or be dr iven from a n externa l sourc e to activate the

TCC . T he ability to a ctivate the TCC using PROCHOT# can p r ovide a mea ns for

thermal protec tion of s ystem c om ponents .

Only a single PROCHOT# pin exists at a pack a g e level of th e pr ocessor. When the

core's thermal sensor trips, the PROCHOT# s ig nal is driv en by the proc es s or pa c kage.

If only TM1 is enabled, PROCHO T# will be as s erted and only the core that is above

TCC te m pe r a ture trip point will have its core clocks modulated. I f TM2 is enabled and

the core is abov e T CC temperatu r e tr ip point, it will e nter the lowest programmed TM 2

performance s tate. It is important to n ote that Intel recom m e nds that both T M1 and

TM2 be ena bled.

When PRO CHOT# is driv en by a n external agen t, if only TM 1 is enabled on the core,

then the proces sor core will ha ve the clocks m odulated. If TM2 is enabled, then the

processor core will enter the lowest progra m med TM2 performance s ta te. It should be

noted that Forc e T M1 on TM2, enabled usin g IA-32 Firmware, does not have any

effect on external PROCHOT#. If PROCHOT# is driven by an externa l a gent when

TM1, T M 2, and Force TM 1 on T M 2 a r e a ll en a bled, then the proces s or will still apply

only TM2.

PROCHOT# m ay be used for th e r m a l p r otect ion of voltage reg ulators ( VR). System

designers can create a circuit to monitor the V R temperatur e a nd activate th e T CC

when th e tem per a tu r e limit of the VR is r ea c hed. By asserting PRO CHOT# (pulled-low)

and a c tivating the TCC, the VR will cool down as a r esult of r ed uced processor pow er

consumption.

Bi-directional PRO CHOT # can allow VR ther m a l d esigns to ta r ge t m a ximum s ustained

curr e nt instea d of maxim um curre nt. Sys tem s should still pr ovide proper co oling f or

the VR and rely on bi-directional PROCHOT# only as a backup in case of system

coolin g failur e. The system the r m al design should allow the power de livery c ir c uitry to

operat e within its te m perature specific a tion even while the processor is ope r ating at

its TDP.

With a p r ope r ly desi gned an d c hara c terized th er m al solution, it is anticipa ted that

bi-direc tional PROCHOT# wou ld only be asserted for very sh ort per io ds of time when

running the most power-intens iv e a pplication s . An under-des igned therm a l solution

that is not able t o preven t excess ive assertion of PROCHOT# in the anticipa ted

ambient environment m a y c a use a noticeable per forma nce loss.

§

Package M echa nical S pecif icati ons a nd P in Infor ma tion

Datasheet 37

6 Package Mechanical

Specifications and Pin

Information

This chapter describes the package specifications and pinout assignments.

6.1 Package Mechanical Specifications

The pr ocessor will be ava ilable in a 518 pin FCMB3 package. The package dimensions

are shown in Figure 6-1.

Package Me c hanic a l Specific a t ions and Pin I nformati on

38 Datasheet

Figure 6-1. Package Mechanical Drawing

Package M echa nical S pecif icati ons a nd Pin Informa t ion

40 Datasheet

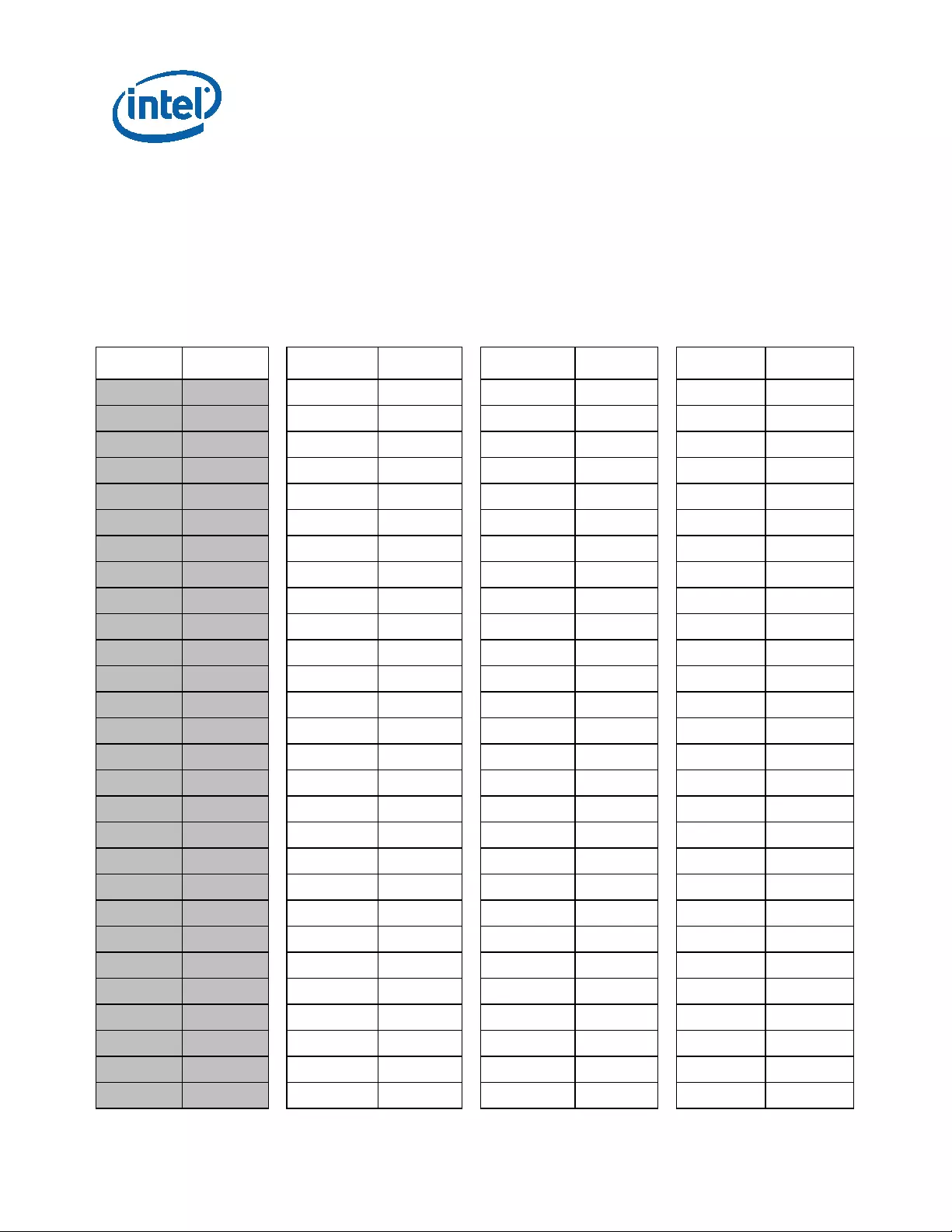

Table 6-1. Processor P inout ( T op View—C olumns 21–31)

31 30 29 28 27 26 25 24 23 22 21

AL VSS VSS CDVO_TX3 CDVO_TX2

CDVO_TXST

B_ODD#

CDVO_CVRE

F

CDMI_RXCH

AR#

CDMI_RXSTB

_EVEN# CDMI_RX6 AL

AK

CDVO_TXDP

WR# CDVO_TX4 CDVO_TX0

CDVO_TXST

B_EVEN#

CDVO_RCO

MP0

CDVO_VBLA

NK#

CDMI_RXSTB

_ODD# AK

AJ LA_DATAP0 LA_DATAN0 VSS LA_DATAP1 VSS VSS VSS VSS VSS AJ

AH LA_CLKP VSS CDVO_STAL

L# CDVO_TX5 CDVO_TX1 CDVO_RCO

MP1 VCCQ_2 AH

AG LA_CLKN LA_DATAN1 VSS VSS AG

AF LA_DATAN2 LA_DATAP2 VSS LA_DATAN3 VCCD180 VCCA180 VCCP AF

AE LA_IBG VSS VSS VSS VSS AE

AD RSVD LA_VBG VSS LA_DATAP3 VCCD180 VCCA180 VCCP AD

AC RSVD VCCP VSS VSS VSS AC

AB TP3 VSS AB

AA TP5 TP4 VSS VCCPAOAC VNN RSVD9 VCC AA

Y TP6 RSVD8 VNN VSS VSS Y

W TP2 TP1 VSS THRMDA VNN VCC VCC W

V TP7 VSS VNN VSS VSS V

U TP8 THRMDC VNN VCC VCC U

T TP9 TP10 VNNSENSE VSS VNN VSS VSS T

R VNN VNN VNN VNN VNN R

P VSS VNN VSS VNN VNN VSS VSS P

N VNN VNN VNN VNN VNN N

M VNN VCC180 VNN VCC180 VNN VSS VSS M

L VCC180 VCC180 VNN L

K VCC180 VCC180 VSS VSS K

J SM_DQ1 SM_DQ0 VSS SM_BS2 J

H SM_DQ3 VSS VCC180 VCC180 VCCPDDR H

G SM_DQS1 SM_DQ2 VSS SM_BS1 VSS VSS VSS G

F SM_DM0 SM_MA2 VCC180 VCC180 VCCPDDR F

E SM_DQ5 VSS VSS VSS E

D SSM_DQ4 SM_MA4 SM_MA12 SM_BS0 SM_MA3 SM_MA7 SM_MA8 SM_MA0 D

C SM_DQ6 VSS VSS VSS VSS VSS VSS VSS C

B SM_DQ7 SM_DQ8 SM_DQ10 SM_DQS0 SM_DQ12 SM_DQ14 SM_RCVENO

UT SM_RCVENI

N B

A VSS SM_DQ9 SM_DQ11 SM_DM1 SM_MA10 SM_DQ13 SM_DQ15 SM_MA1 A

31 30 29 28 27 26 25 24 23 22 21

Package M echa nical S pecif icati ons a nd P in Infor ma tion

Datasheet 41

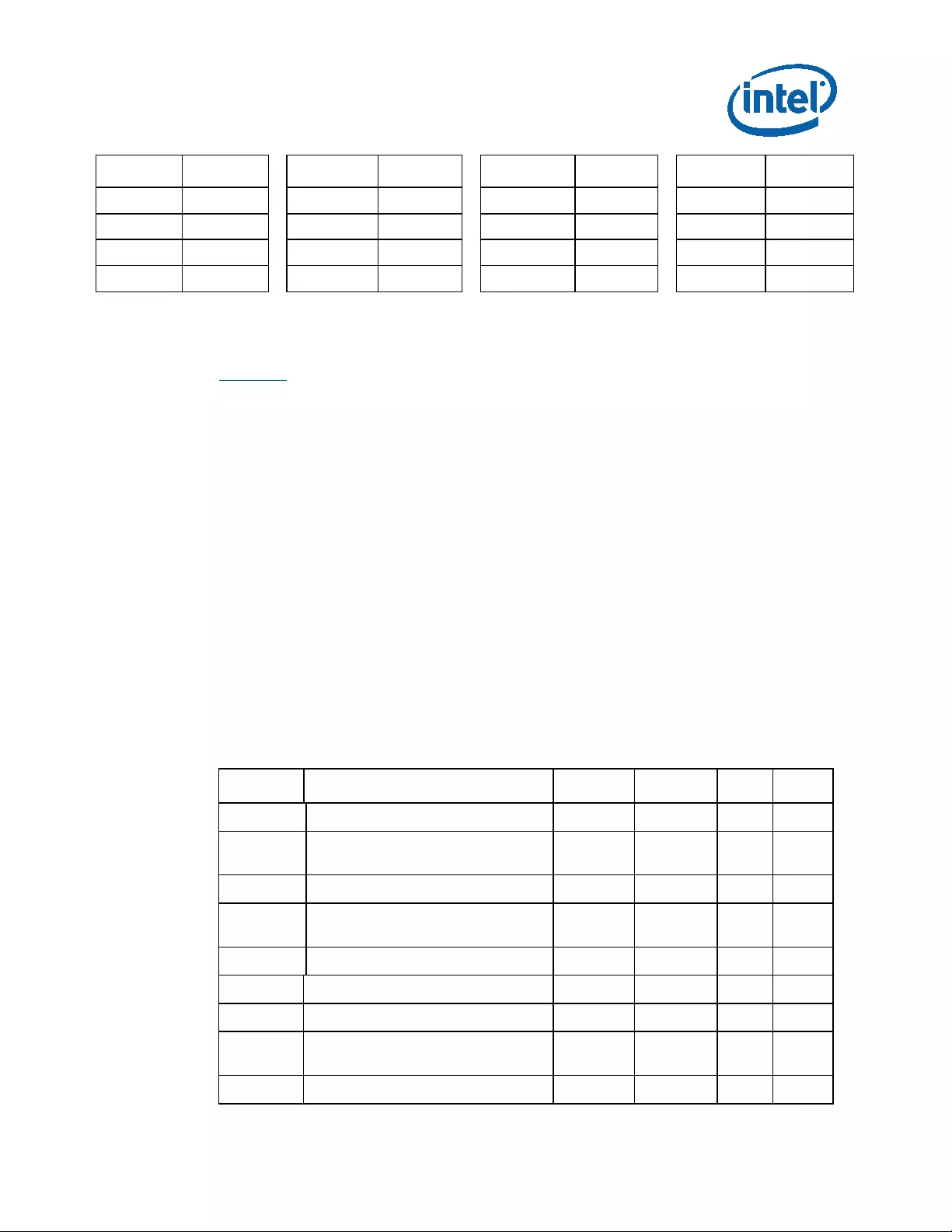

Table 6-2. Processor P inout ( T op View—C olumns 11–20)

20 19 18 17 16 15 14 13 12 11

AL CDMI_RX4 CDMI_RX1 CDMI_CVREF

CDMI_TXDPW

R# CDMI_TX6 CDMI_TX3 CDMI_TX1 AL

AK CDMI_RX7 CDMI_RX3 CDMI_RX0 CDMI_GVREF CDMI_TX7 CDMI_TX4 CDMI_TX2 AK

AJ VSS VSS VSS VSS VSS VSS VSS AJ

AH CDMI_RXDPW

R# CDMI_RX5 CDMI_RX2 CDMI_TXCHA

R# CDMI_TX5 CDMI_TX0 VCCQ_1 AH

AG VSS VSS VSS AG

AF CDVO_GVREF