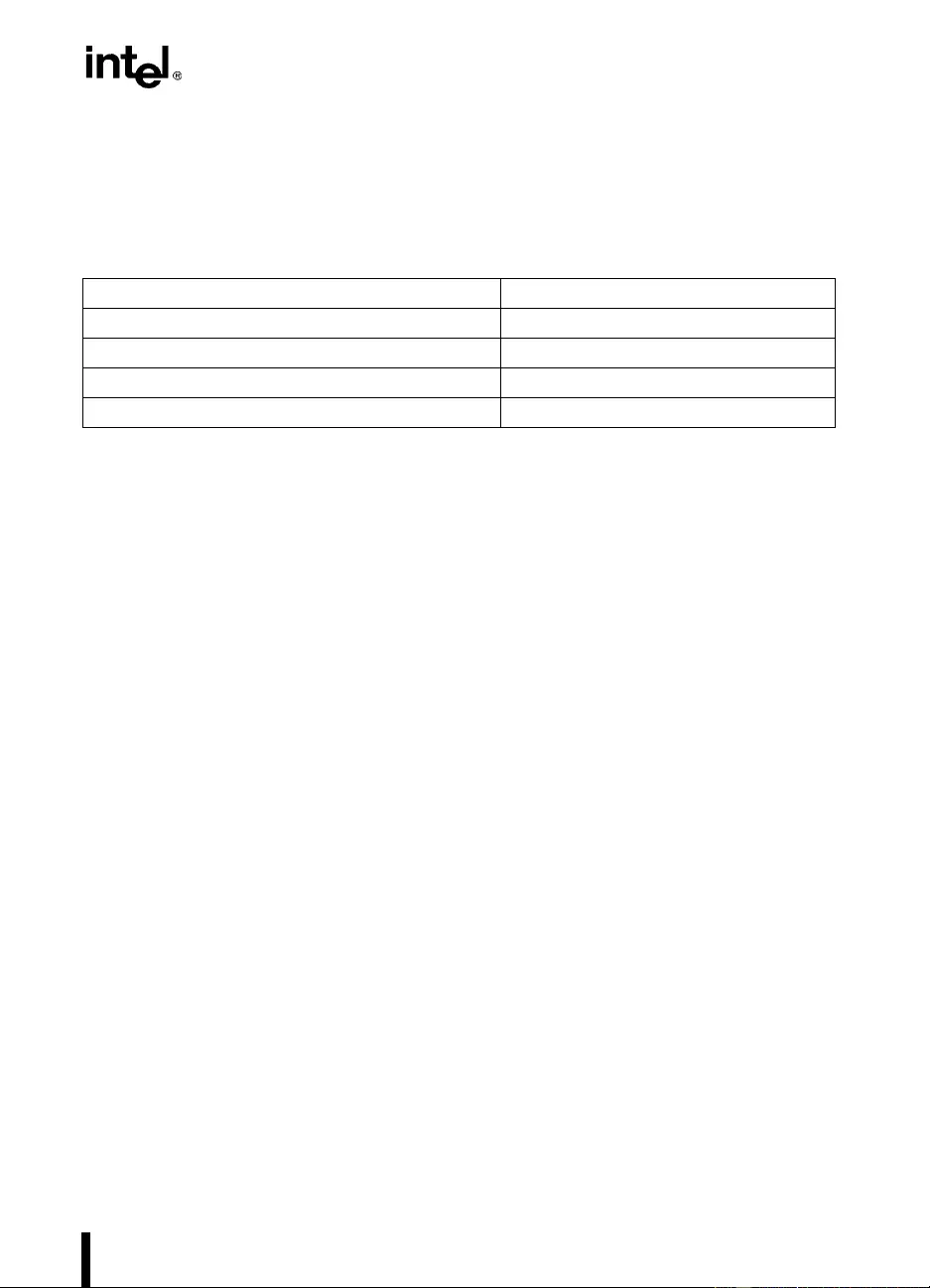

Table of Contents

- LITERATURE

- Intel Application Support Services

- Pentium ® Pro Family Developer’s Manual Volume 1: Specifications

- 1. Component Introduction

- 2. Pentium ® Pro Processor Architecture Overview

- 3. Bus Overview

- 4. Bus Protocol

- 4.1. ARBITRATION PHASE

- 4.1.1. Protocol Overview

- 4.1.2. Bus Signals

- 4.1.3. Internal Bus States

- 4.1.4. Arbitration Protocol Description

- 4.1.4.1. SYMMETRIC ARBITRATION OF A SINGLE AGENT AFTER RESET#

- 4.1.4.2. SIGNAL DEASSERTION AFTER BUS RESET

- 4.1.4.3. DELAY OF TRANSACTION GENERATION AFTER RESET

- 4.1.4.4. SYMMETRIC ARBITRATION WITH NO LOCK#

- 4.1.4.5. SYMMETRIC BUS ARBITRATION WITH NO TRANSACTION GENERATION

- 4.1.4.6. BUS EXCHANGE AMONG SYMMETRIC AND PRIORITY AGENTS WITH NO LOCK#

- 4.1.4.7. SYMMETRIC AND PRIORITY BUS EXCHANGE DURING LOCK#

- 4.1.4.8. BNR# SAMPLING

- 4.1.5. Symmetric Agent Arbitration Protocol Rules

- 4.1.6. Priority Agent Arbitration Protocol Rules

- 4.1.7. Bus Lock Protocol Rules

- 4.2. REQUEST PHASE

- 4.3. ERROR PHASE

- 4.4. SNOOP PHASE

- 4.5. RESPONSE PHASE

- 4.6. DATA PHASE

- 4.6.1. Data Phase Overview

- 4.6.2. Data Phase Protocol Description

- 4.6.2.1. SIMPLE WRITE TRANSFER

- 4.6.2.2. SIMPLE READ TRANSACTION

- 4.6.2.3. IMPLICIT WRITEBACK

- 4.6.2.4. FULL SPEED READ PARTIAL TRANSACTIONS

- 4.6.2.5. RELAXED DBSY# DEASSERTION

- 4.6.2.6. FULL SPEED READ LINE TRANSFERS (SAME AGENT)

- 4.6.2.7. FULL SPEED WRITE PARTIAL TRANSACTIONS

- 4.6.2.8. FULL SPEED WRITE LINE TRANSACTIONS (SAME AGENTS)

- 4.6.3. Data Phase Protocol Rules

- 4.1. ARBITRATION PHASE

- 5. Bus Transactions and Operations

- 5.1. BUS TRANSACTIONS SUPPORTED

- 5.2. BUS TRANSACTION DESCRIPTION

- 5.2.1. Memory Transactions (see Table A-9)

- 5.2.2. I/O Transactions

- 5.2.3. Non-memory Central Transactions

- 5.2.4. Deferred Reply Transaction

- 5.2.5. Reserved Transactions

- 5.3. BUS OPERATIONS

- 6. Range Registers

- 7. Cache Protocol

- 8. Data Integrity

- 9. Configuration

- 9.1. DESCRIPTION

- 9.1.1. Output Tristate

- 9.1.2. Built-in Self Test

- 9.1.3. Data Bus Error Checking Policy

- 9.1.4. Response Signal Parity Error Checking Policy

- 9.1.5. AERR# Driving Policy

- 9.1.6. AERR# Observation Policy

- 9.1.7. BERR# Driving Policy for Initiator Bus Errors

- 9.1.8. BERR# Driving Policy for Target Bus Errors

- 9.1.9. Bus Error Driving Policy for Initiator Internal Errors

- 9.1.10. BERR# Observation Policy

- 9.1.11. BINIT# Driving Policy

- 9.1.12. BINIT# Observation Policy

- 9.1.13. In-order Queue Pipelining

- 9.1.14. Power-on Reset Vector

- 9.1.15. FRC Mode Enable

- 9.1.16. APIC Mode

- 9.1.17. APIC Cluster ID

- 9.1.18. Symmetric Agent Arbitration ID

- 9.1.19. Low Power Standby Enable

- 9.2. CLOCK FREQUENCIES AND RATIOS

- 9.3. SOFTWARE-PROGRAMMABLE OPTIONS

- 9.1. DESCRIPTION

- 10. Pentium ® Pro Processor Test Access Port (TAP)

- 11. Electrical Specifications

- 11.1. THE PENTIUM ® PRO PROCESSOR BUS AND V REF

- 11.2. POWER MANAGEMENT: STOP GRANT AND AUTO HALT

- 11.3. POWER AND GROUND PINS

- 11.4. DECOUPLING RECOMMENDATIONS

- 11.5. BCLK CLOCK INPUT GUIDELINES

- 11.6. VOLTAGE IDENTIFICATION

- 11.7. JTAG CONNECTION

- 11.8. SIGNAL GROUPS

- 11.9. PWRGOOD

- 11.10. THERMTRIP#

- 11.11. UNUSED PINS

- 11.12. MAXIMUM RATINGS

- 11.13. D.C. SPECIFICATIONS

- 11.14. GTL+ BUS SPECIFICATIONS

- 11.15. A.C. SPECIFICATIONS

- 11.16. FLEXIBLE MOTHERBOARD RECOMMENDATIONS

- 12. GTL+ Interface Specification

- 12.1. SYSTEM SPECIFICATION

- 12.2. GENERAL GTL+ I/O BUFFER SPECIFICATION

- 12.3. PACKAGE SPECIFICATION

- 12.4. REF8N NETWORK

- 13. 3.3V Tolerant Signal Quality Specifications

- 14. Thermal Specifications

- 15. Mechanical Specifications

- 16. Tools

- 16.1. ANALOG MODELING

- 16.2. IN-TARGET PROBE FOR THE PENTIUM ® PRO PROCESSOR (ITP)

- 17. OverDrive ® Processor Socket Specification

- 17.1. INTRODUCTION

- 17.2. MECHANICAL SPECIFICATIONS

- 17.3. FUNCTIONAL OPERATION OF OVERDRIVE ® PROCESSOR SIGNALS

- 17.4. OVERDRIVE ® PROCESSOR ELECTRICAL SPECIFICATIONS

- 17.5. THERMAL SPECIFICATIONS

- 17.6. CRITERIA FOR OVERDRIVE ® PROCESSOR

- Appendix A. Signals Reference

- A.1. ALPHABETICAL SIGNALS REFERENCE

- A.1.1. A[35:3]# (I/O)

- A.1.2. A20M# (I)

- A.1.3. ADS# (I/O)

- A.1.4. AERR# (I/O)

- A.1.5. AP[1:0]# (I/O)

- A.1.6. ASZ[1:0]# (I/O)

- A.1.7. ATTR[7:0]# (I/O)

- A.1.8. BCLK (I)

- A.1.9. BE[7:0]# (I/O)

- A.1.10. BERR# (I/O)

- A.1.11. BINIT# (I/O)

- A.1.12. BNR# (I/O)

- A.1.13. BP[3:2]# (I/O)

- A.1.14. BPM[1:0]# (I/O)

- A.1.15. BPRI# (I)

- A.1.16. BR0#(I/O), BR[3:1]# (I)

- A.1.17. BREQ[3:0]# (I/O)

- A.1.18. D[63:0]# (I/O)

- A.1.19. DBSY# (I/O)

- A.1.20. DEFER# (I)

- A.1.21. DEN# (I/0)

- A.1.22. DEP[7:0]# (I/O)

- A.1.23. DID[7:0]# (I/O)

- A.1.24. DRDY# (I/O)

- A.1.25. DSZ[1:0]# (I/O)

- A.1.26. EXF[4:0]# (I/O)

- A.1.27. FERR# (O)

- A.1.28. FLUSH# (I)

- A.1.29. FRCERR(I/O)

- A.1.30. HIT# (I/O), HITM#(I/O)

- A.1.31. IERR# (O)

- A.1.32. IGNNE# (I)

- A.1.33. INIT# (I)

- A.1.34. INTR (I)

- A.1.35. LEN[1:0]# (I/O)

- A.1.36. LINT[1:0] (I)

- A.1.37. LOCK# (I/O)

- A.1.38. NMI (I)

- A.1.39. PICCLK (I)

- A.1.40. PICD[1:0] (I/O)

- A.1.41. PWR_GD (I)

- A.1.42. REQ[4:0]# (I/O)

- A.1.43. RESET# (I)

- A.1.44. RP# (I/O)

- A.1.45. RS[2:0]#(I)

- A.1.46. RSP# (I)

- A.1.47. SMI# (I)

- A.1.48. SMMEM# (I/O)

- A.1.49. SPLCK# (I/O)

- A.1.50. STPCLK# (I)

- A.1.51. TCK (I)

- A.1.52. TDI(I)

- A.1.53. TDO (O)

- A.1.54. TMS (I)

- A.1.55. TRDY# (I)

- A.1.56. TRST# (I)

- A.2. SIGNAL SUMMARIES

- A.1. ALPHABETICAL SIGNALS REFERENCE

- Index

- FIGURES

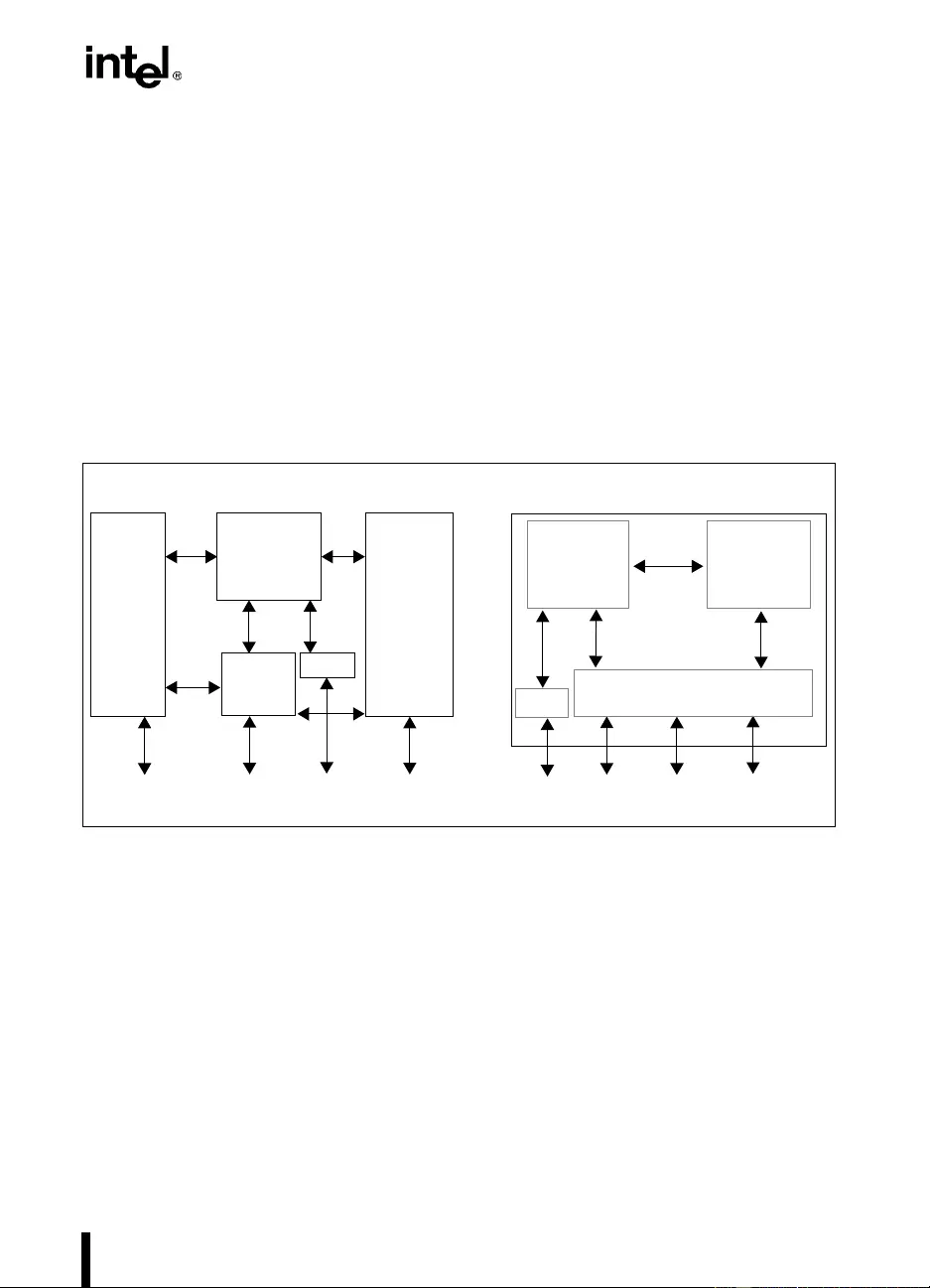

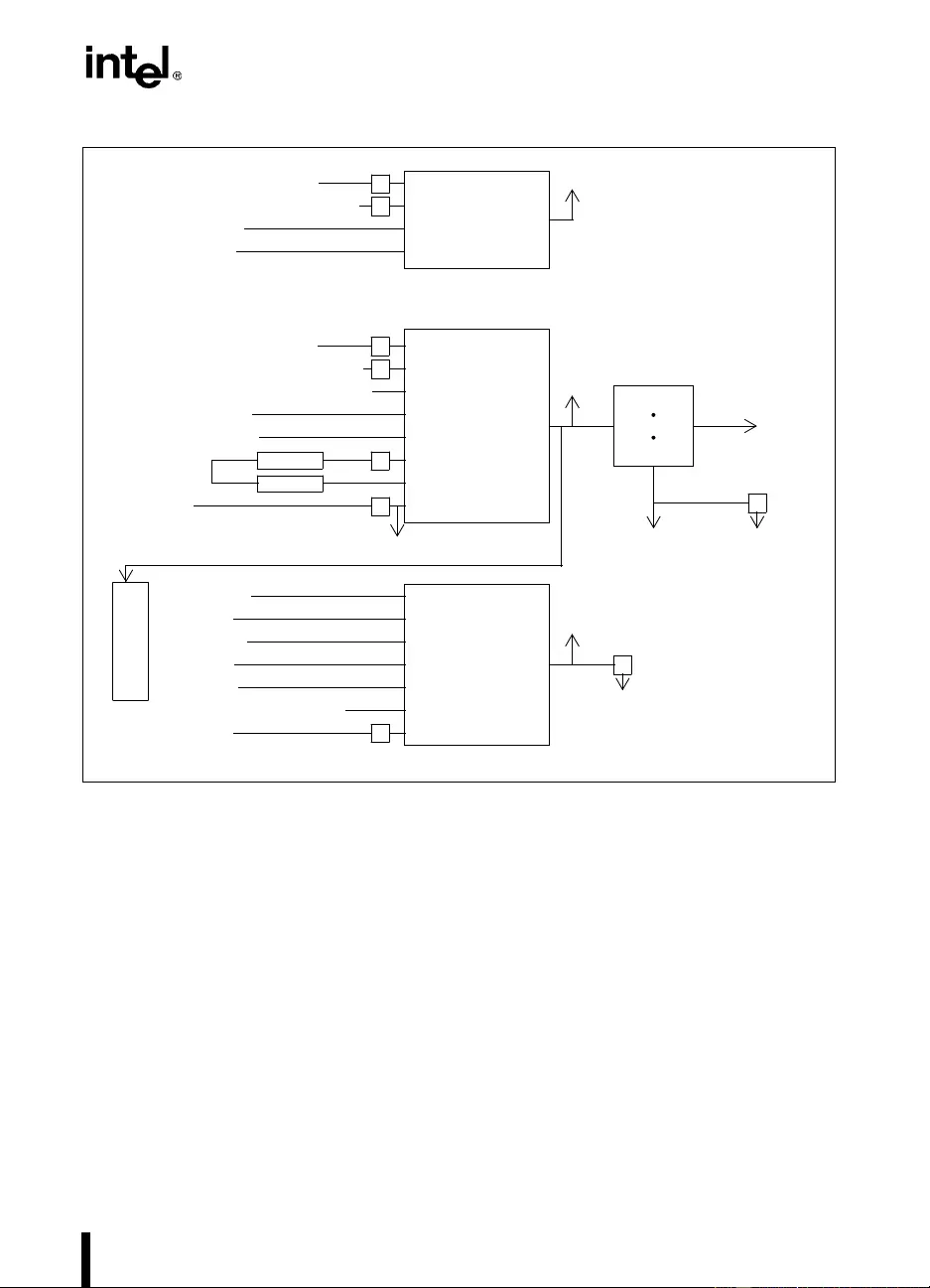

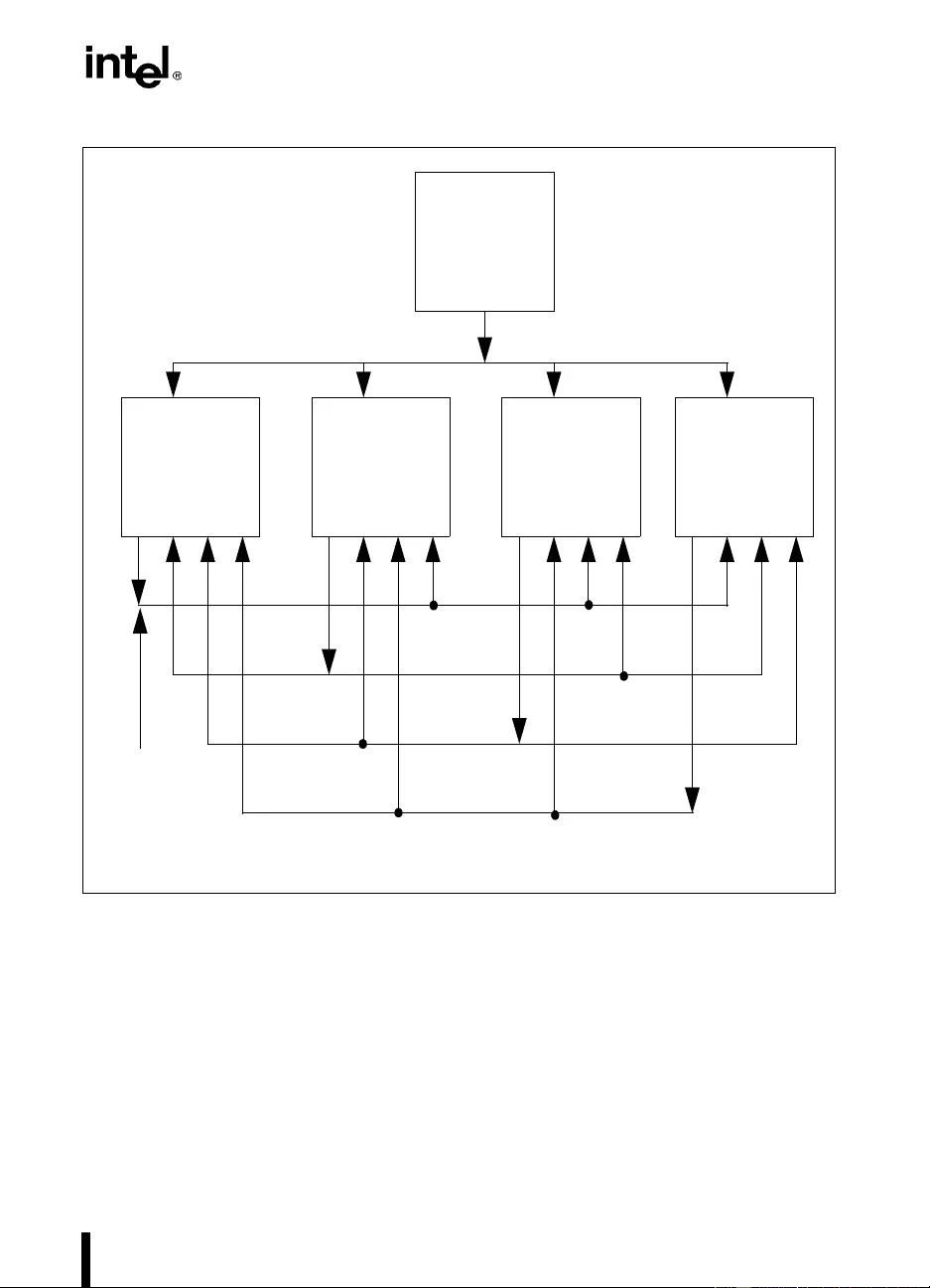

- Figure 1-1. The Pentium ® Pro Processor Integrating the CPU, L2 Cache, APIC and Bus Controller

- Figure 1-2. Pentium ® Pro Processor System Interface Block Diagram

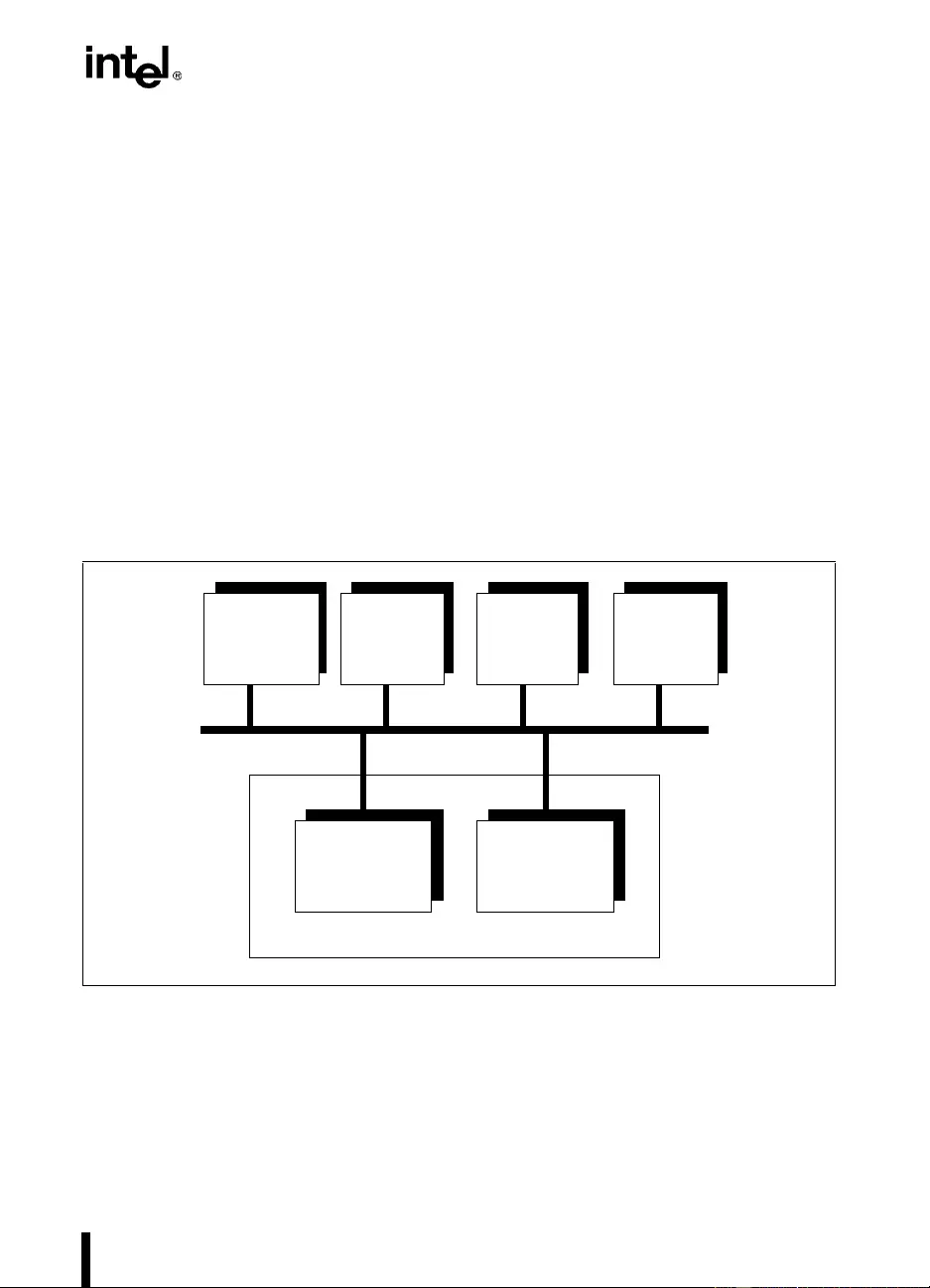

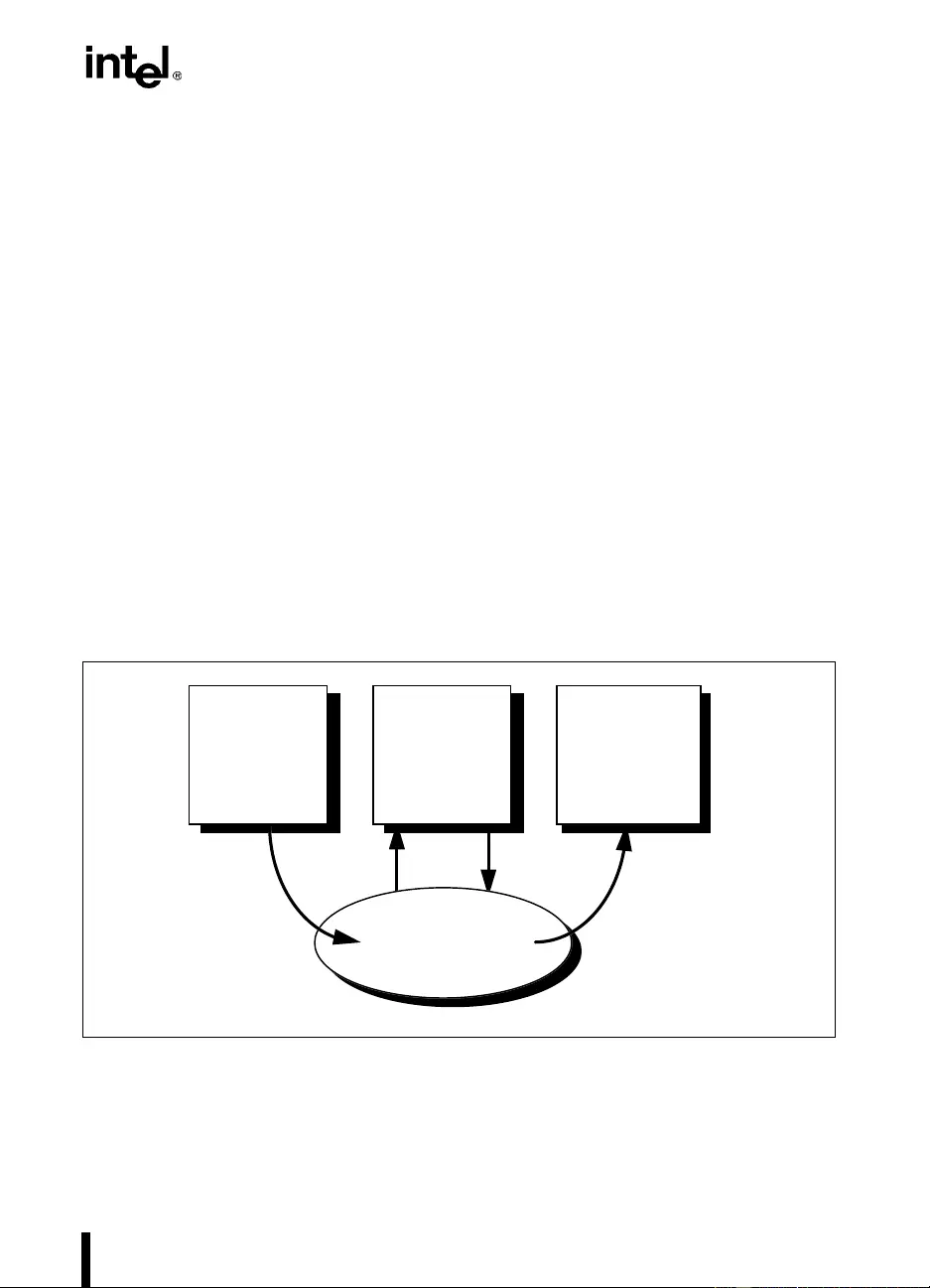

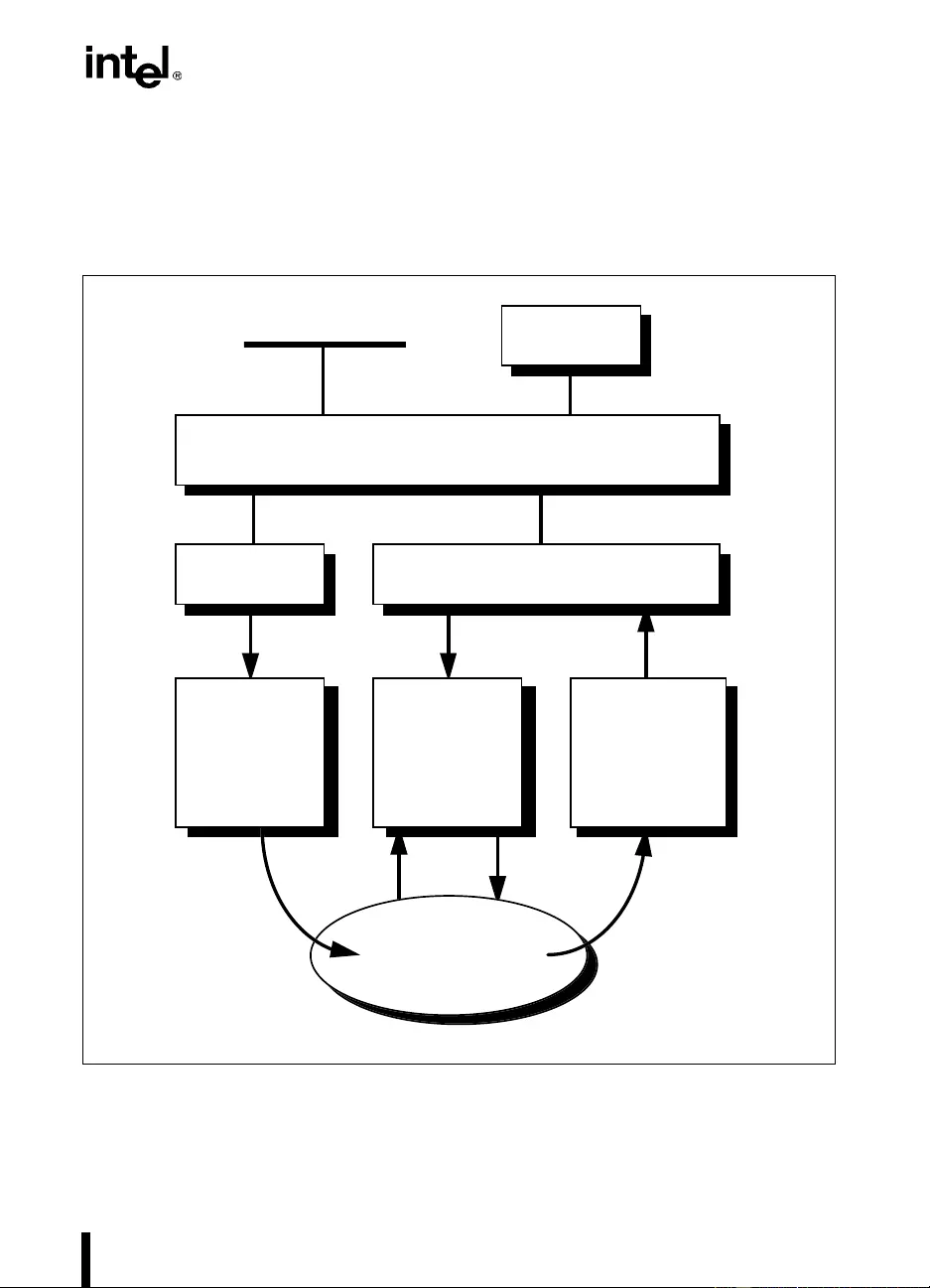

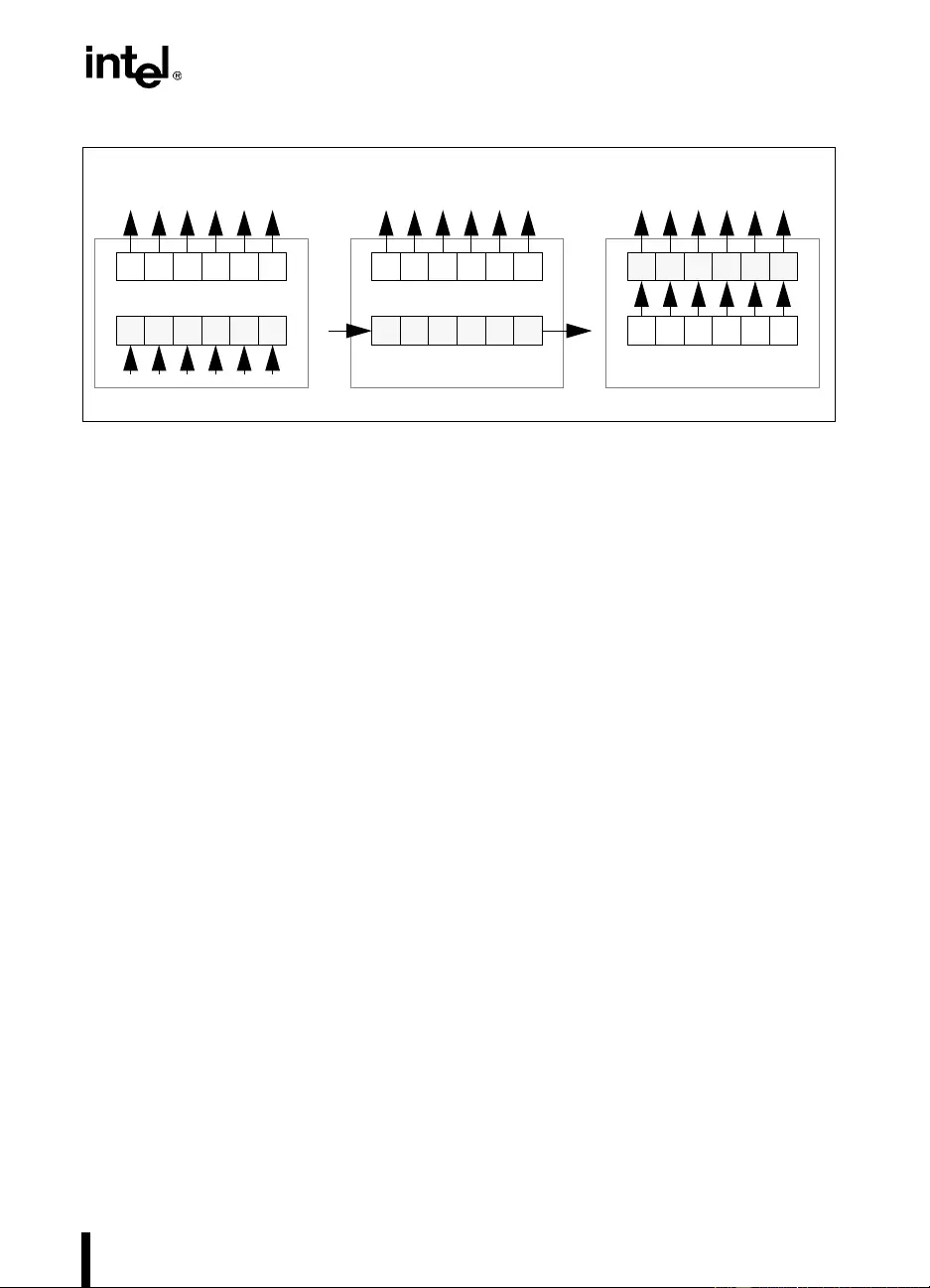

- Figure 2-1. Three Engines Communicating Using an Instruction Pool

- Figure 2-2. A Typical Code Fragment

- Figure 2-3. The Three Core Engines Interface with Memory via Unified Caches

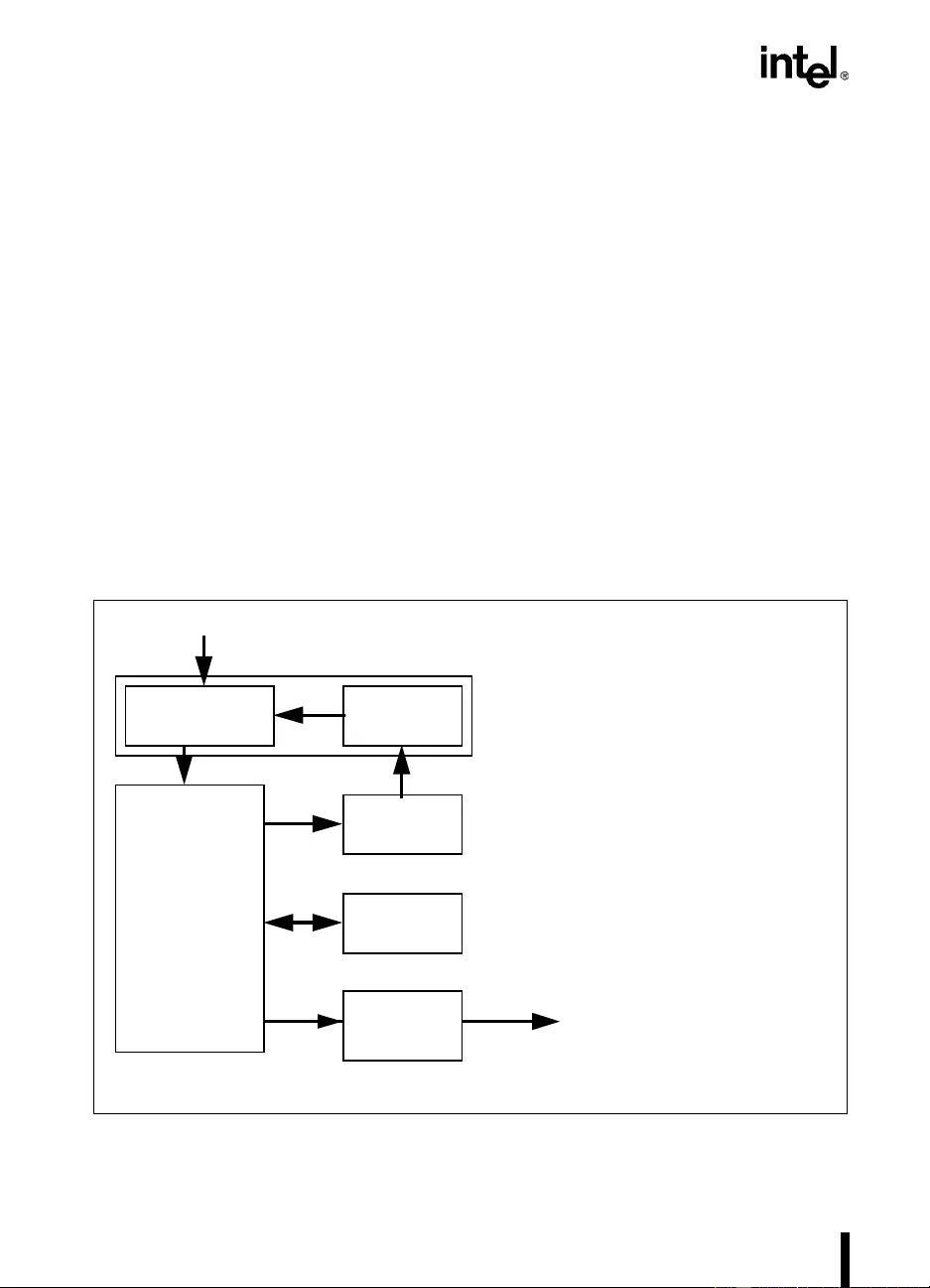

- Figure 2-4. Inside the Fetch/Decode Unit

- Figure 2-5. Inside the Dispatch/Execute Unit

- Figure 2-6. Inside the Retire Unit

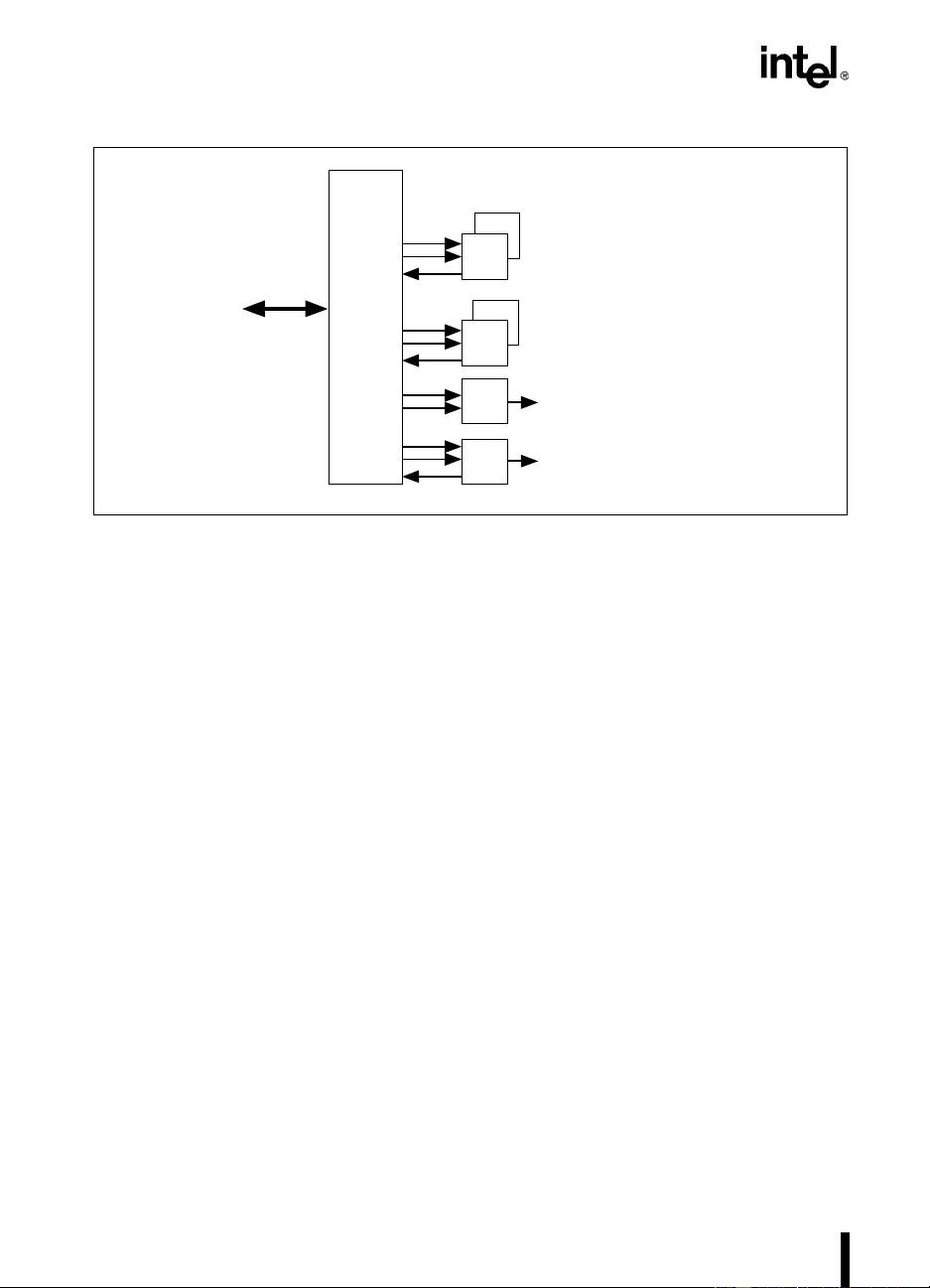

- Figure 2-7. Inside the Bus Interface Unit

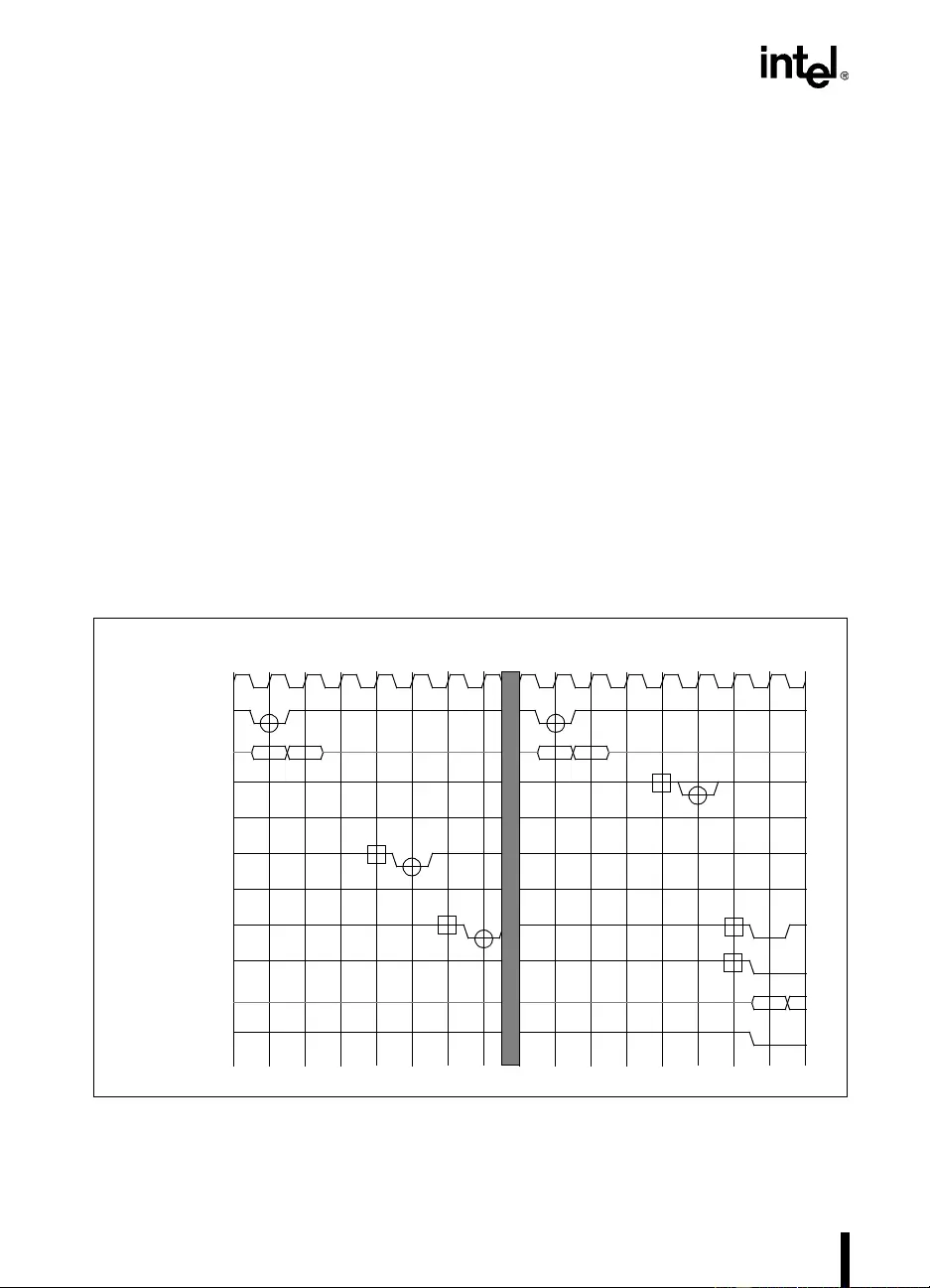

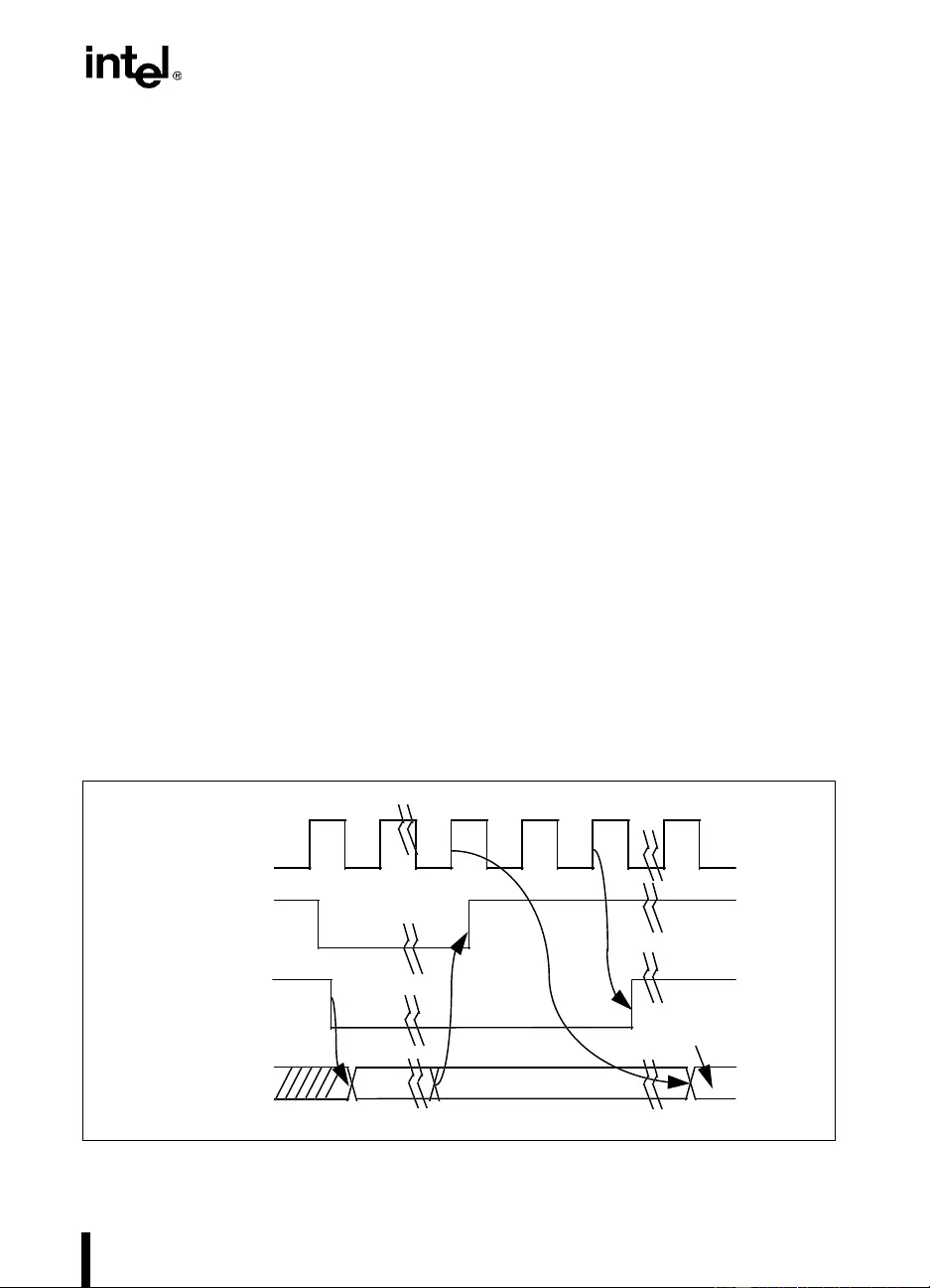

- Figure 3-1. Latched Bus Protocol

- Figure 3-2. Pentium ® Pro Processor Bus Transaction Phases

- Figure 4-1. BR[3:0]# Physical Interconnection

- Figure 4-2. Symmetric Arbitration of a Single Agent After RESET#

- Figure 4-3. Signal Deassertion After Bus Reset

- Figure 4-4. Delay of Transaction Generation After Reset

- Figure 4-5. Symmetric Bus Arbitration with no LOCK#

- Figure 4-6. Symmetric Arbitration with no Transaction Generation

- Figure 4-7. Bus Exchange Among Symmetric and Priority Agent with no LOCK#

- Figure 4-8. Symmetric and Priority Bus Exchange During LOCK#

- Figure 4-9. BNR# Sampling After RESET#

- Figure 4-10. BNR# Sampling After ADS#

- Figure 4-11. Request Generation Phase

- Figure 4-12. Four-Clock Snoop Phase

- Figure 4-13. Snoop Phase Stall Due to a Slower Agent

- Figure 4-14. RS[2:0]# Activation with no TRDY#

- Figure 4-15. RS[2:0]# Activation with Request Initiated TRDY#

- Figure 4-16. RS[2:0]# Activation with Snoop Initiated TRDY#

- Figure 4-17. RS[2:0]# Activation After Two TRDY# Assertions

- Figure 4-18. Request Initiated Data Transfer

- Figure 4-19. Response Initiated Data Transfer

- Figure 4-20. Snoop Initiated Data Transfer

- Figure 4-21. Full Speed Read Partial Transactions

- Figure 4-22. Relaxed DBSY# Deassertion

- Figure 4-23. Full Speed Read Line Transactions

- Figure 4-24. Full Speed Write Partial Transactions

- Figure 4-25. Full Speed Write Line Transactions

- Figure 5-1. Bus Transactions

- Figure 5-2. Response Responsibility Pickup Effect on an Outstanding Invalidation Transaction

- Figure 5-3. Deferred Response Followed by a Deferred Reply to a Read Operation

- Figure 8-1. BERR# Protocol Mechanism

- Figure 8-2. BINIT# Protocol Mechanism

- Figure 8-3. Pentium ® Pro Processor Errors

- Figure 9-1. Hardware Configuration Signal Sampling

- Figure 9-2. BR[3:0]# Physical Interconnection

- Figure 10-1. Simplified Block Diagram of Pentium ® Pro Processor TAP logic

- Figure 10-2. TAP Controller Finite State Machine

- Figure 10-3. Pentium ® Pro Processor TAP instruction Register

- Figure 10-4. Operation of the Pentium ® Pro Processor TAP Instruction Register

- Figure 10-5. TAP Instruction Register Access

- Figure 11-1. GTL+ Bus Topology

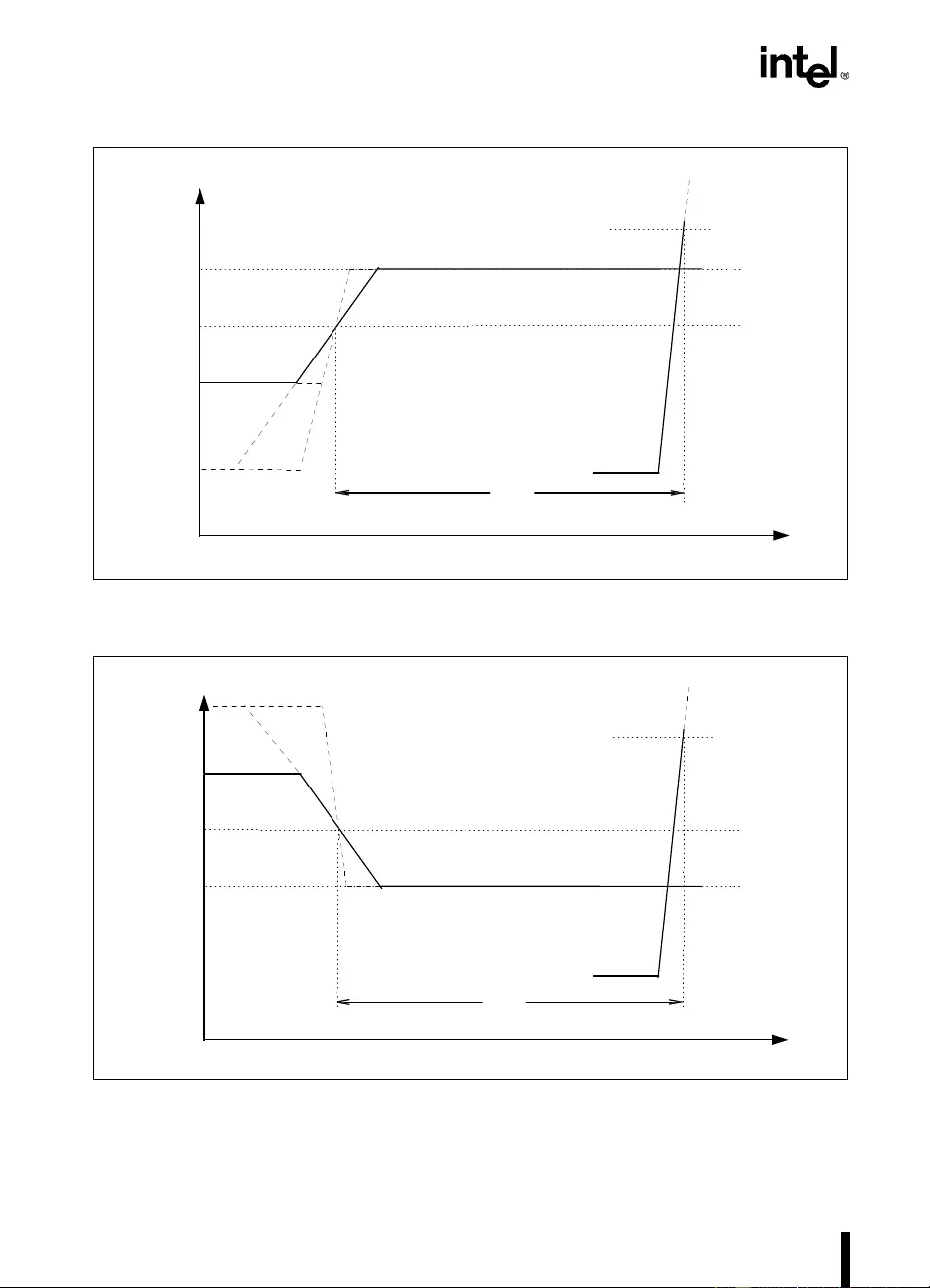

- Figure 11-2. Transient Types

- Figure 11-3. Timing Diagram of Clock Ratio Signals

- Figure 11-4. Example Schematic for Clock Ratio Pin Sharing

- Figure 11-5. PWRGOOD Relationship at Power-On

- Figure 11-6. 3.3V Tolerant Group Derating Curve

- Figure 11-7. Generic Clock Waveform

- Figure 11-8. Valid Delay Timings

- Figure 11-9. Setup and Hold Timings

- Figure 11-10. Lo to Hi GTL+ Receiver Ringback Tolerance

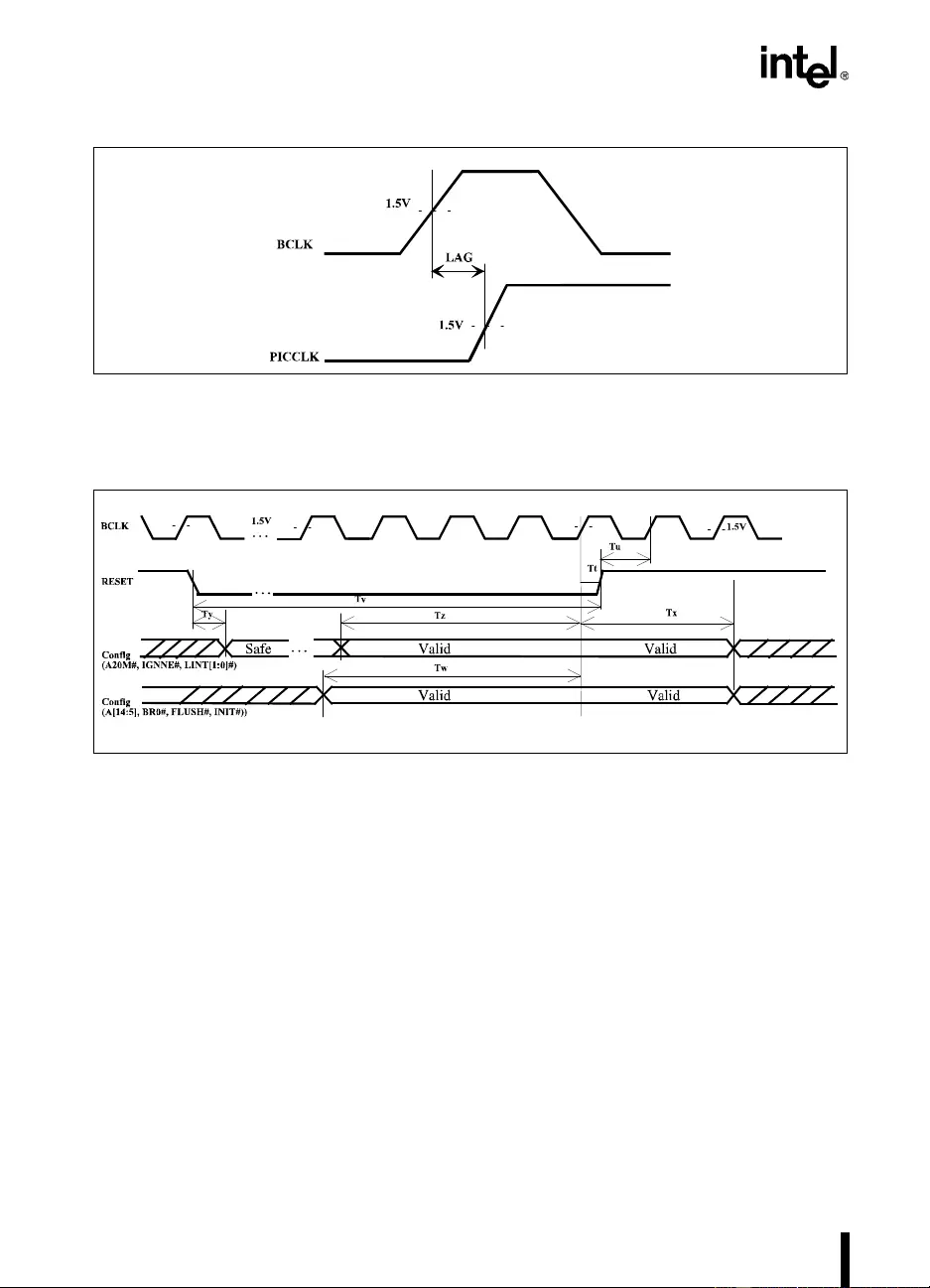

- Figure 11-11. FRC Mode BCLK to PICCLK Timing

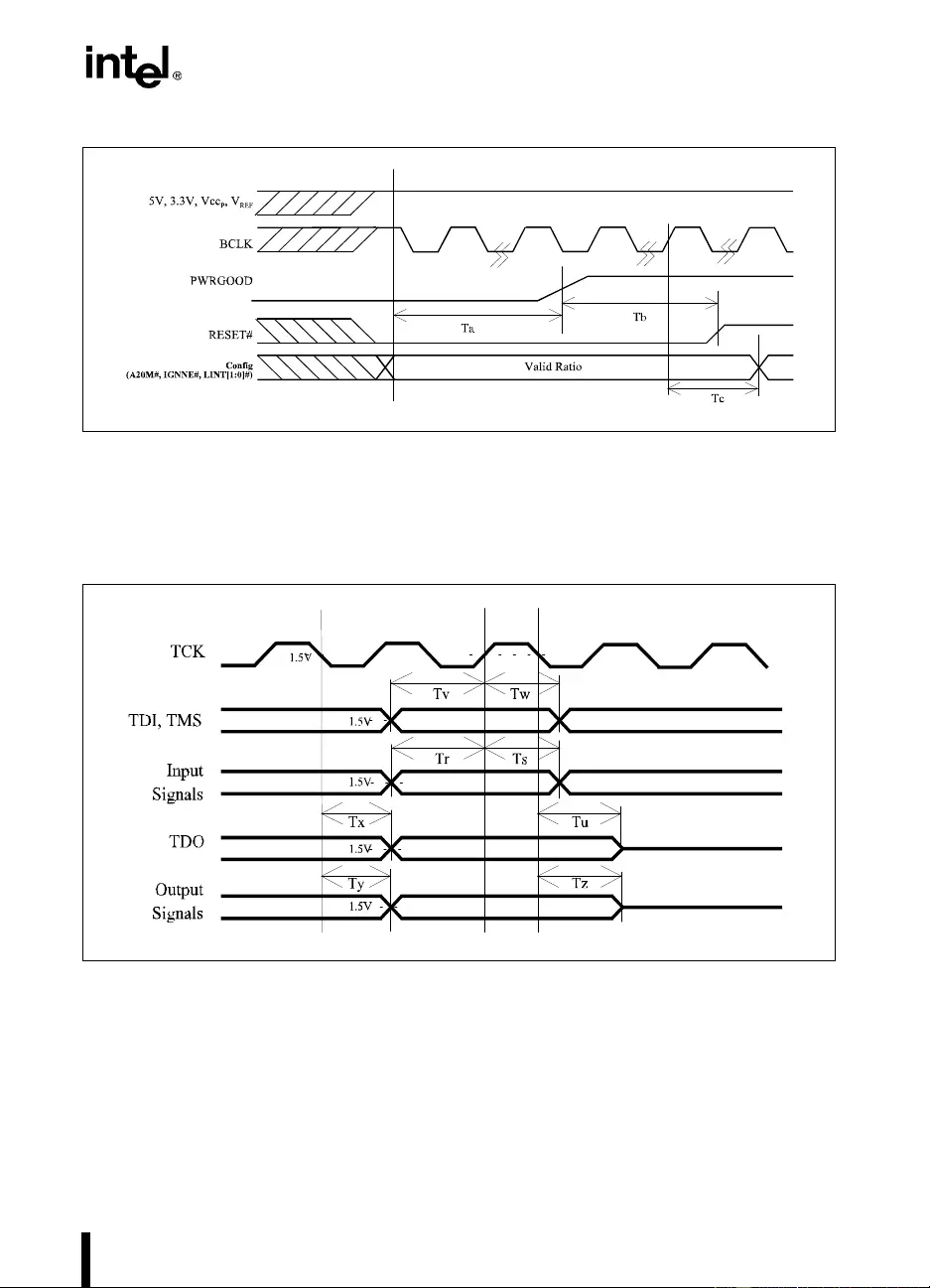

- Figure 11-12. Reset and Configuration Timings

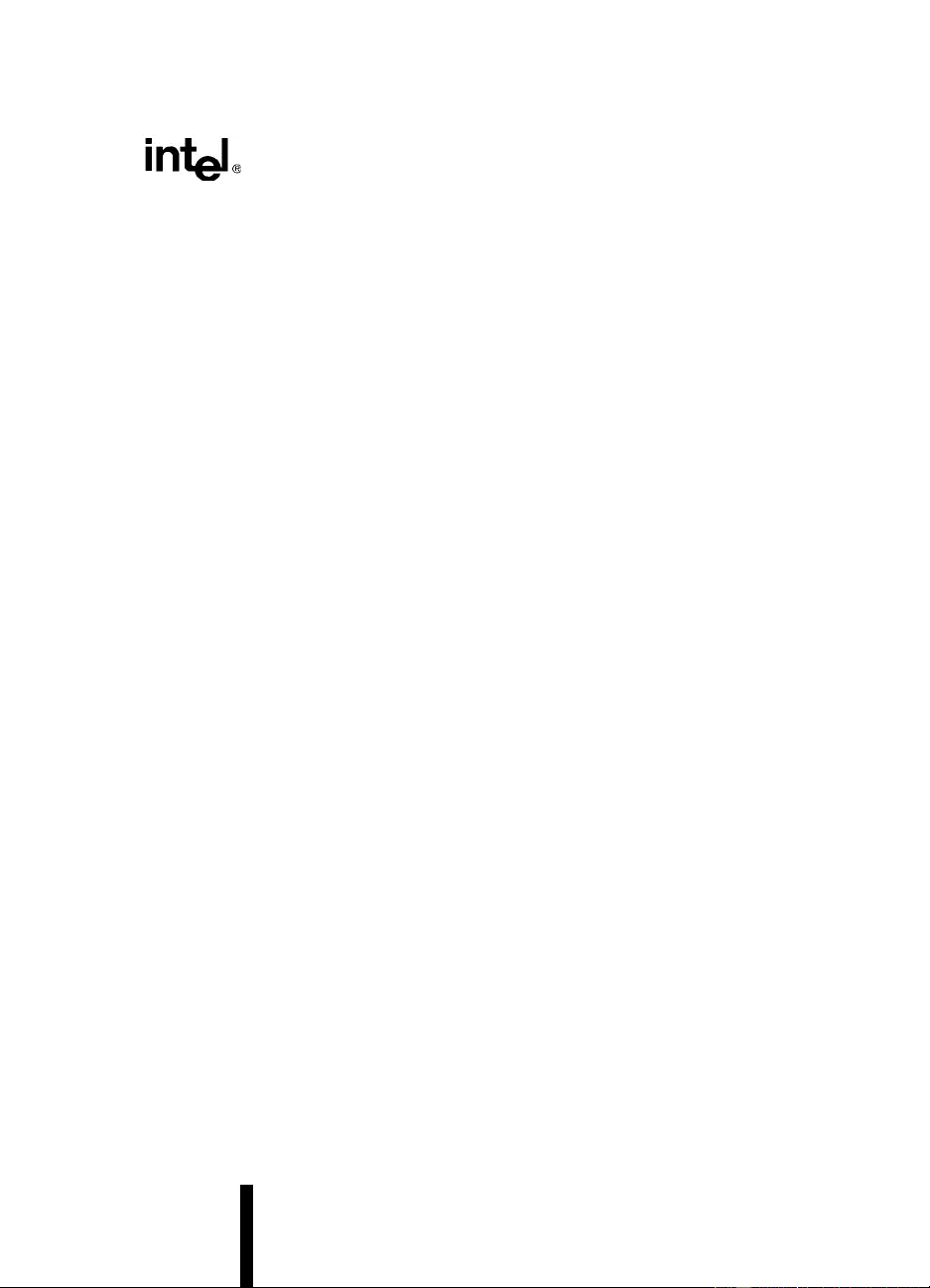

- Figure 11-13. Power-On Reset and Configuration Timings

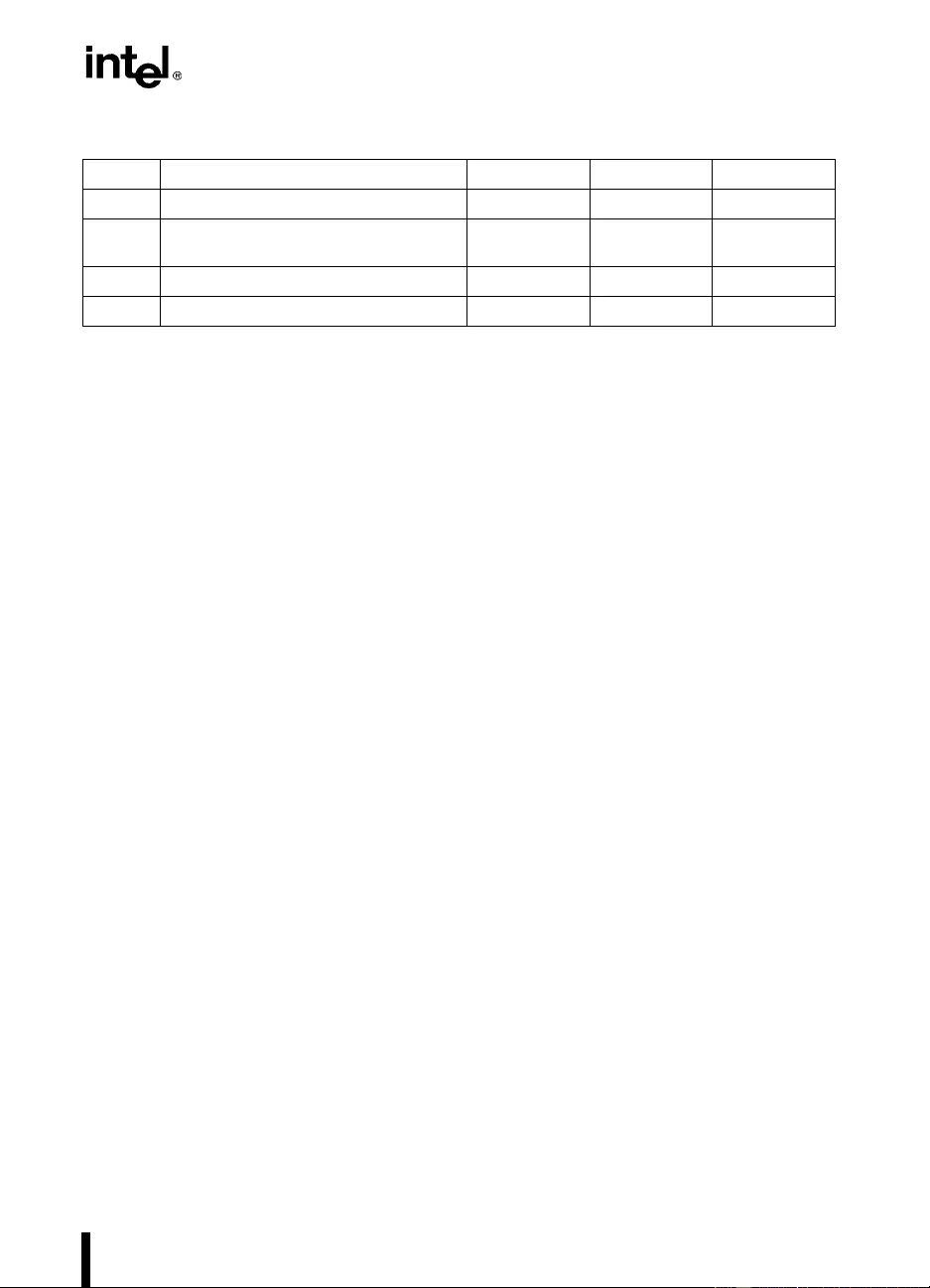

- Figure 11-14. Test Timings (Boundary Scan)

- Figure 11-15. Test Reset Timing

- Figure 12-1. Example Terminated Bus with GTL+ Transceivers

- Figure 12-2. Receiver Waveform Showing Signal Quality Parameters

- Figure 12-3. Standard Input Lo-to-Hi Waveform for Characterizing Receiver Ringback Tolerance

- Figure 12-4. Standard Input Hi-to-Lo Waveform for Characterizing Receiver Ringback Tolerance

- Figure 12-5. Measuring Nominal Flight Time

- Figure 12-6. Flight Time of a Rising Edge Slower Than 0.3V/ns

- Figure 12-7. Extrapolated Flight Time of a Non-Monotonic Rising Edge

- Figure 12-8. Extrapolated Flight Time of a Non-Monotonic Falling Edge

- Figure 12-9. Acceptable Driver Signal Quality

- Figure 12-10. Unacceptable Signal, Due to Excessively Slow Edge After Crossing V REF

- Figure 12-11. Test Load for Measuring Output AC Timings

- Figure 12-12. Clock to Output Data Timing (T CO )

- Figure 12-13. Standard Input Lo-to-Hi Waveform for Characterizing Receiver Setup Time

- Figure 12-14. Standard Input Hi-to-Lo Waveform for Characterizing Receiver Setup Time

- Figure 12-15. Ref8N Topology

- Figure 13-1. 3.3V Tolerant Signal Overshoot/Undershoot and Ringback

- Figure 14-1. Location of Case Temperature Measurement (Top-Side View)

- Figure 14-2. Thermocouple Placement

- Figure 14-3. Thermal Resistance Relationships

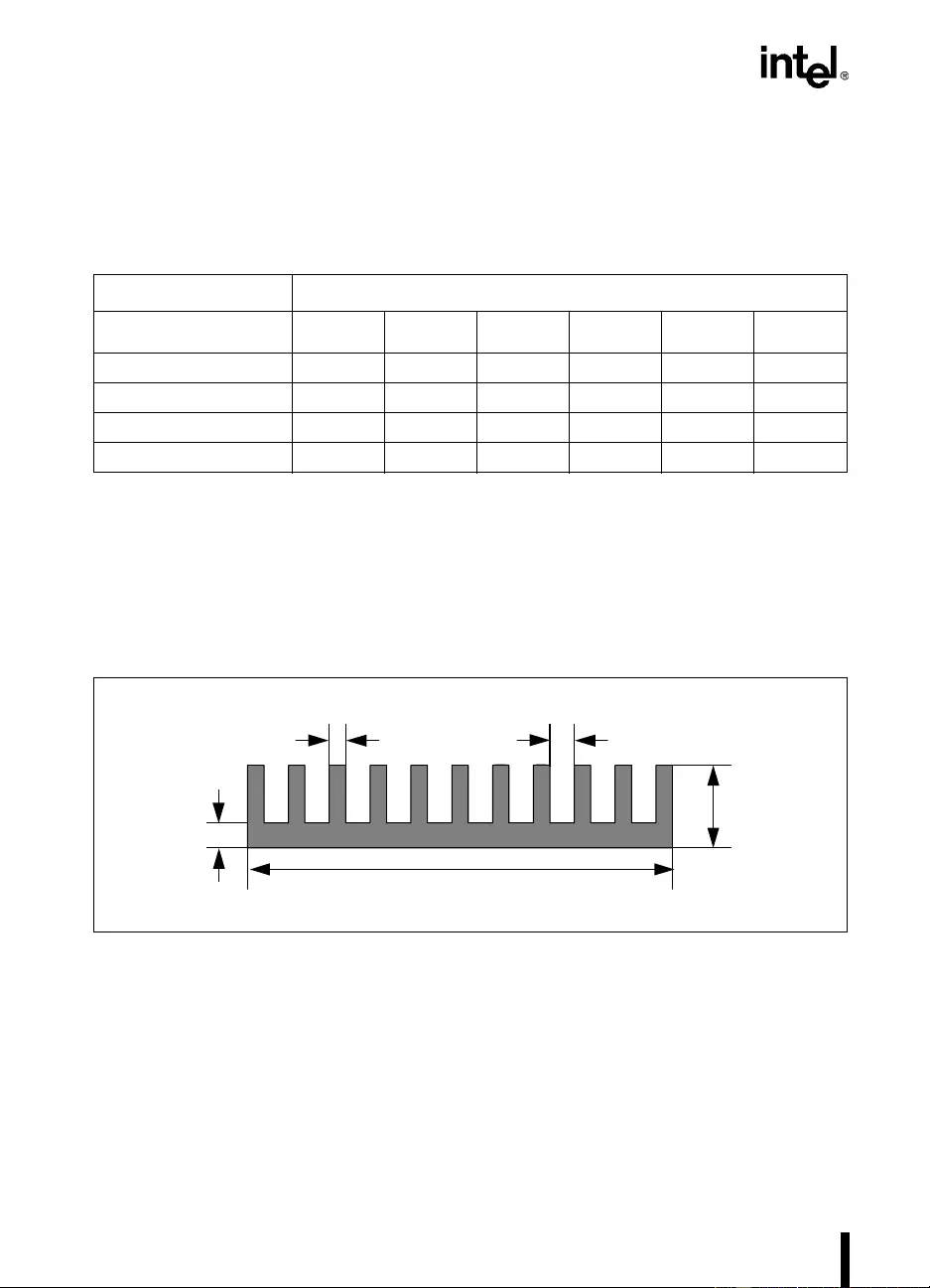

- Figure 14-4. Analysis Heat Sink Dimensions

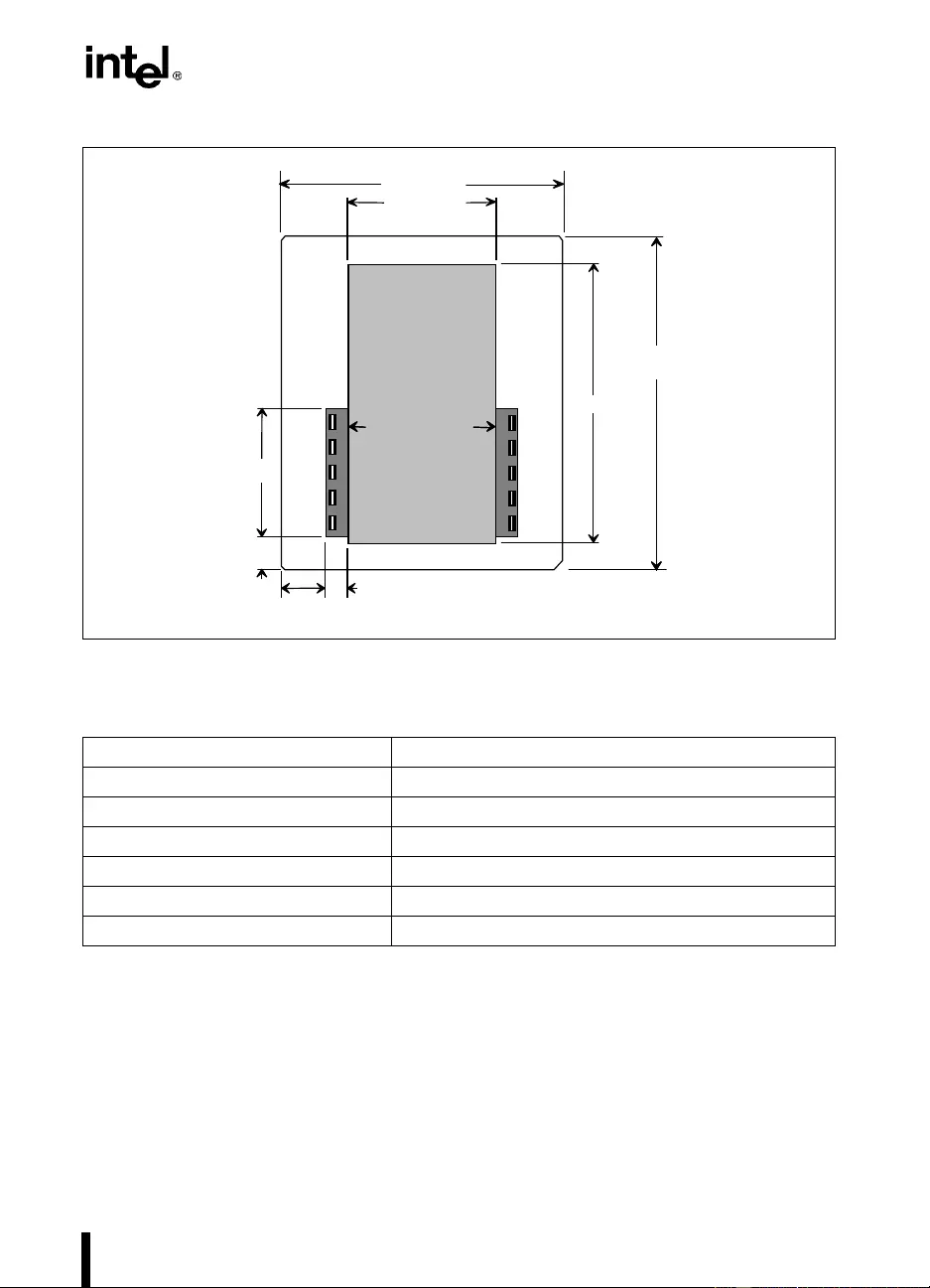

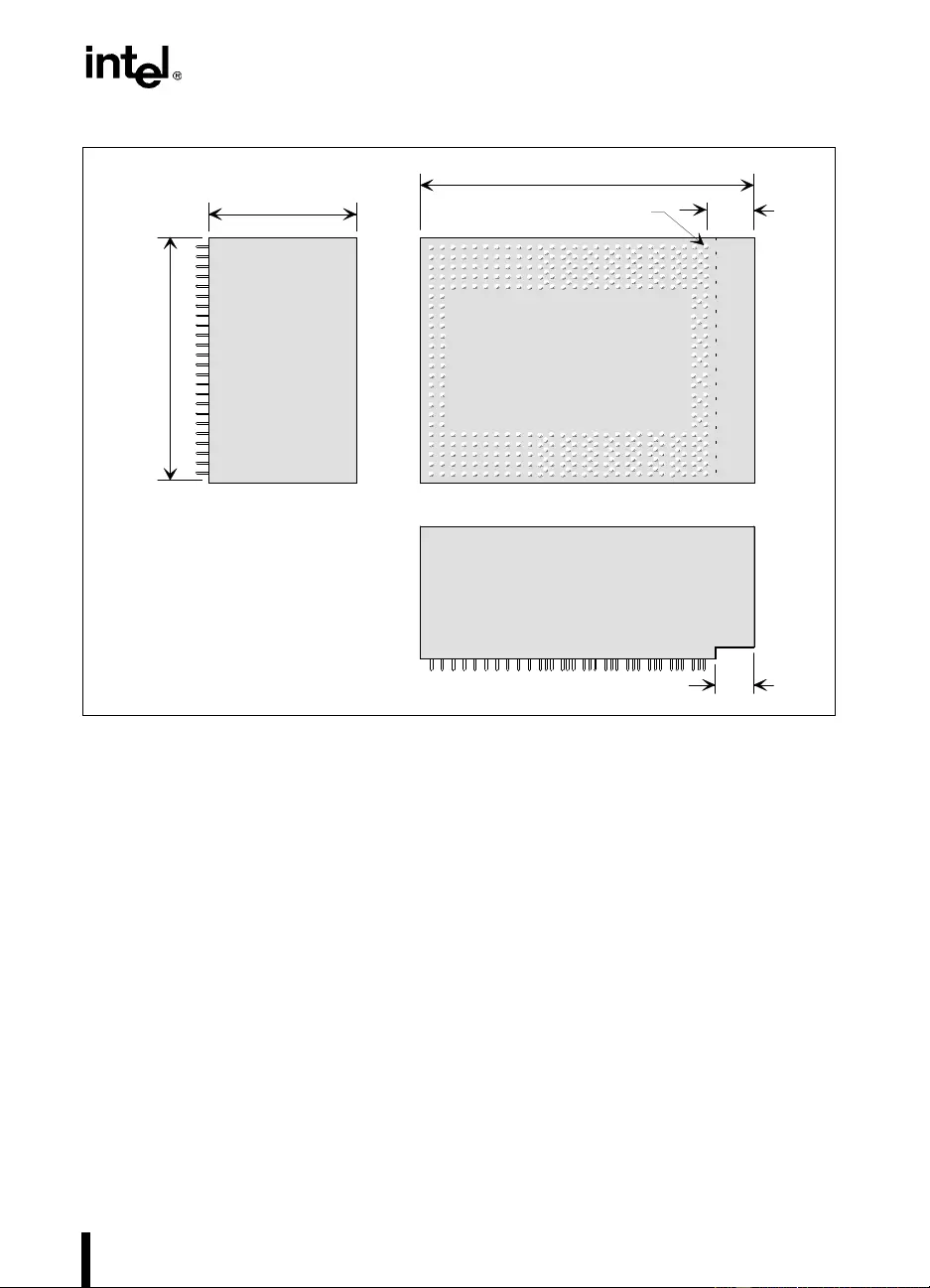

- Figure 15-1. Package Dimensions-Bottom View

- Figure 15-2. Top View of Keep Out Zones and Heat Spreader

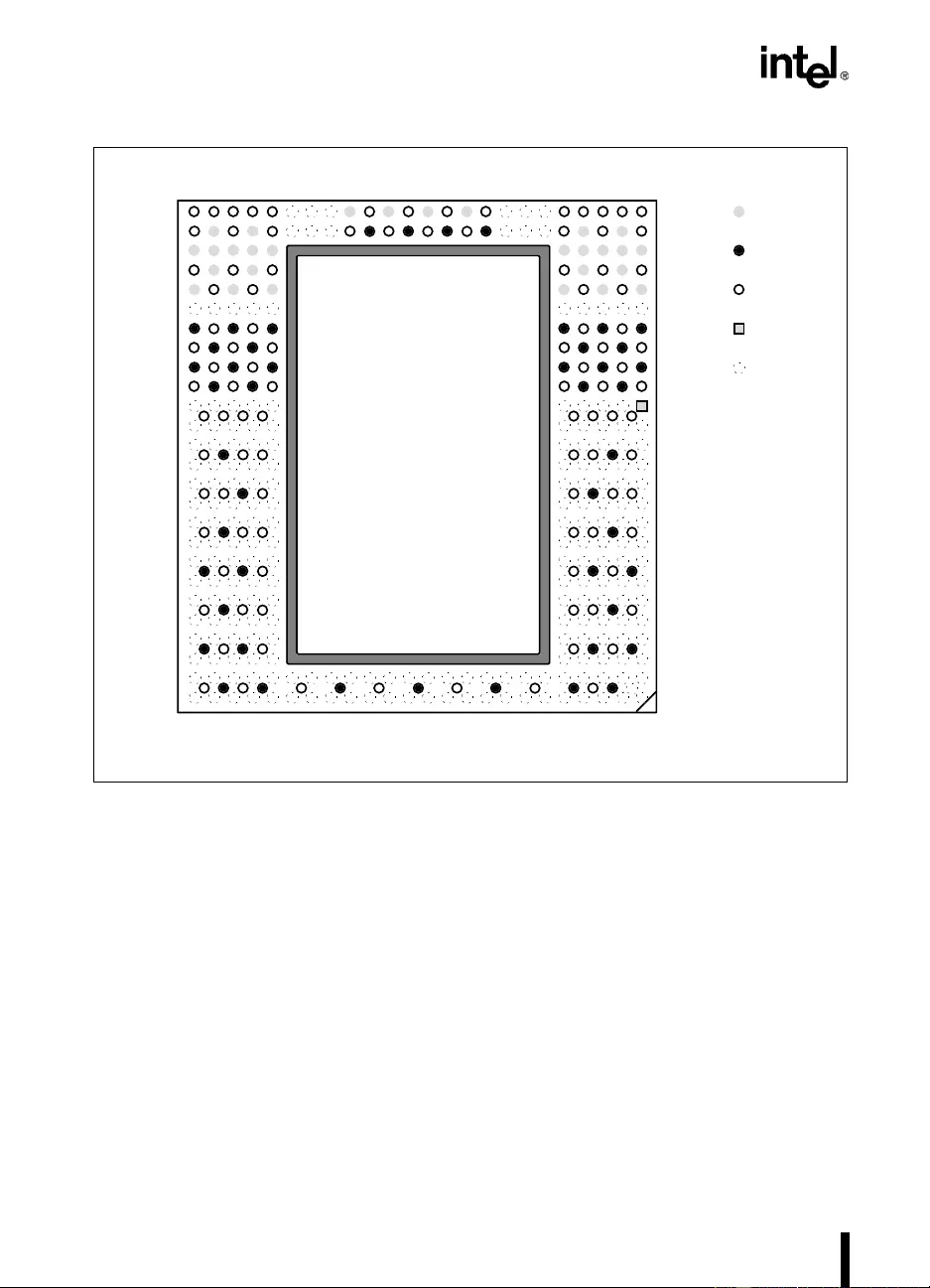

- Figure 15-3. Pentium ® Pro Processor Top View with Power Pin Locations

- Figure 16-1. GTL+ Signal Termination

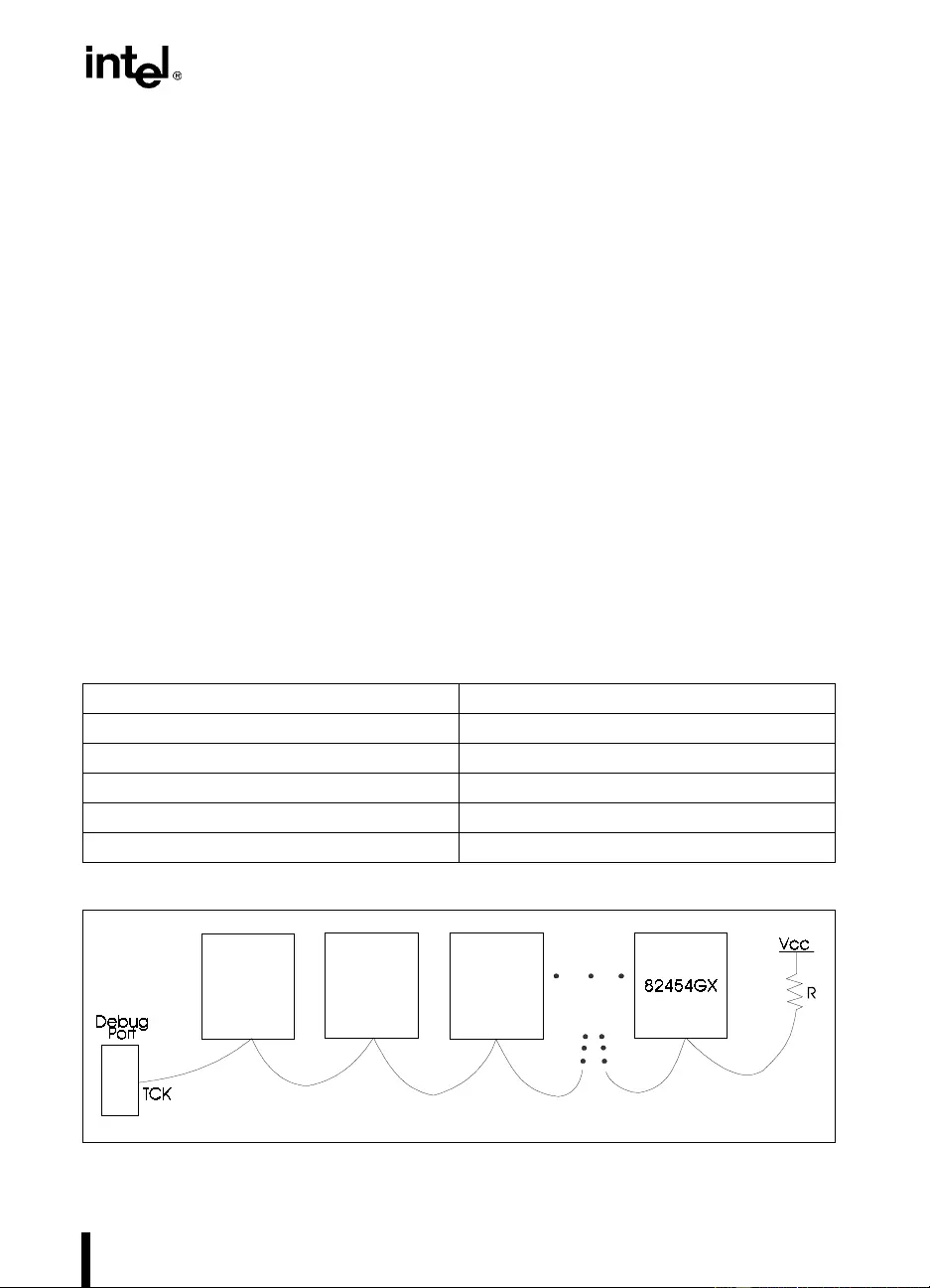

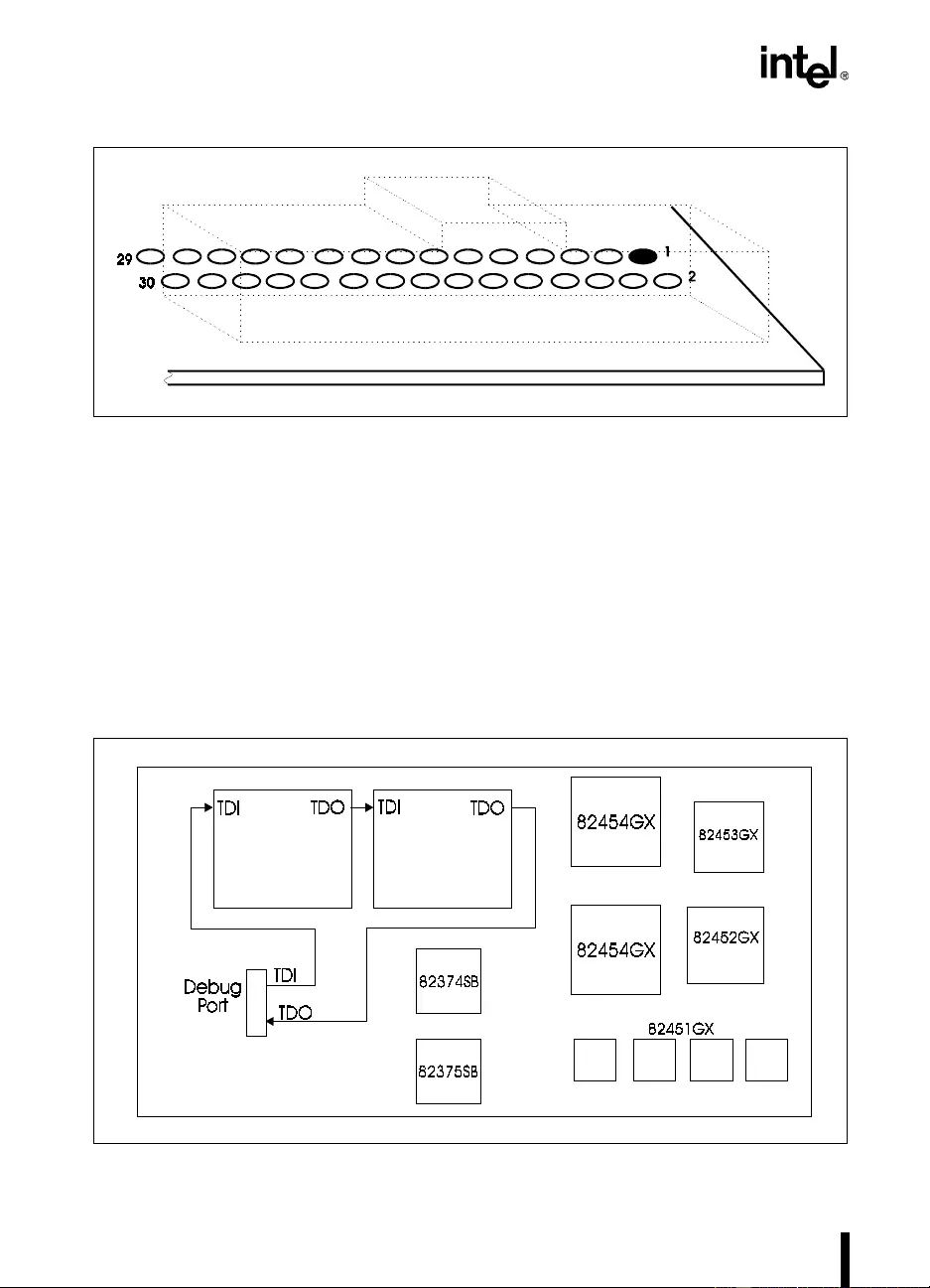

- Figure 16-2. TCK with Daisy Chain Configuration

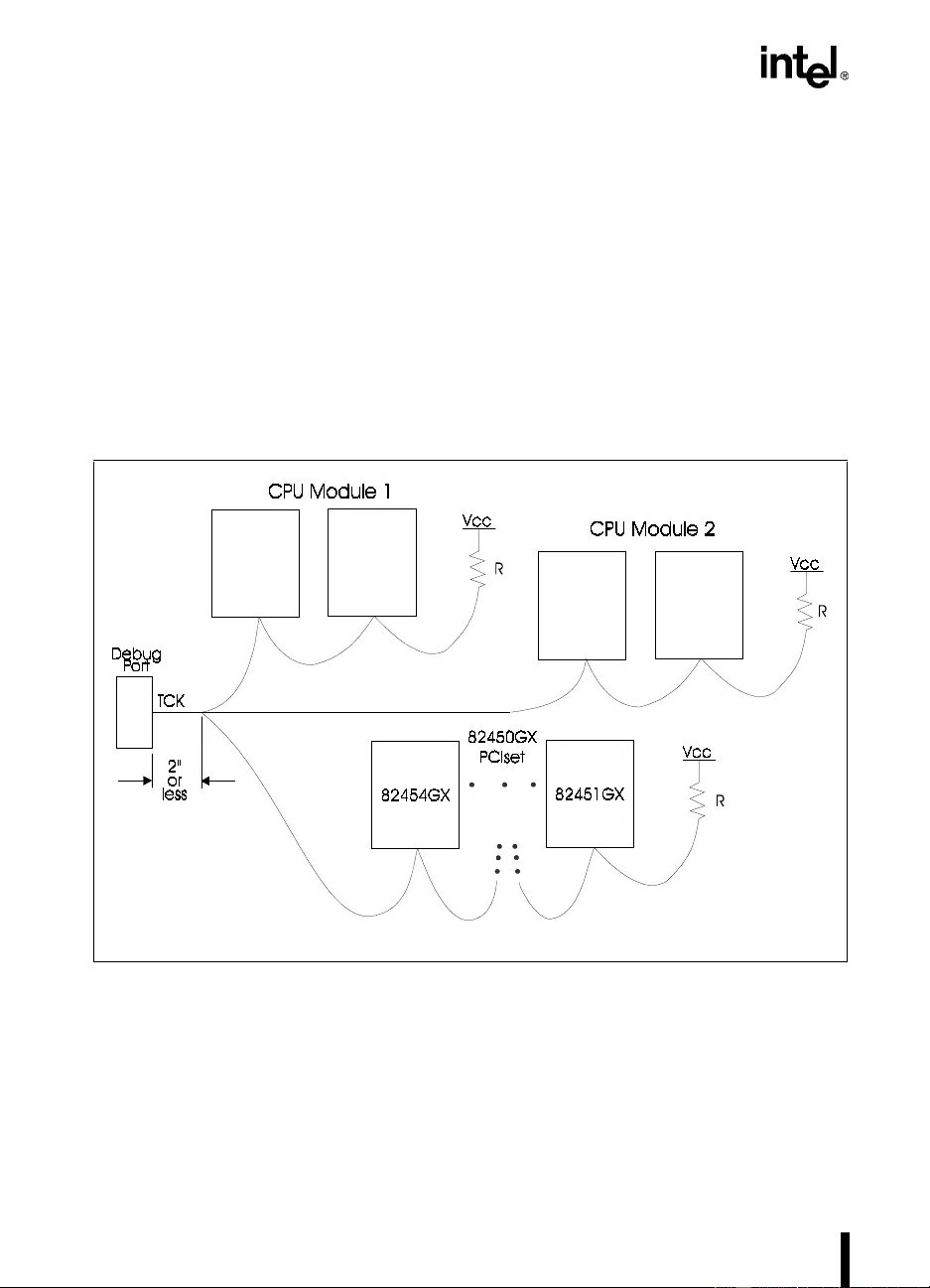

- Figure 16-3. TCK with Star Configuration

- Figure 16-4. Generic MP System Layout for Debug Port Connection

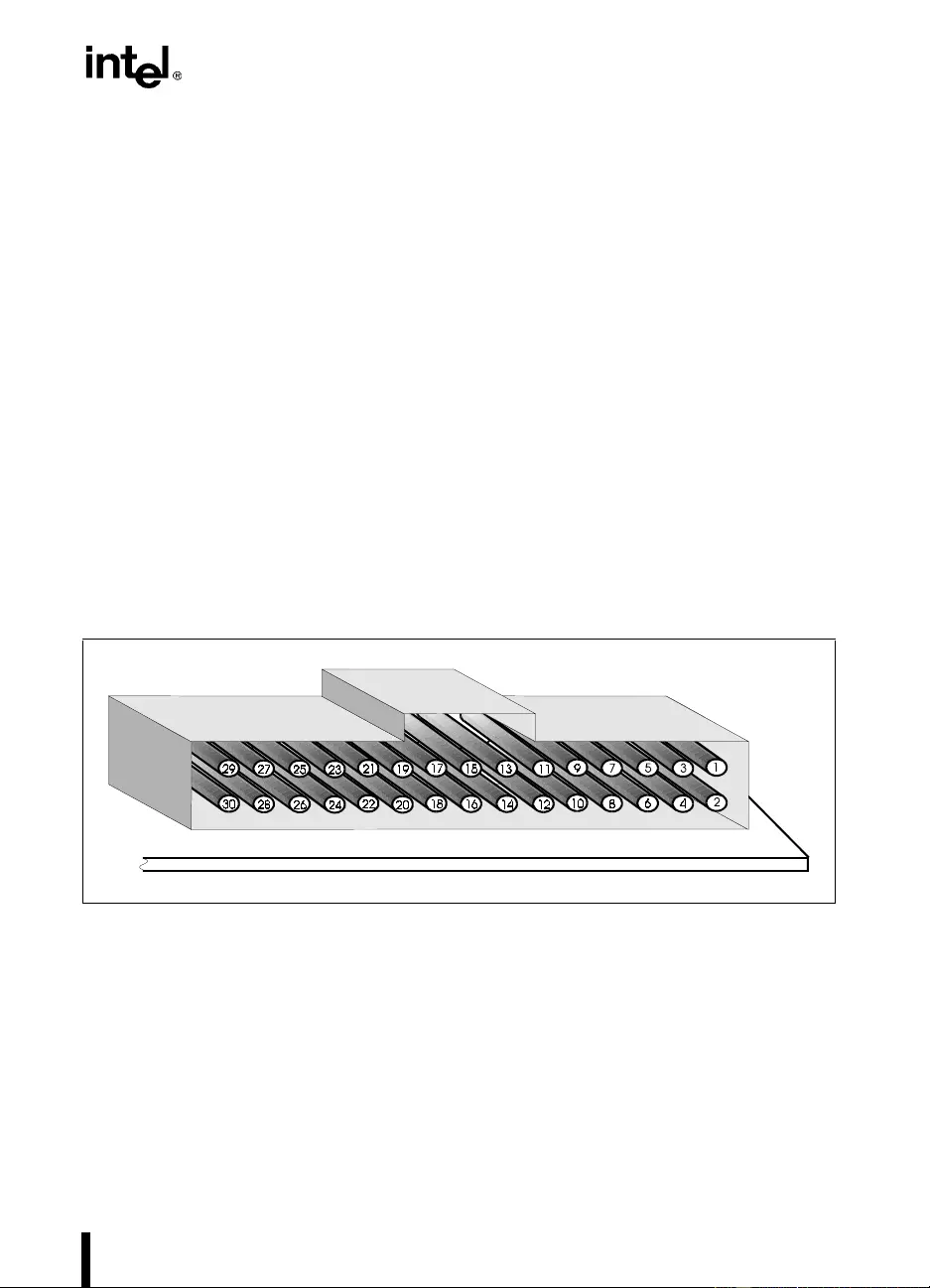

- Figure 16-5. Debug Port Connector on Primary Side of Circuit Board

- Figure 16-6. Hole Layout for Connector on Primary Side of Circuit Board

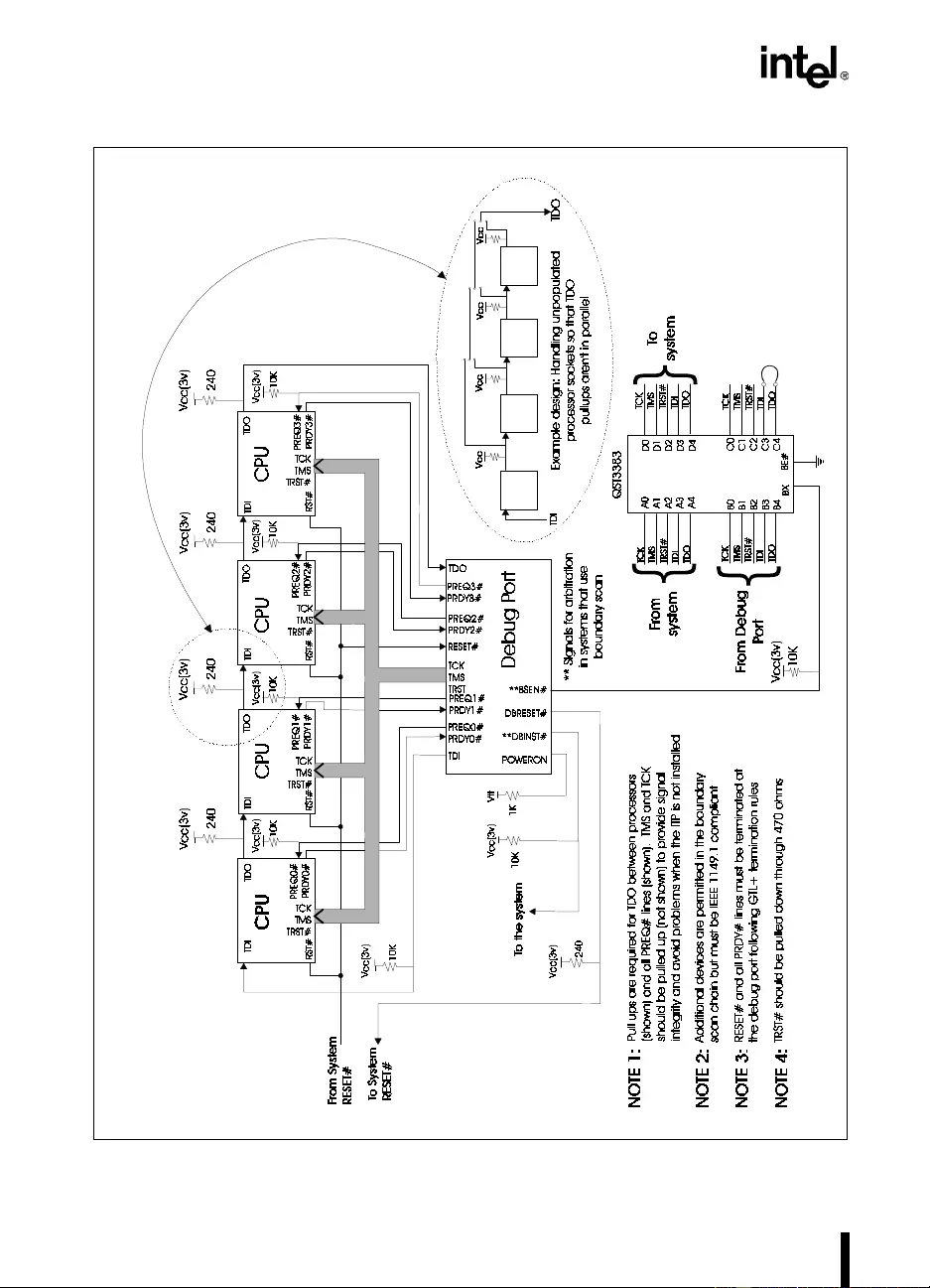

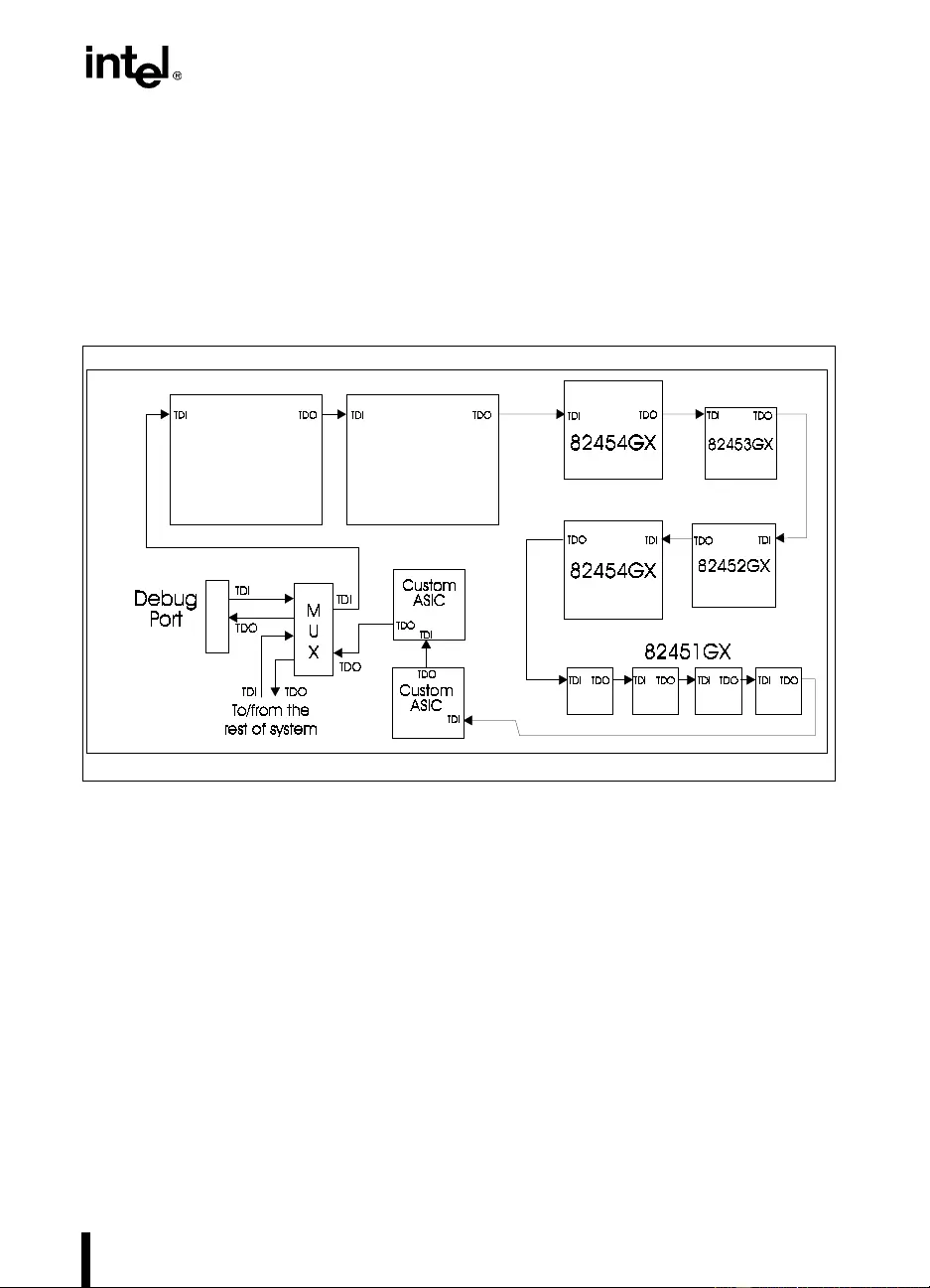

- Figure 16-7. Pentium ® Pro Processor-Based System Where Boundary Scan is Not Used

- Figure 16-8. Pentium ® Pro Processor-Based System Where Boundary Scan is Used

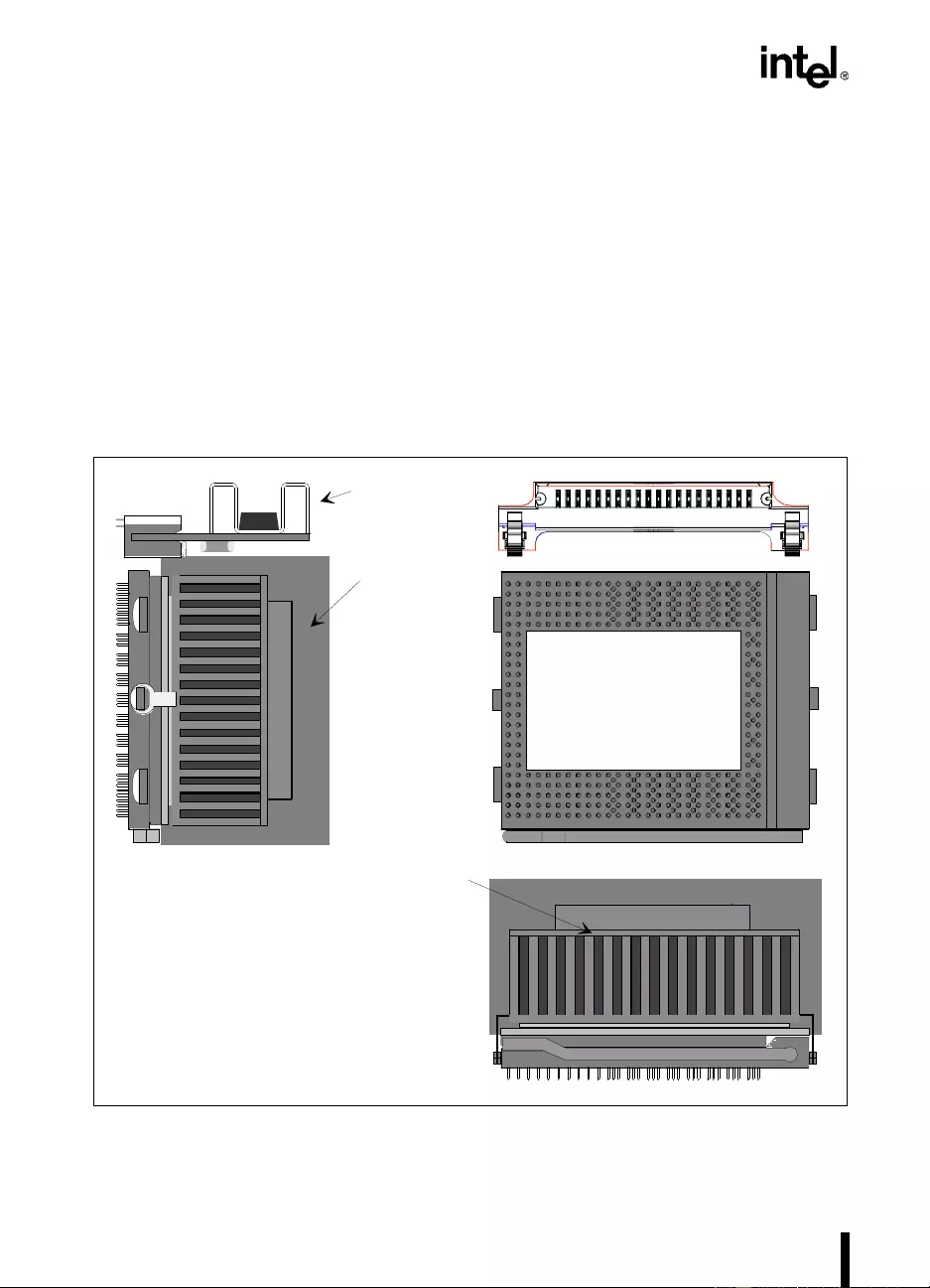

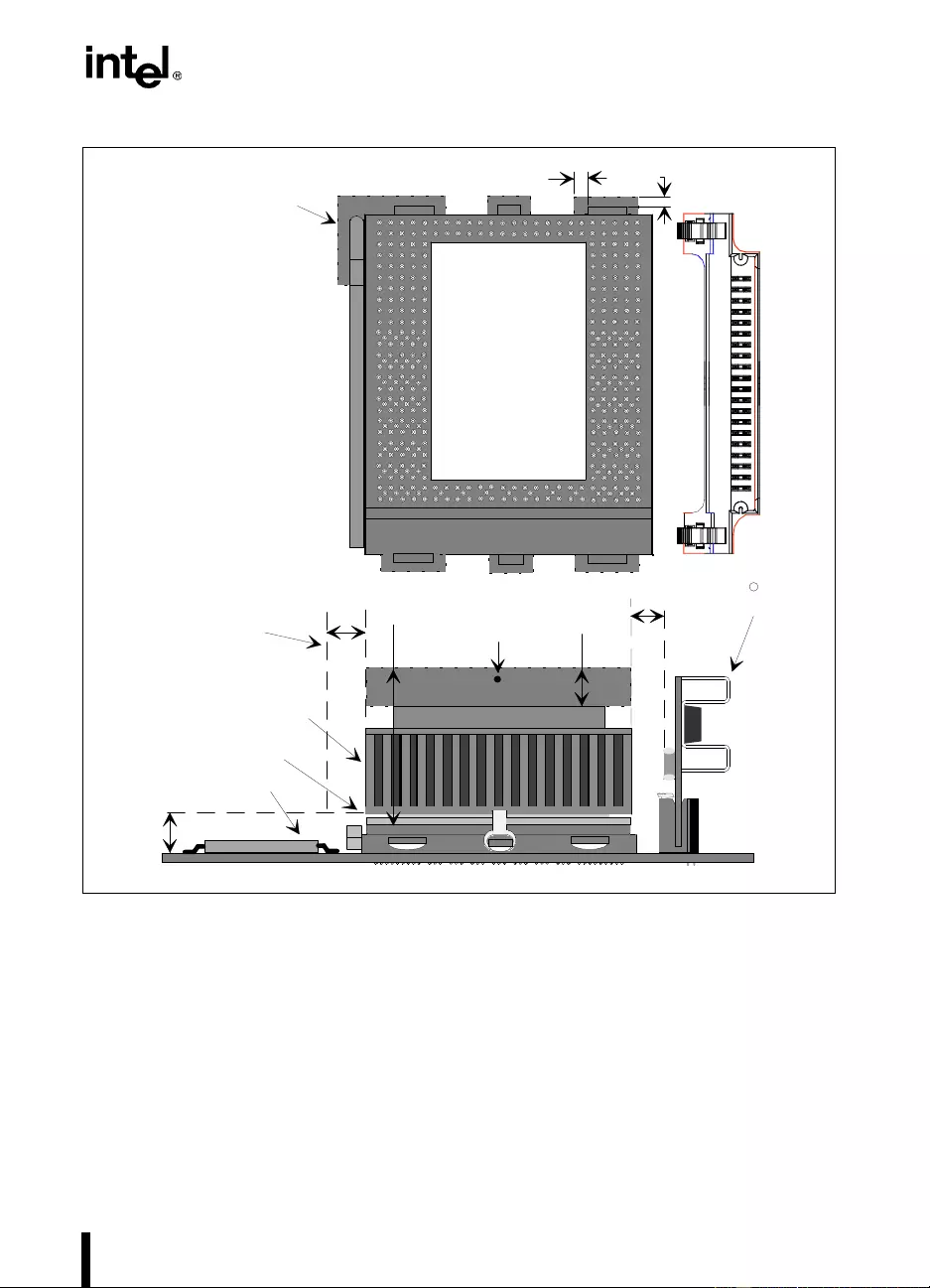

- Figure 17-1. Socket 8 Shown with the Fan/heatsink Cooling Solution, Clip Attachment Features and Adjacent Voltage Regulator Modu

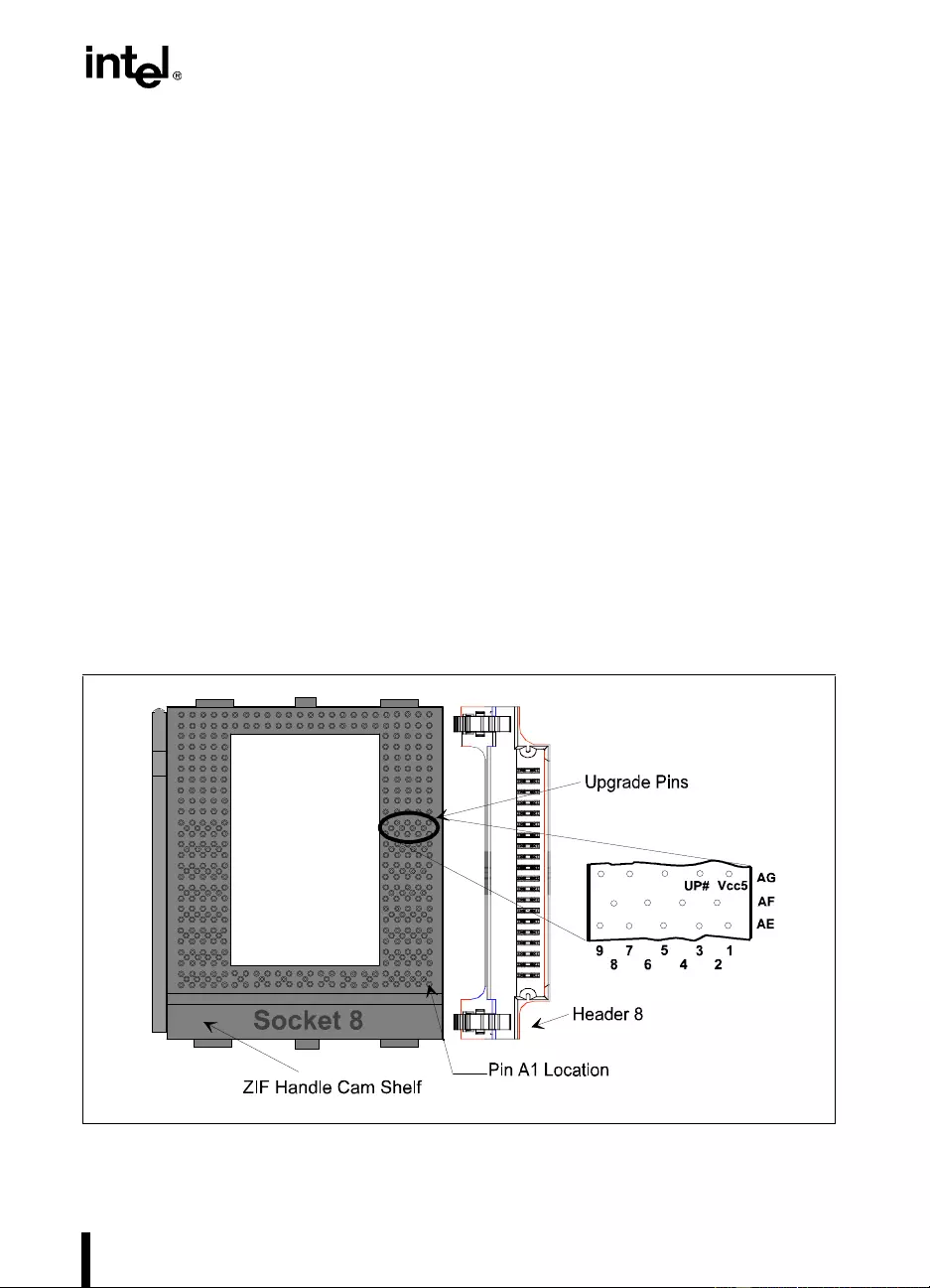

- Figure 17-2. OverDrive ® Processor Pinout

- Figure 17-3. OverDrive ® Processor Envelope Dimensions

- Figure 17-4. Space Requirements for the OverDrive ® Processor

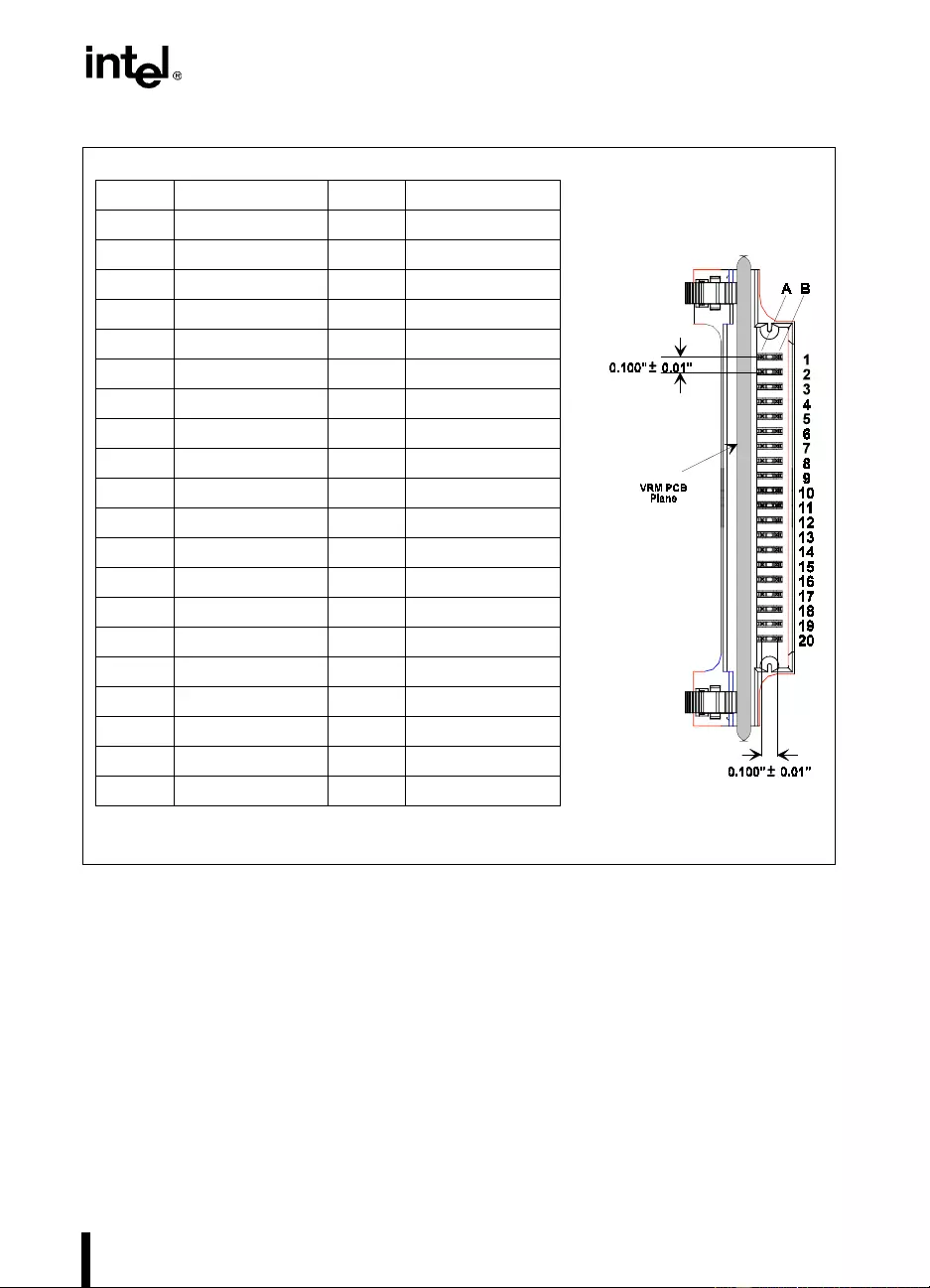

- Figure 17-5. Header 8 Pinout

- Figure 17-6. OverDrive ® Voltage Regulator Module Envelope

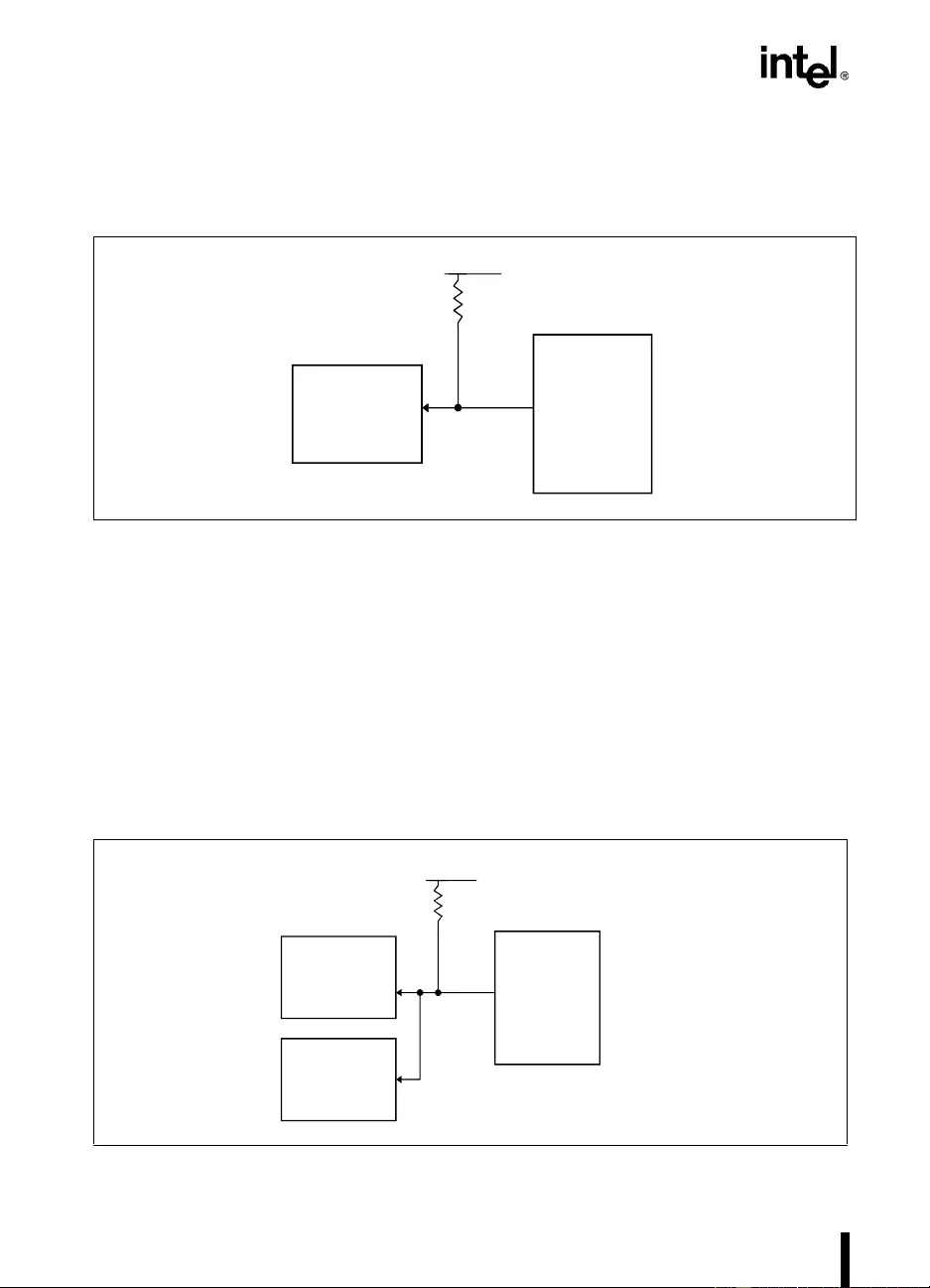

- Figure 17-7. Upgrade Presence Detect Schematic - Case 1

- Figure 17-8. Upgrade Presence Detect Schematic - Case 2

- Figure 17-9. Upgrade Presence Detect Schematic - Case 3

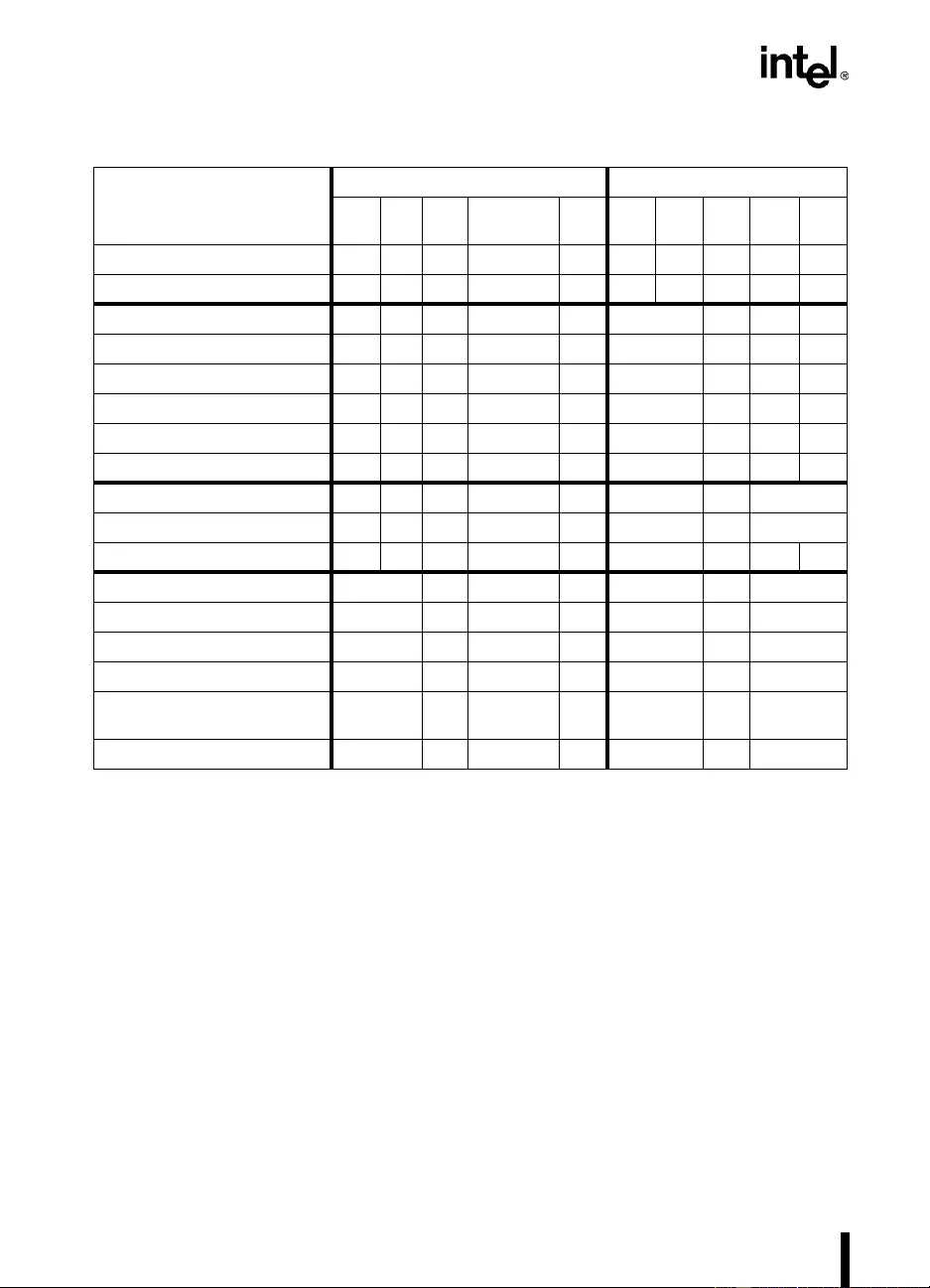

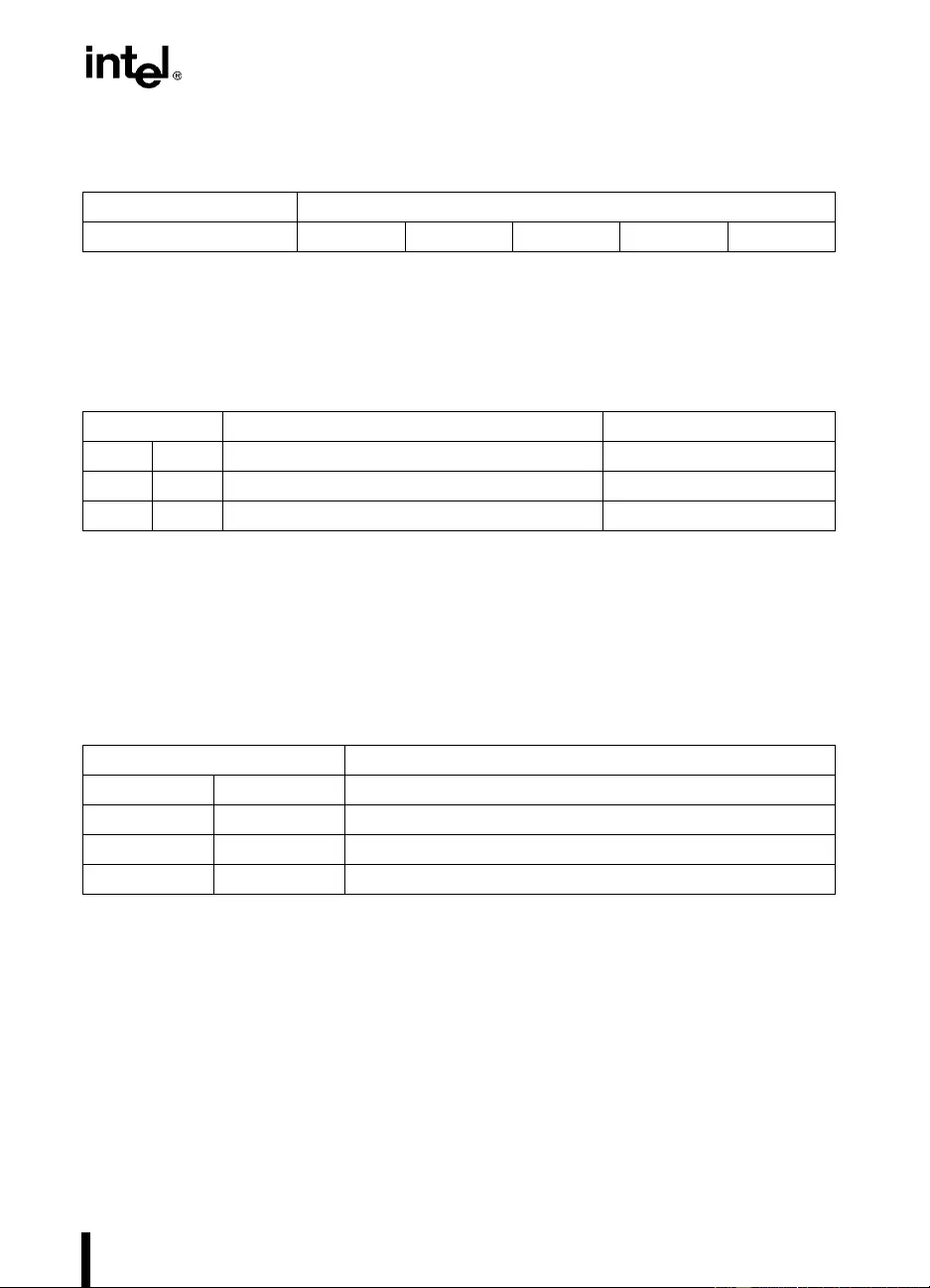

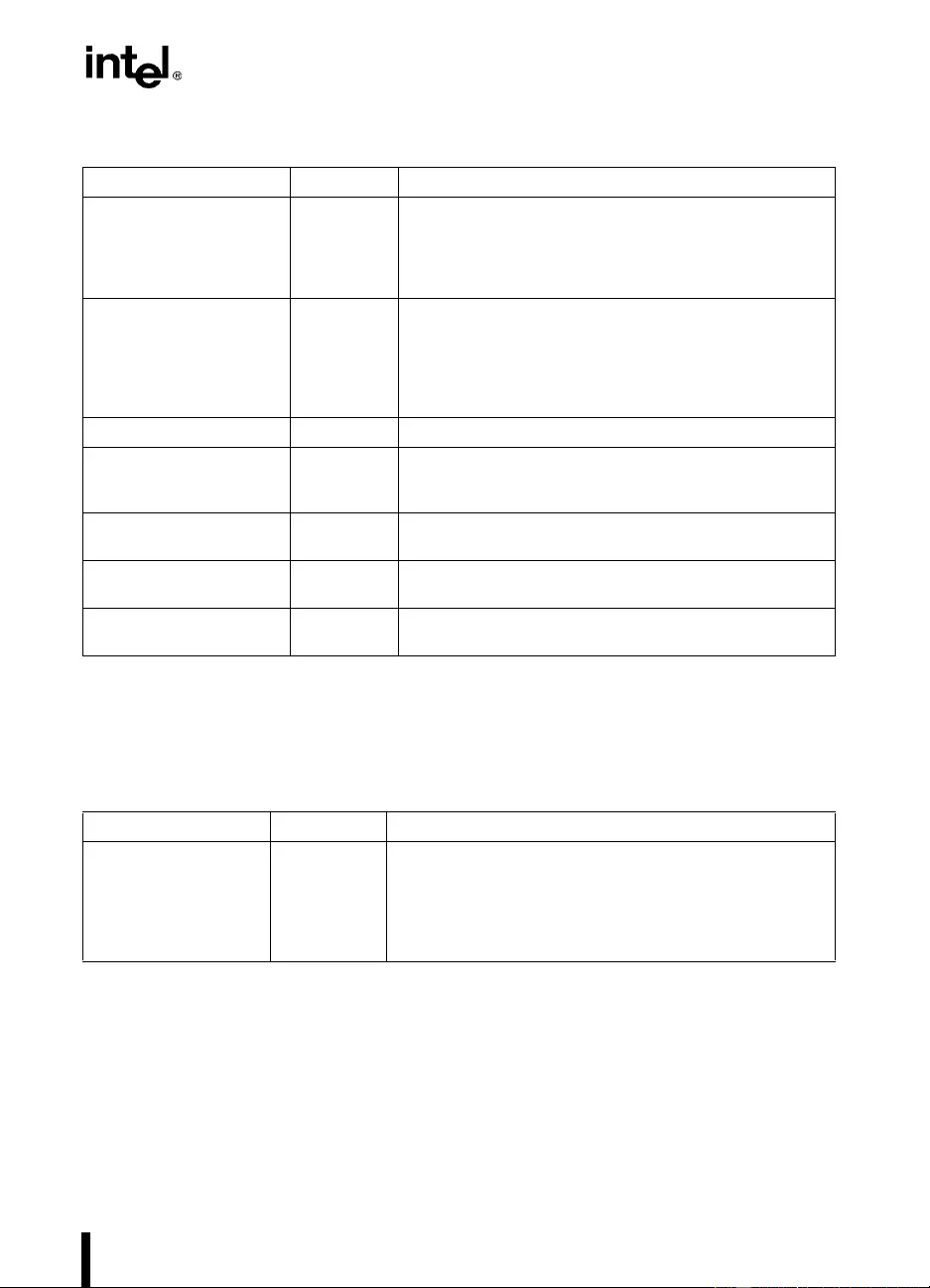

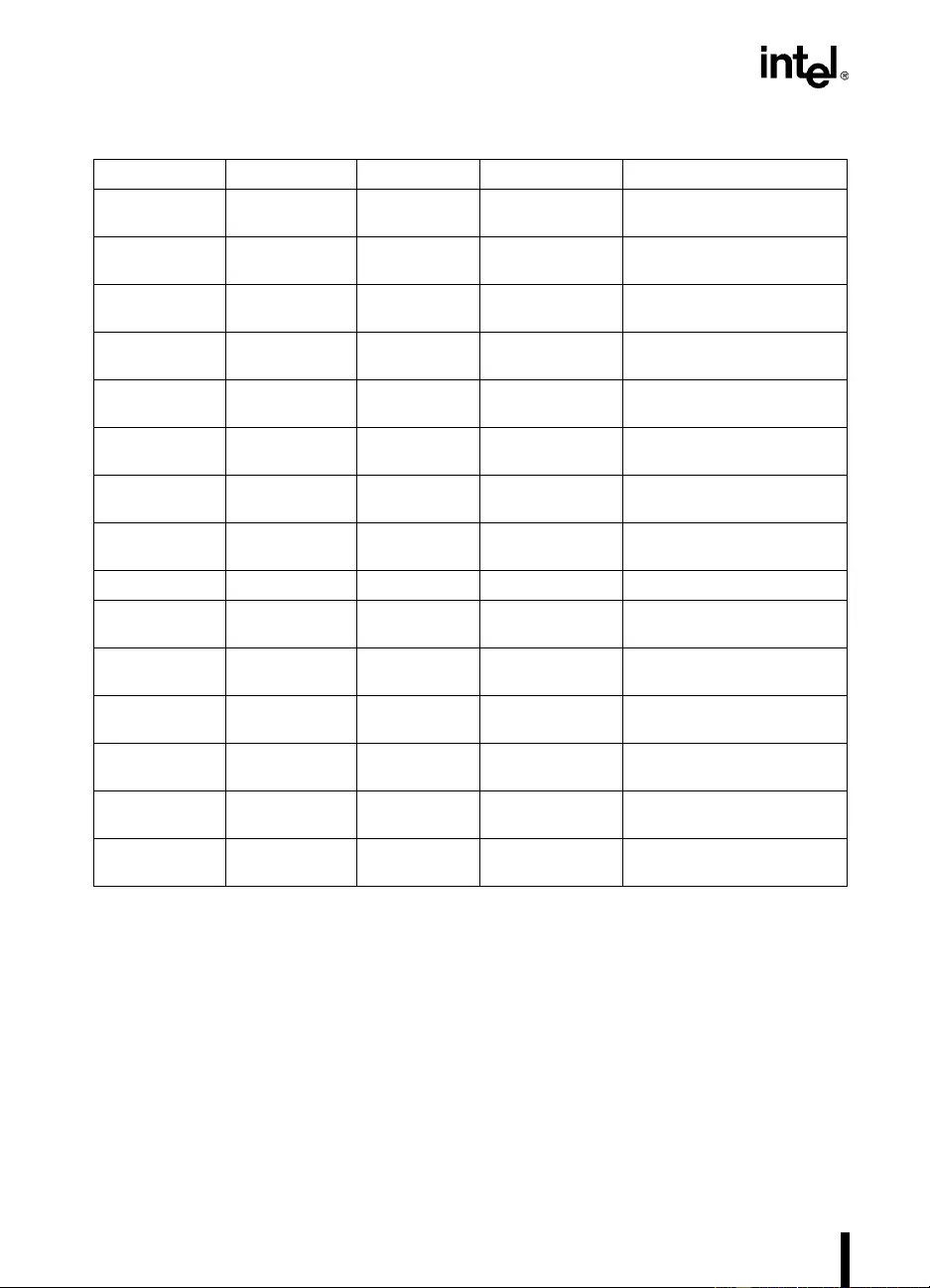

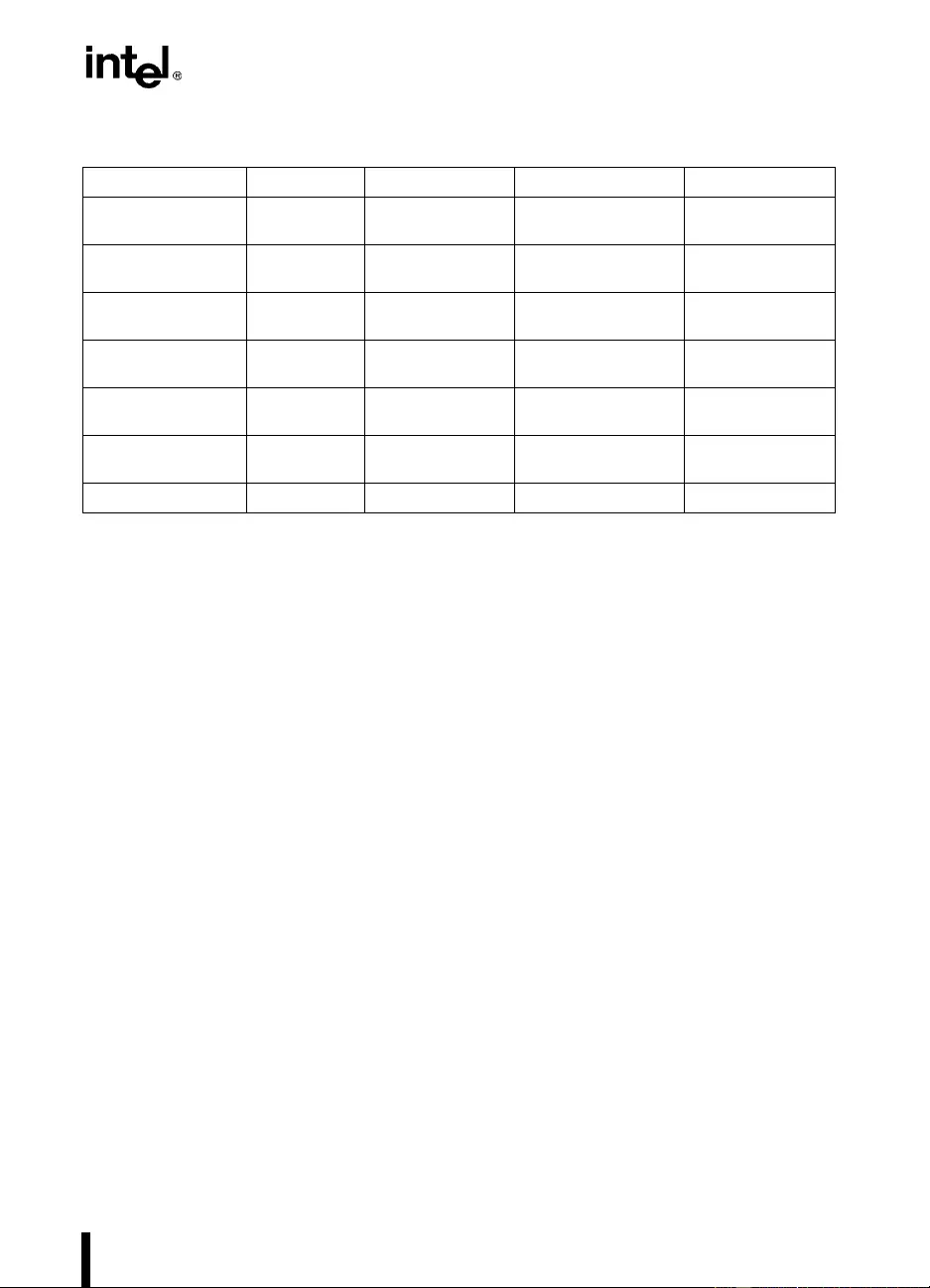

- TABLES

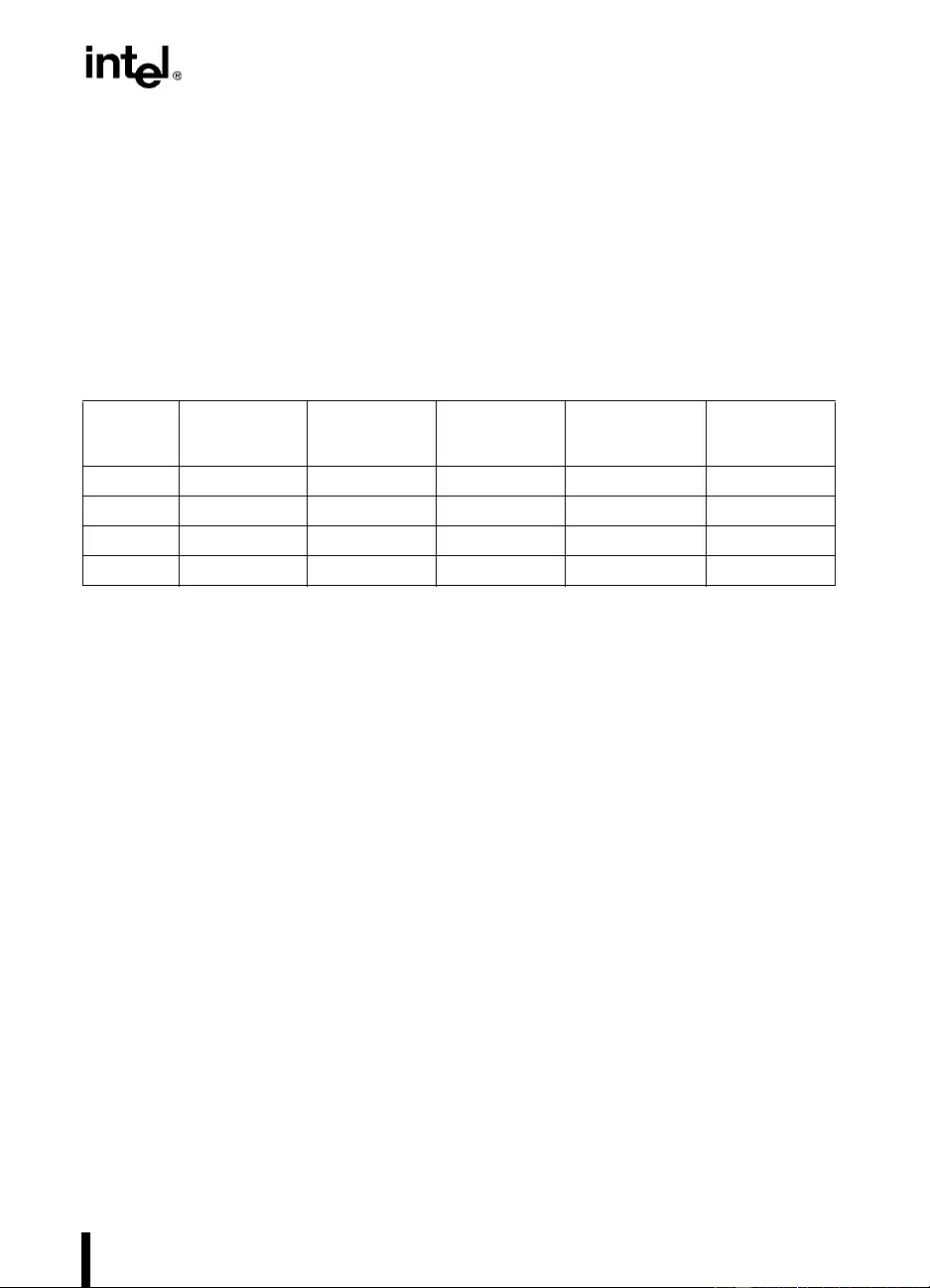

- Table 3-1. Burst Order Used For Pentium ® Pro Processor Bus Line Transfers

- Table 3-2. Execution Control Signals

- Table 3-3. Arbitration Phase Signals

- Table 3-4. Request Signals

- Table 3-5. Transaction Types Defined by REQa#/REQb# Signals

- Table 3-6. Address Space Size

- Table 3-7. Length of Data Transfer

- Table 3-8. Memory Range Register Signal Encoding

- Table 3-9. DID[7:0]# Encoding

- Table 3-10. Special Transaction Encoding on Byte Enables

- Table 3-11. Extended Function Pins

- Table 3-12. Error Phase Signals

- Table 3-13. Snoop Signals

- Table 3-14. Response Signals

- Table 3-15. Transaction Response Encodings

- Table 3-16. Data Phase Signals

- Table 3-17. Error Signals

- Table 3-18. PC Compatibility Signals

- Table 3-19. Diagnostic Support Signals

- Table 4-1. HIT# and HITM# During Snoop Phase

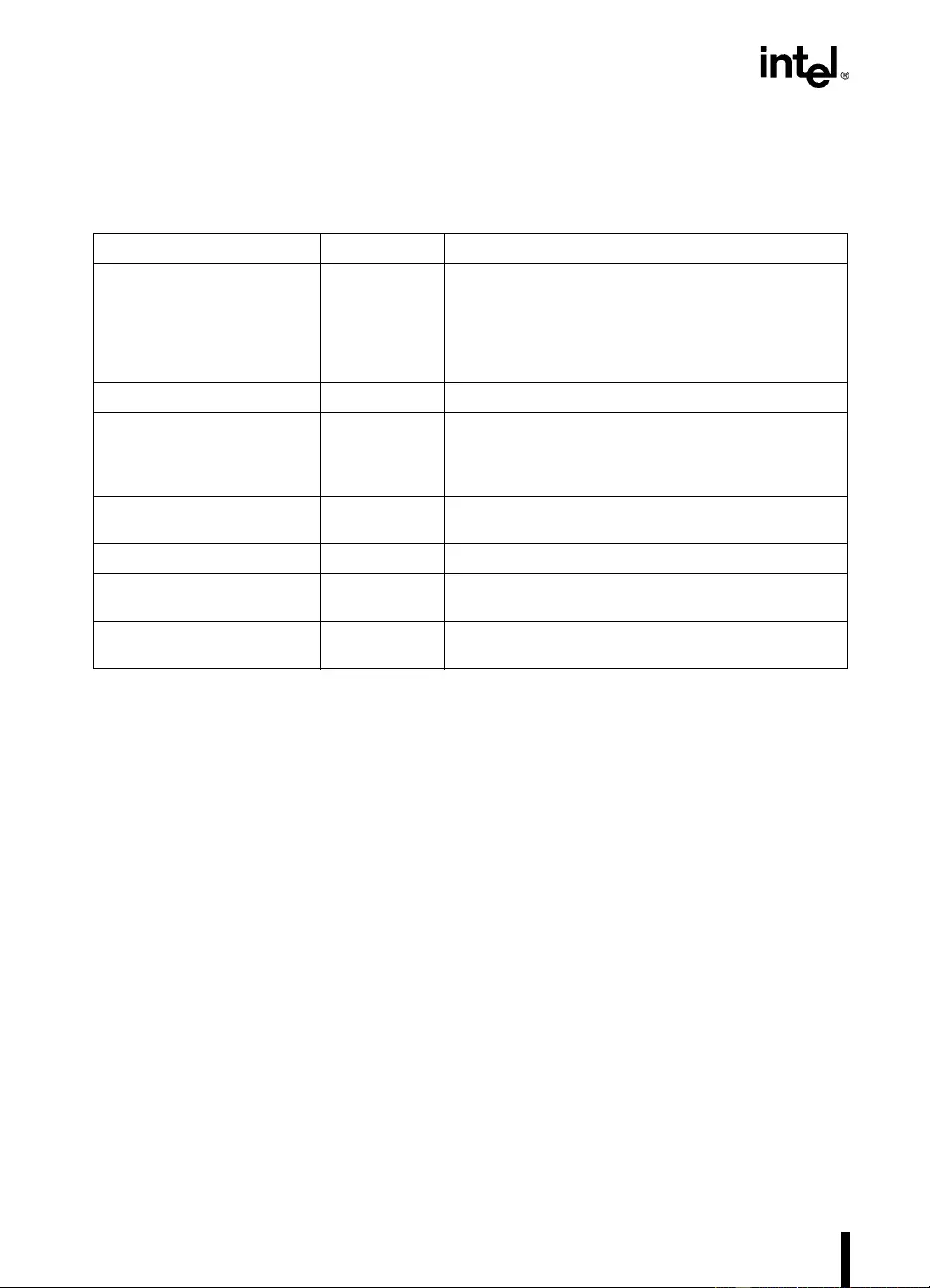

- Table 4-2. Response Phase Encodings

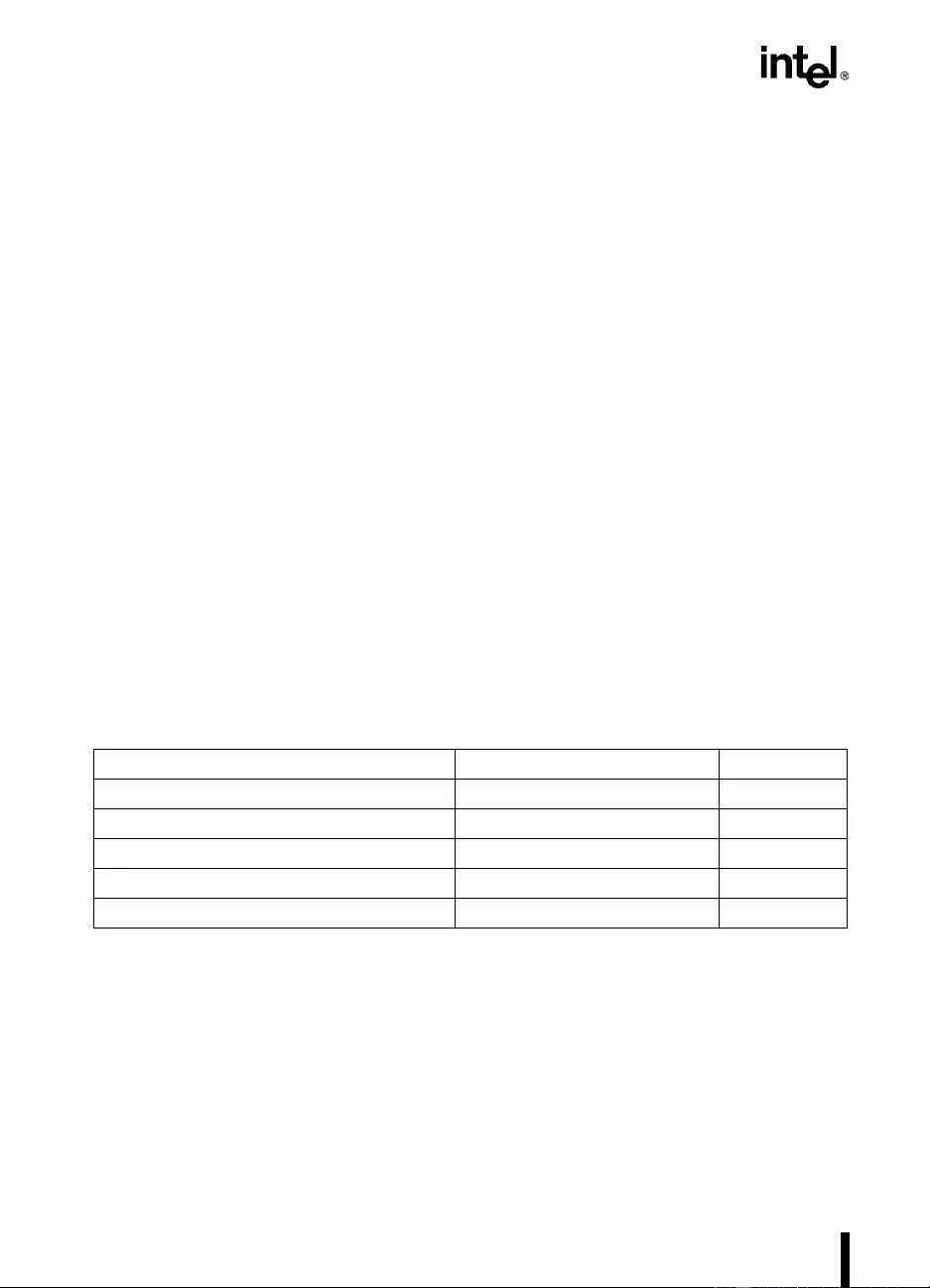

- Table 6-1. Pentium ® Pro Processor Architecture Memory Types

- Table 8-1. Direct Bus Signal Protection

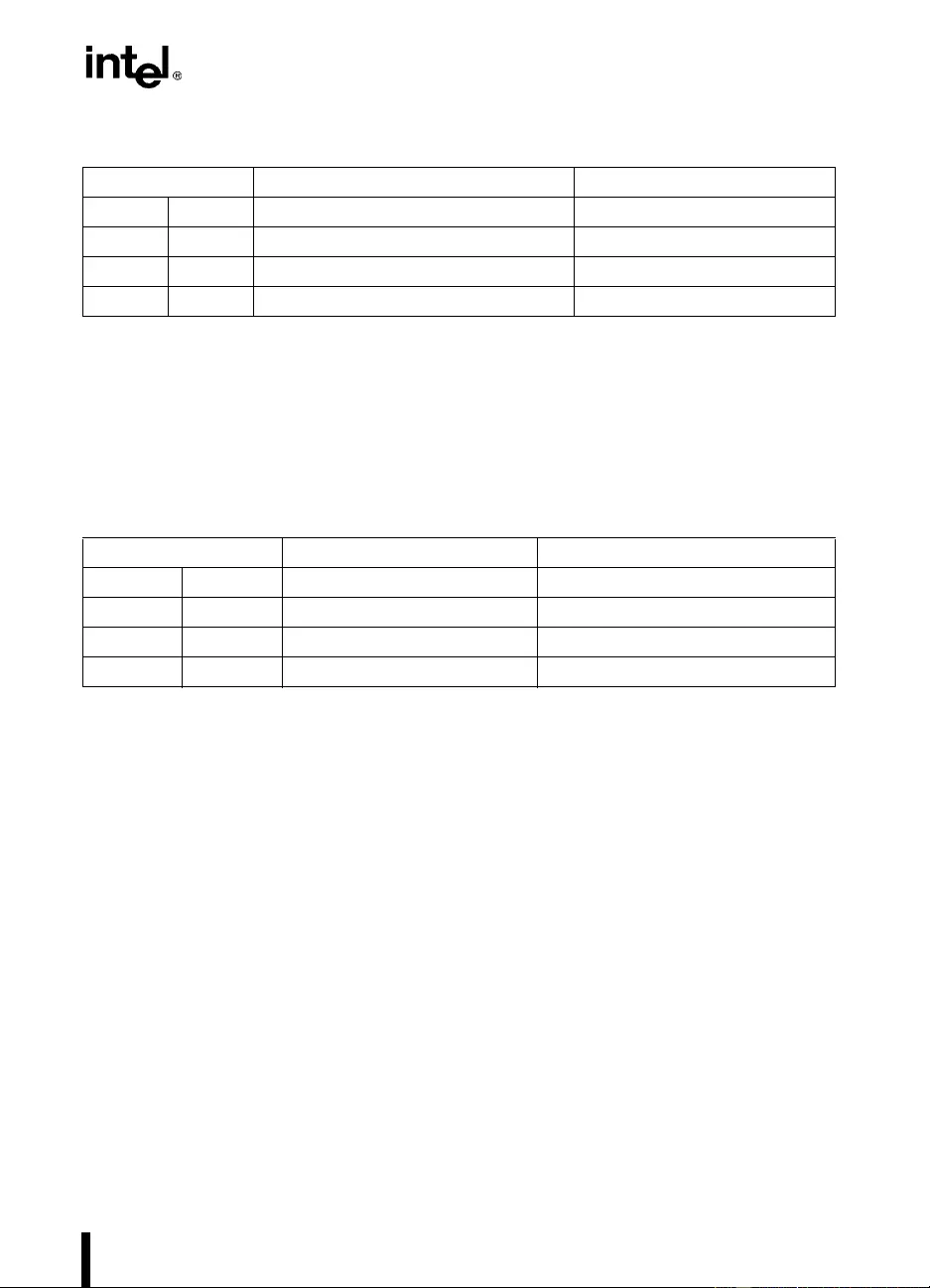

- Table 9-1. APIC Cluster ID Configuration for the Pentium ® Pro Processor

- Table 9-2. BREQ[3:0]# Interconnect

- Table 9-3. Arbitration ID Configuration

- Table 9-4. Bus Frequency to Core Frequency Ratio Configuration

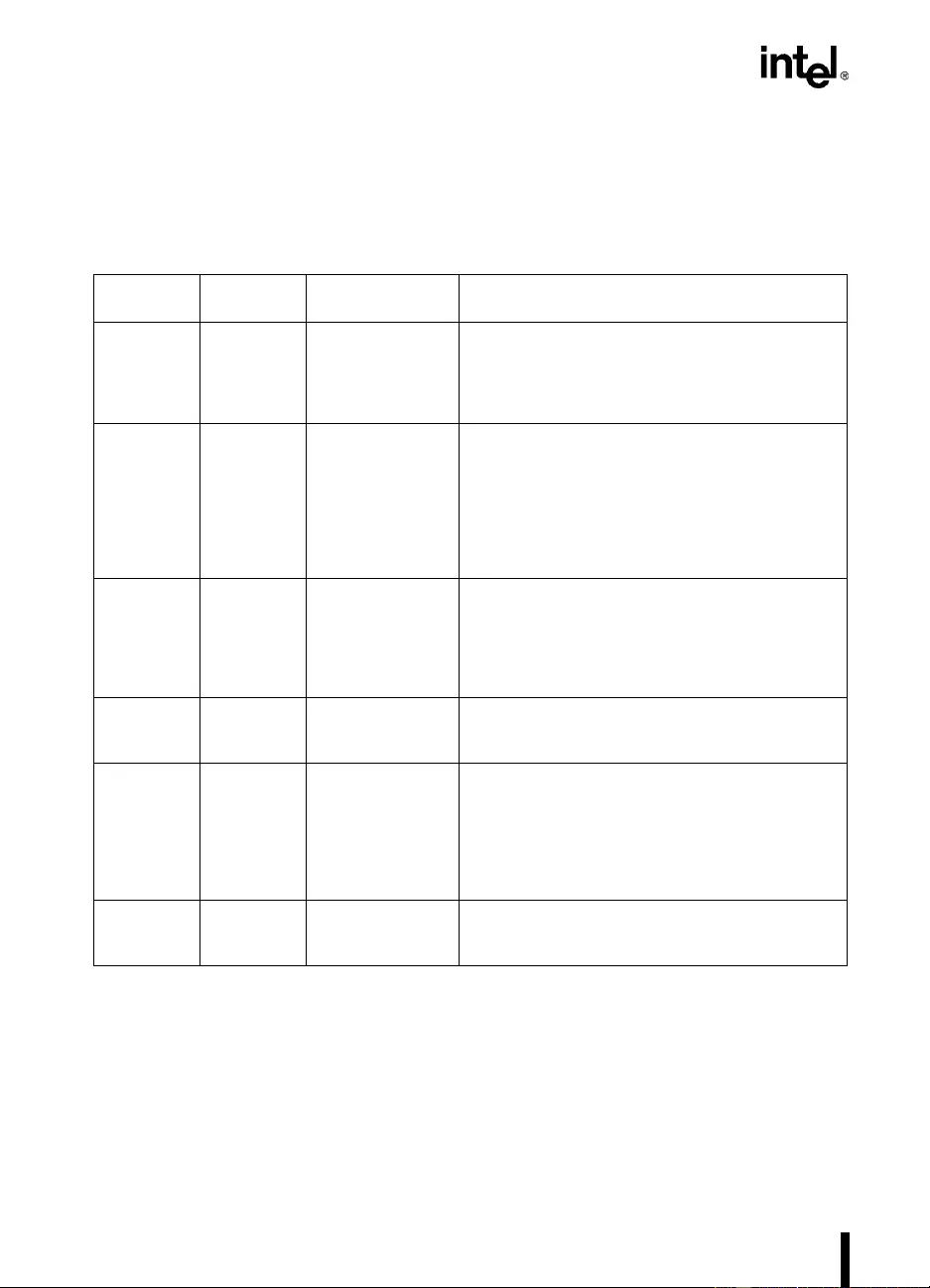

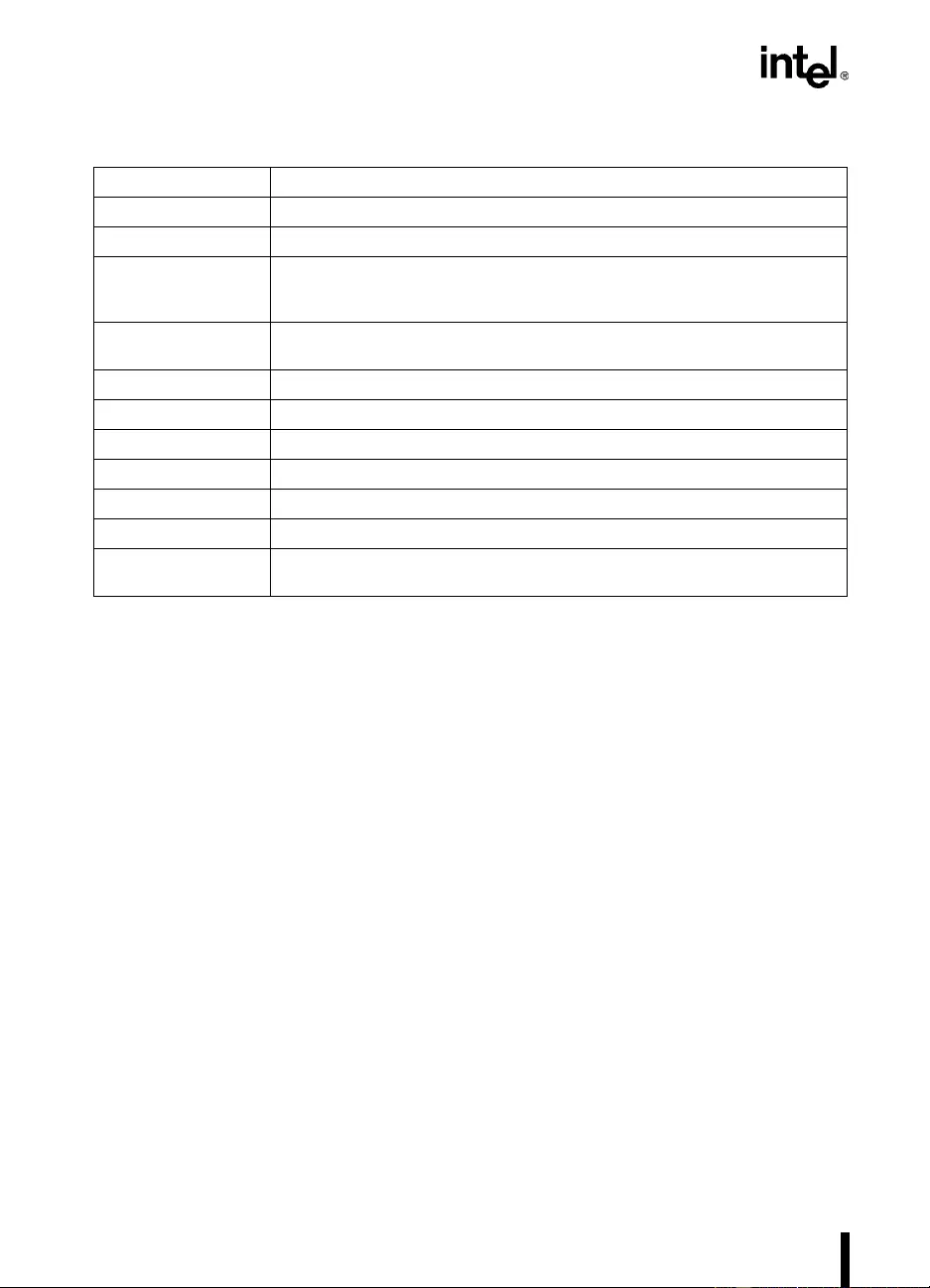

- Table 9-5. Pentium ® Pro Processor Power-on Configuration Register

- Table 9-6. Pentium ® Pro Processor Power-on Configuration Register APIC Cluster ID bit Field

- Table 9-7. Pentium ® Pro Processor Power-on Configuration Register Bus Frequency to Core Frequency Ratio Bit Field

- Table 9-8. Pentium ® Pro Processor Power-on Configuration Register Arbitration ID Configuration

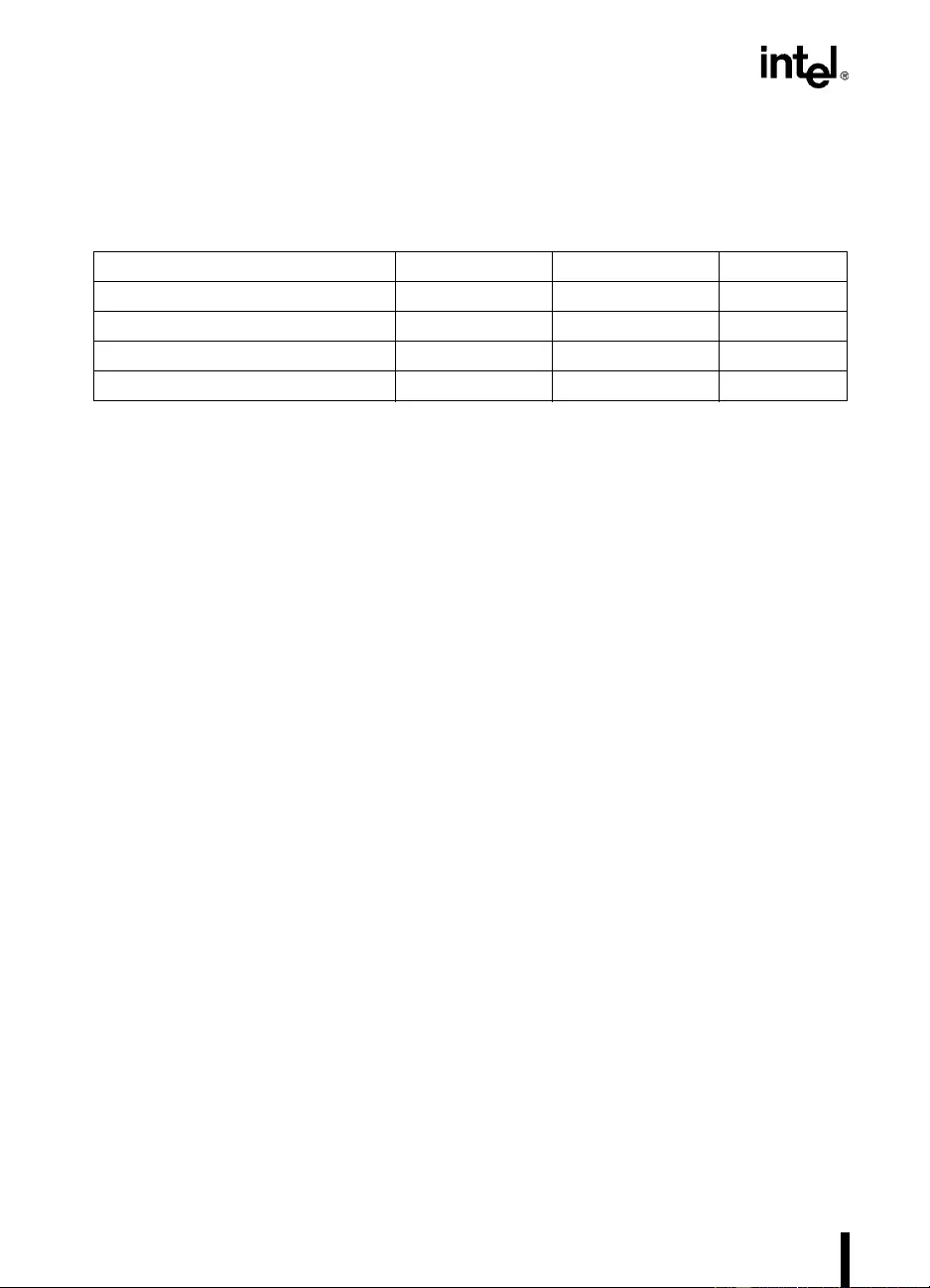

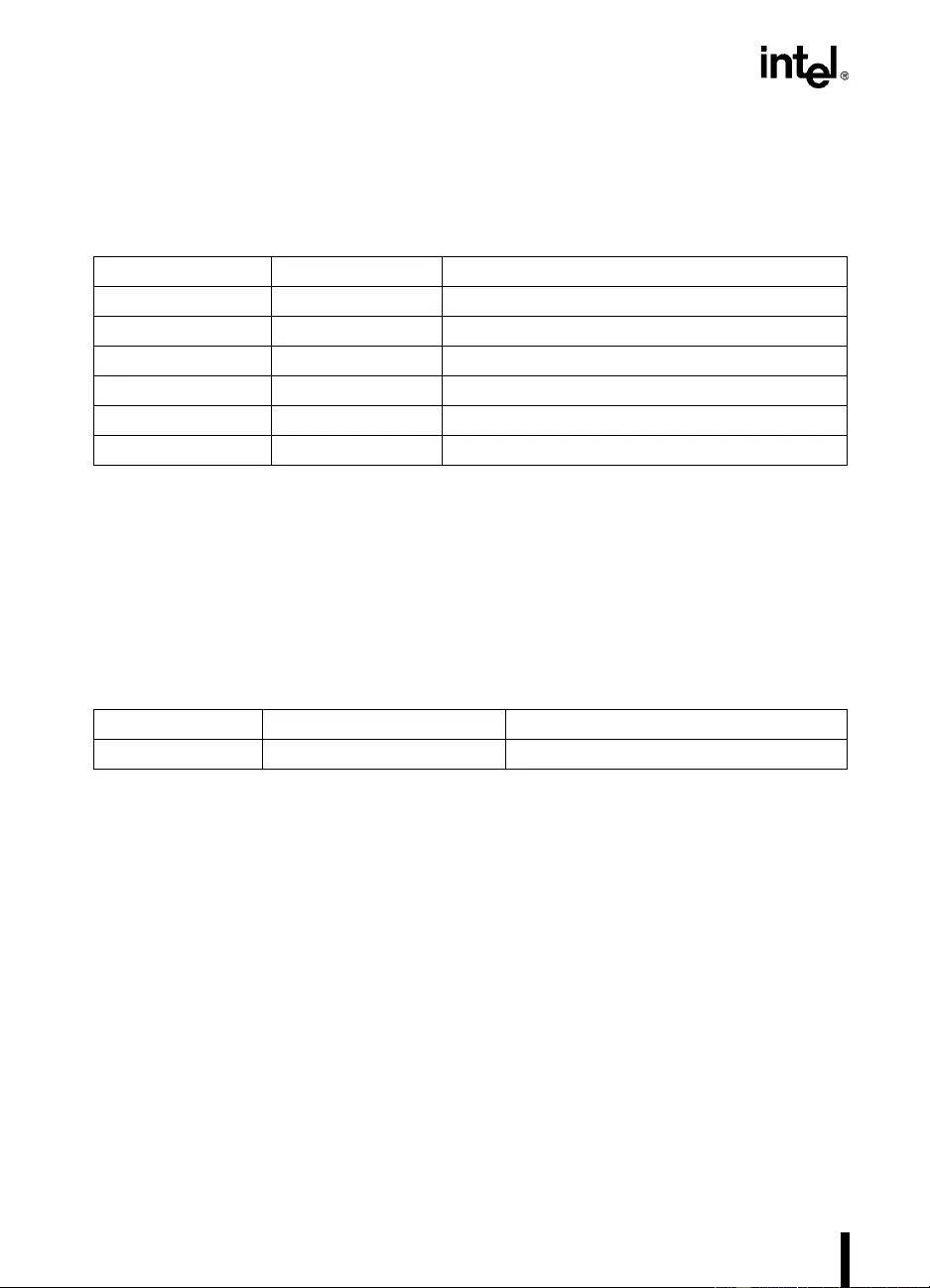

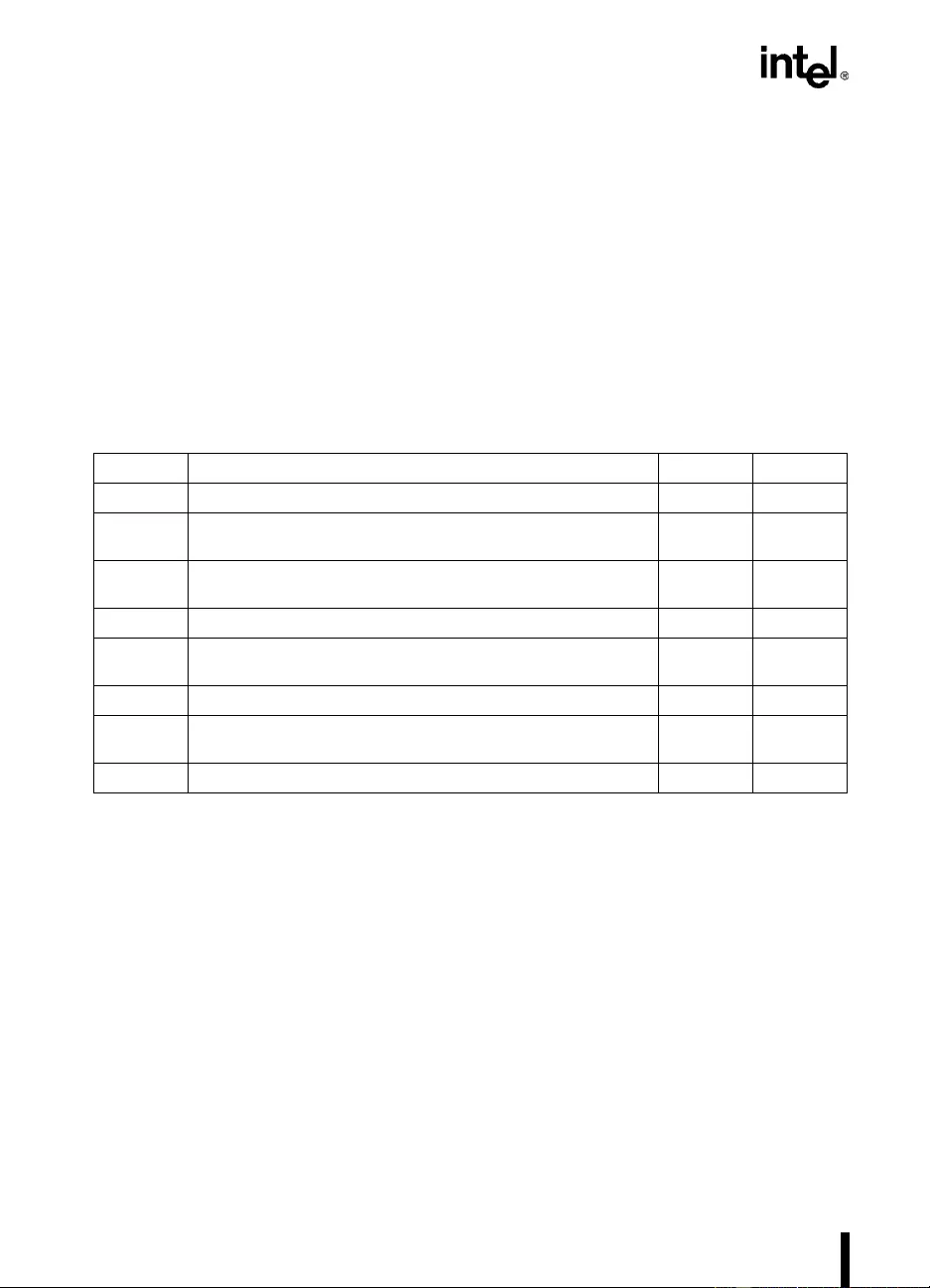

- Table 10-1. 1149.1 Instructions in the Pentium ® Pro Processor TAP

- Table 10-2. TAP Data Registers

- Table 10-3. Device ID Register

- Table 10-4. TAP Reset Actions

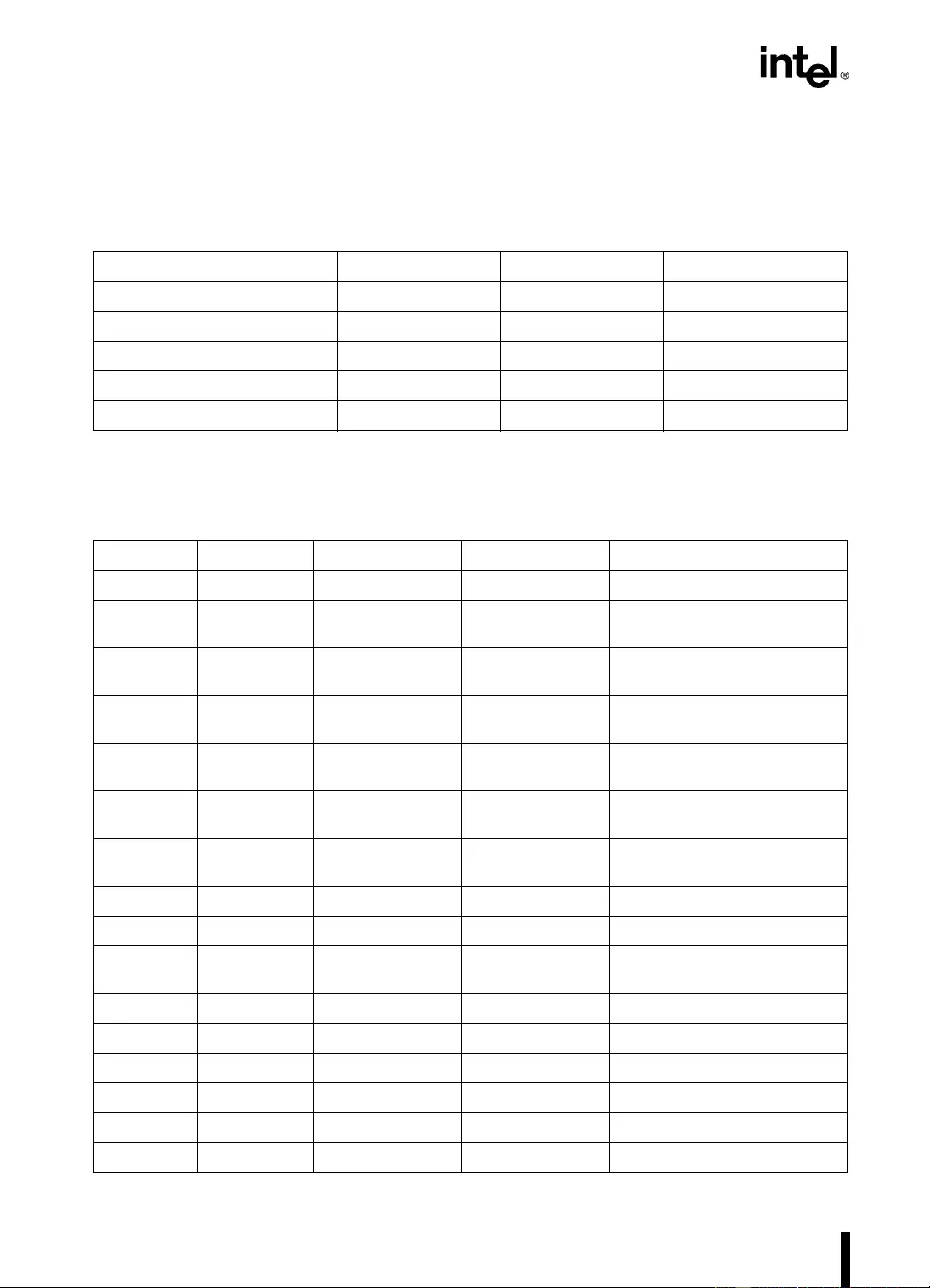

- Table 11-1. Voltage Identification Definition

- Table 11-2. Signal Groups

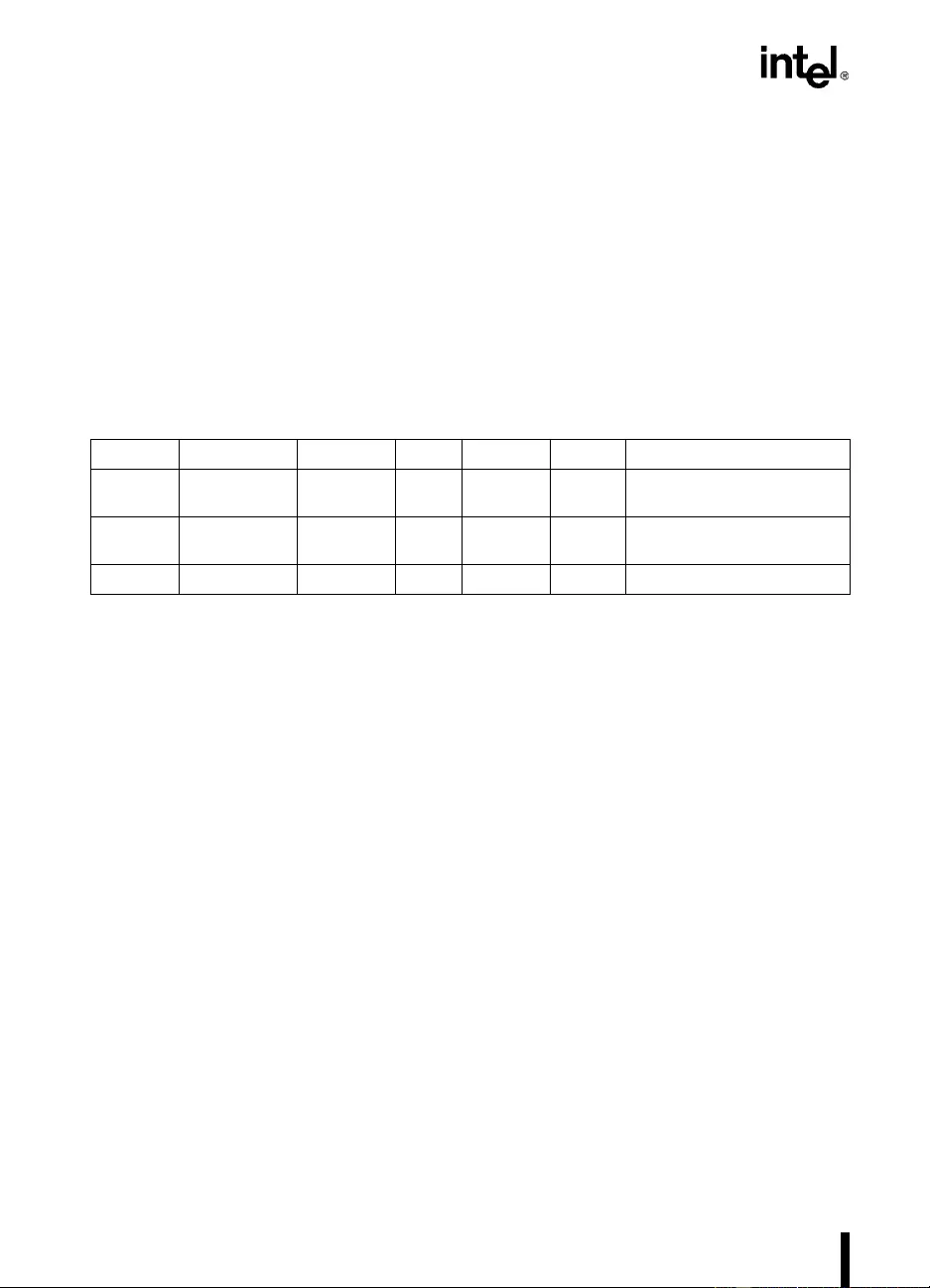

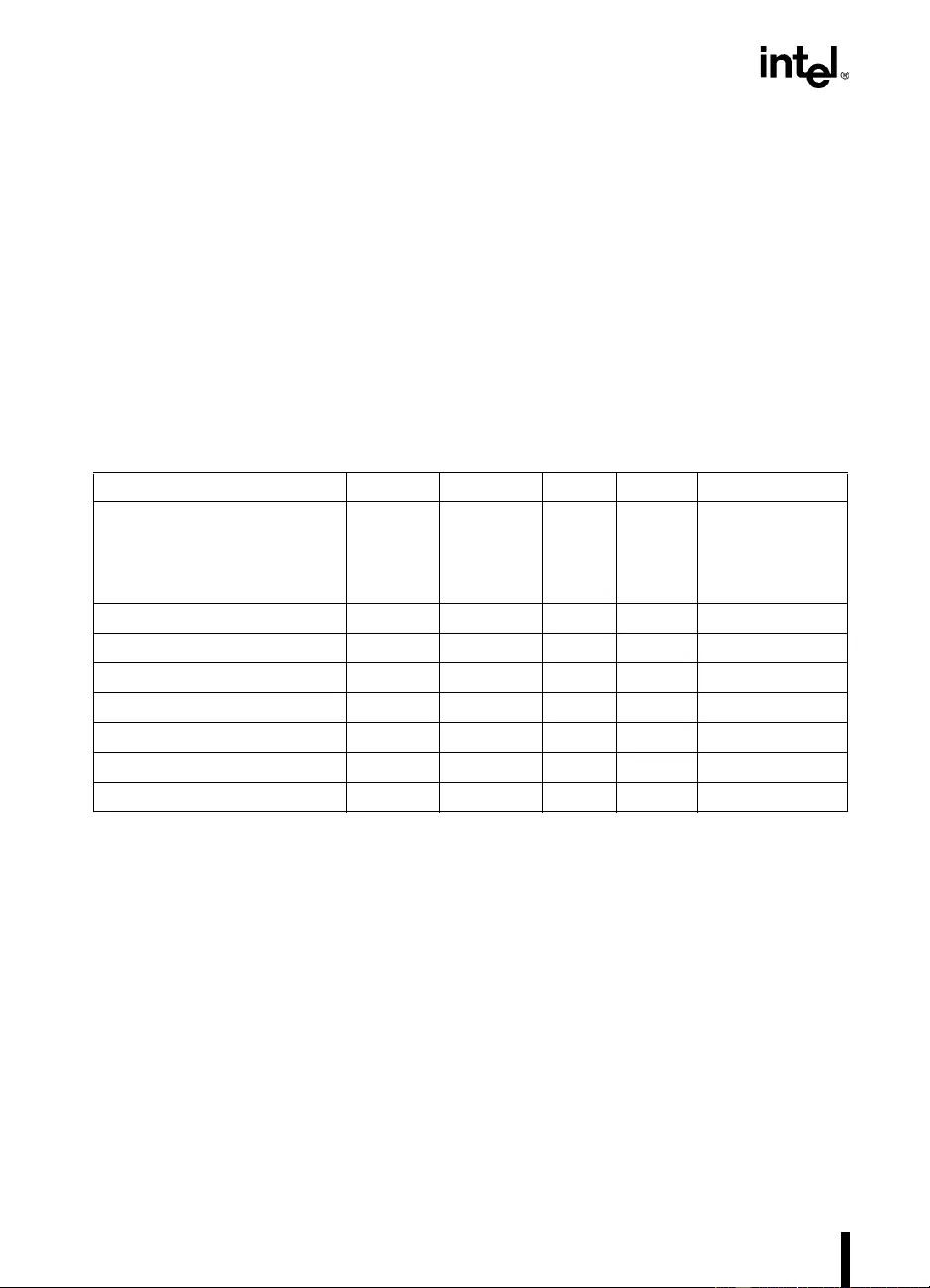

- Table 11-3. Absolute Maximum Ratings

- Table 11-4. Voltage Specification

- Table 11-5. Power Specifications

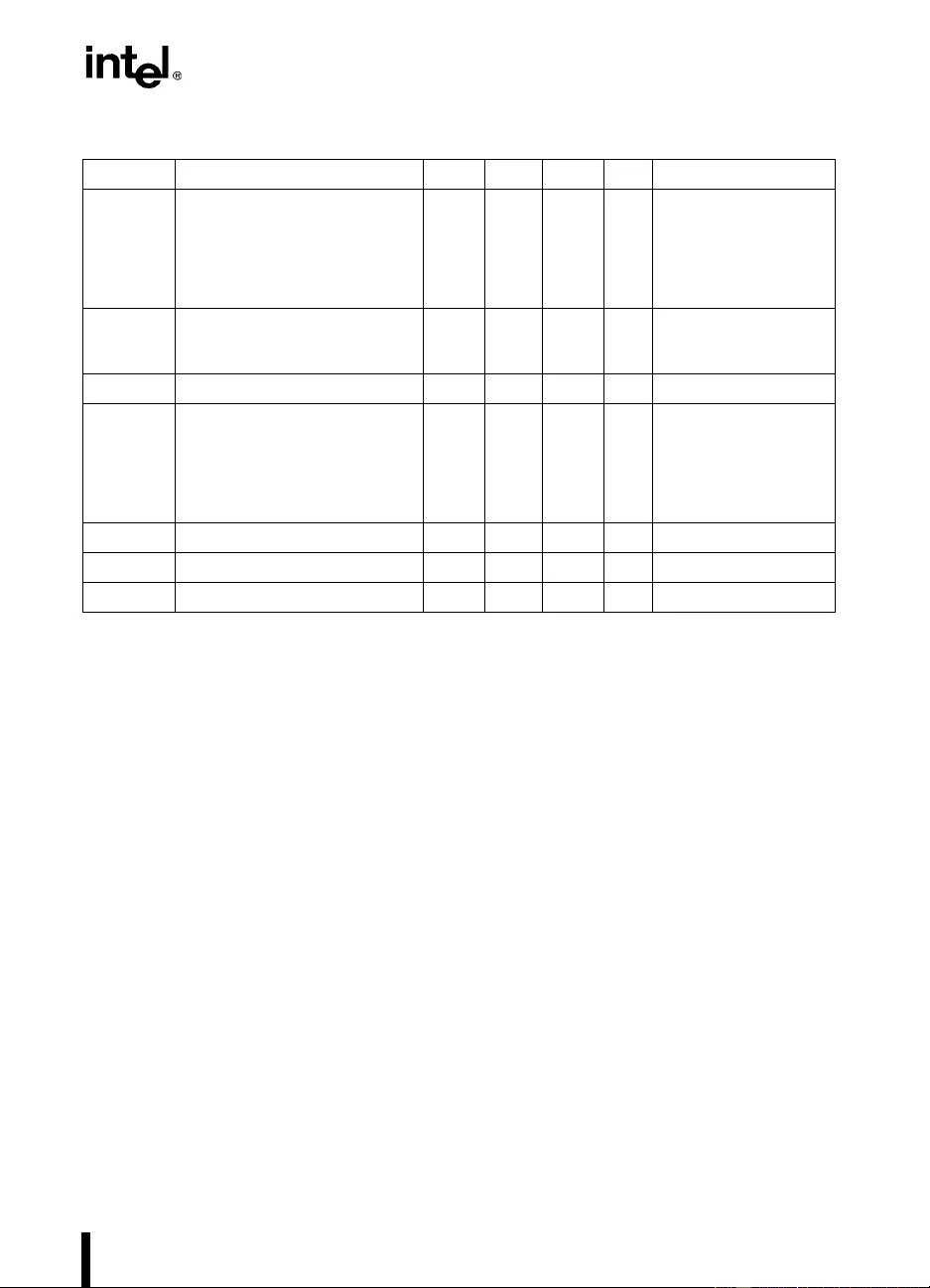

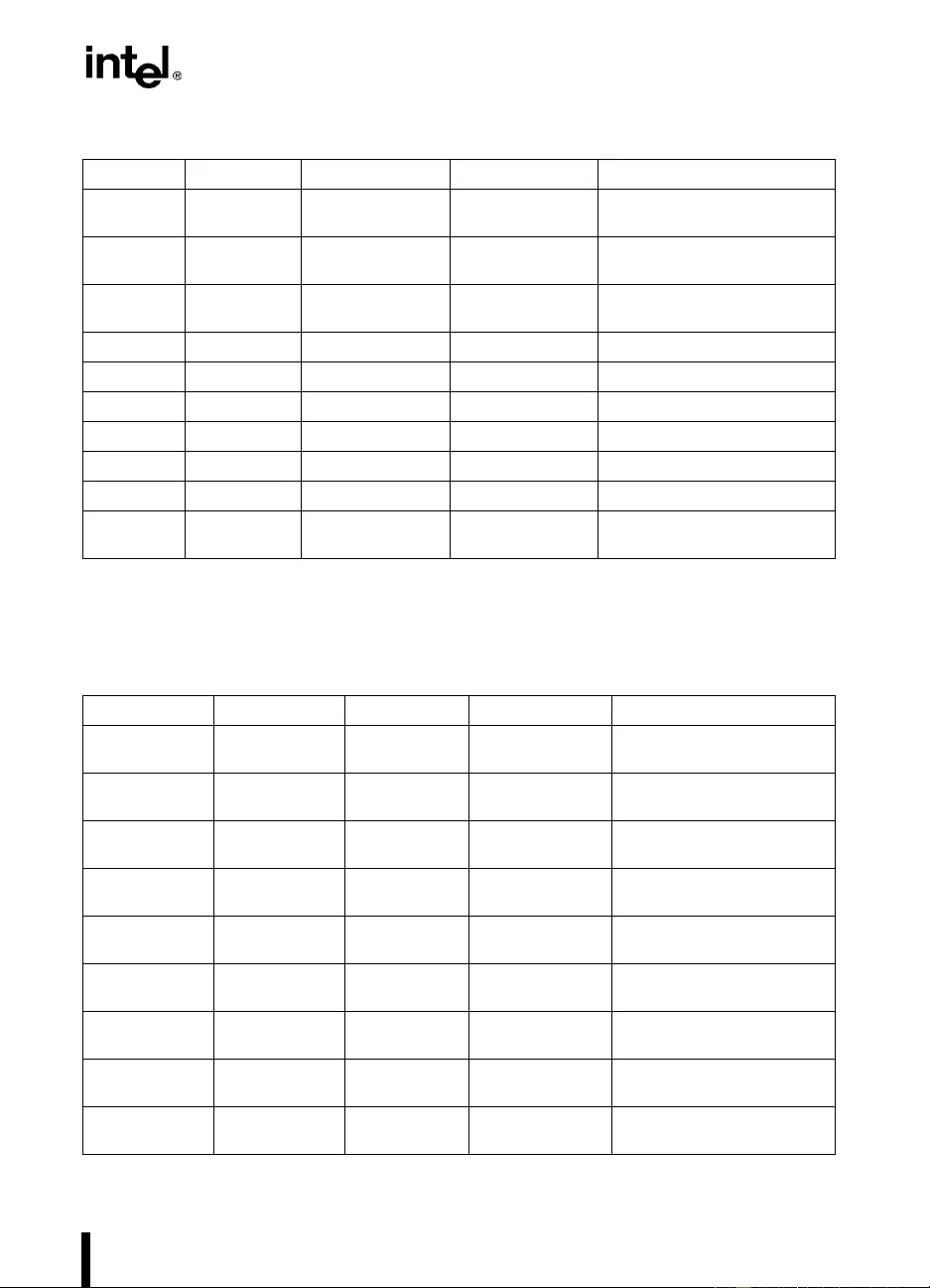

- Table 11-6. GTL+ Signal Groups D.C. Specifications

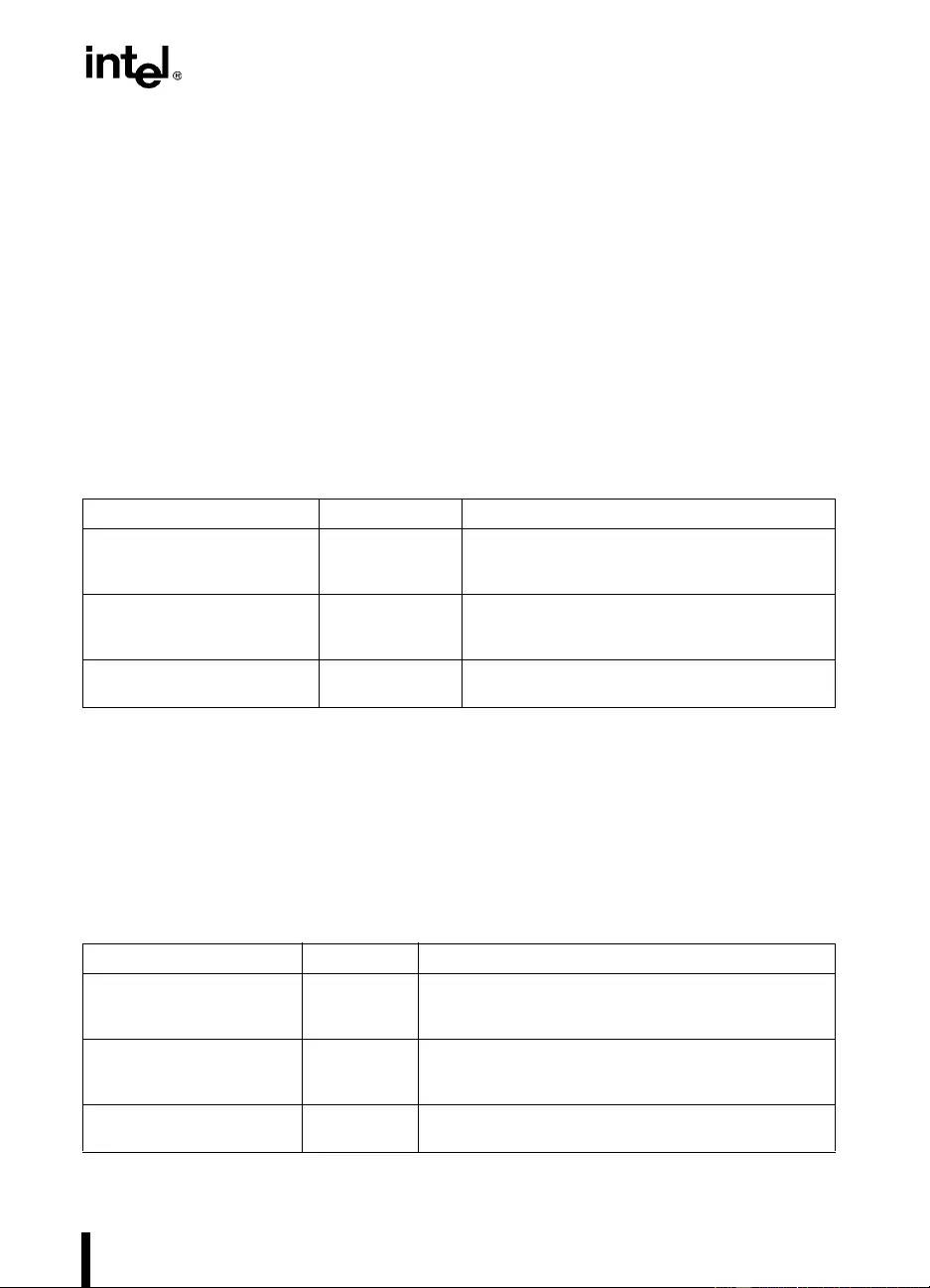

- Table 11-7. Non-GTL+ Signal Groups D.C. Specifications

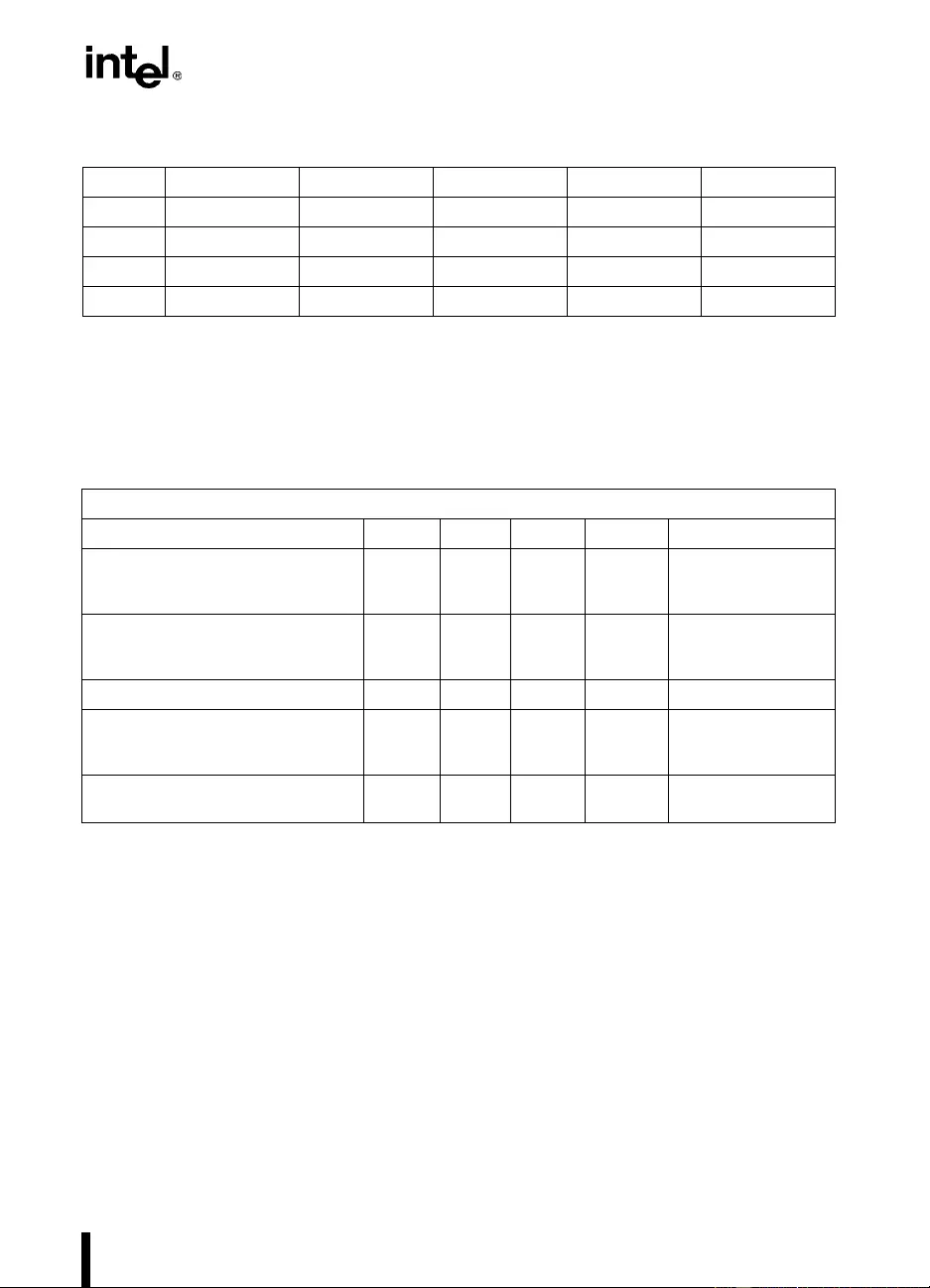

- Table 11-8. GTL+ Bus D.C. Specifications

- Table 11-9. Bus Clock A.C. Specifications

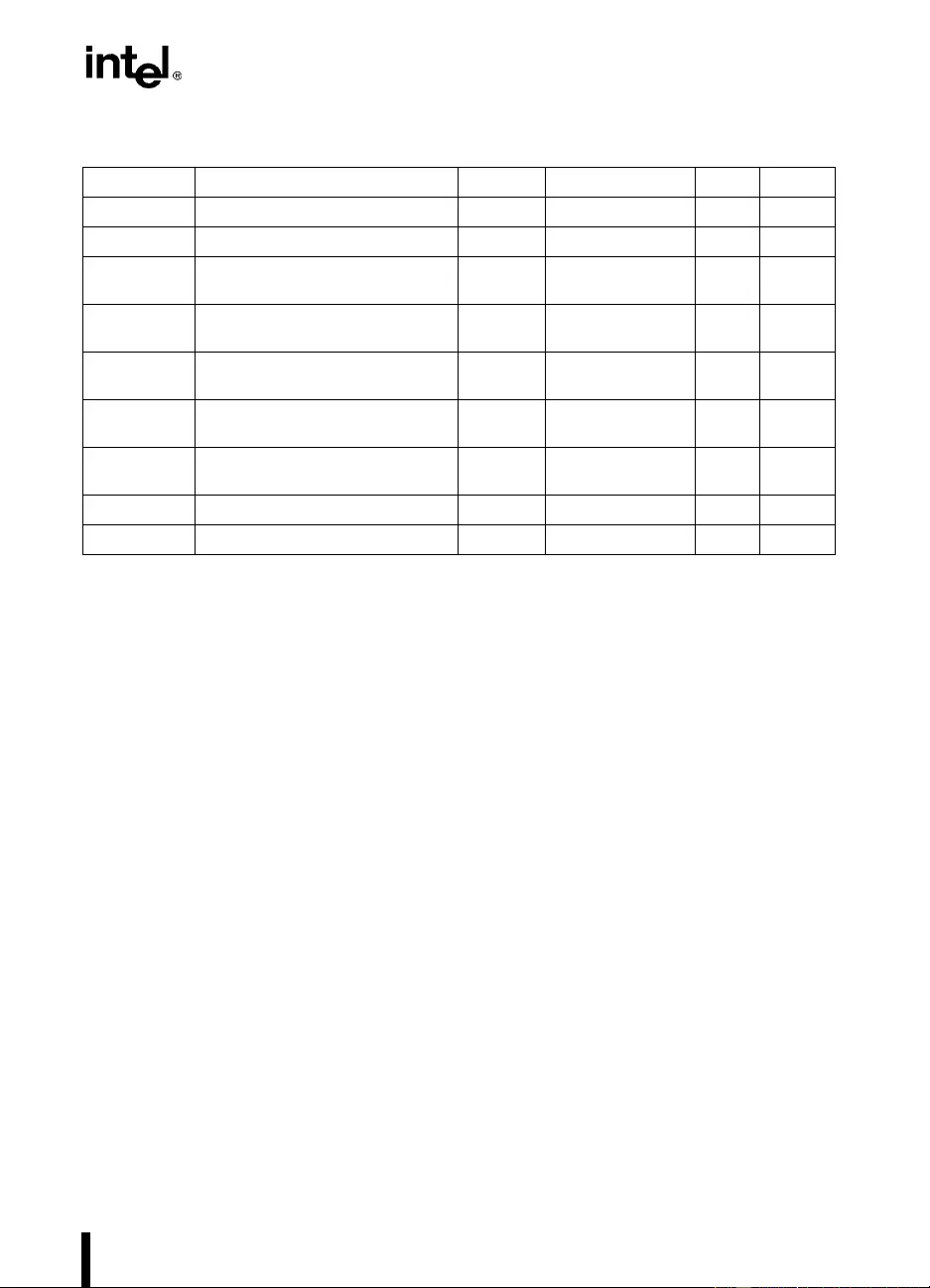

- Table 11-10. Supported Clock Ratios

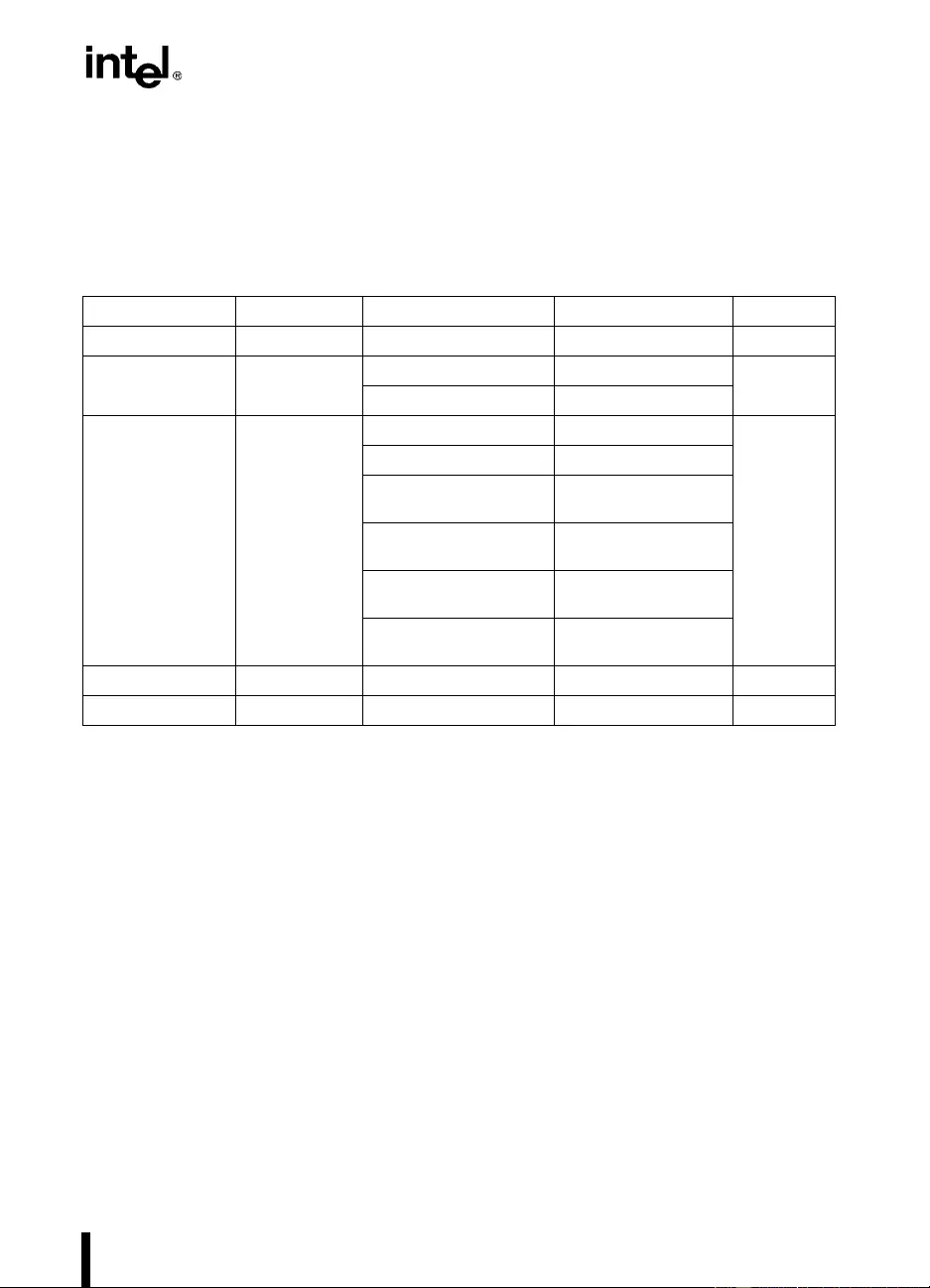

- Table 11-11. GTL+ Signal Groups A.C. Specifications

- Table 11-12. GTL+ Signal Groups Ringback Tolerance

- Table 11-13. 3.3V Tolerant Signal Groups A.C. Specifications

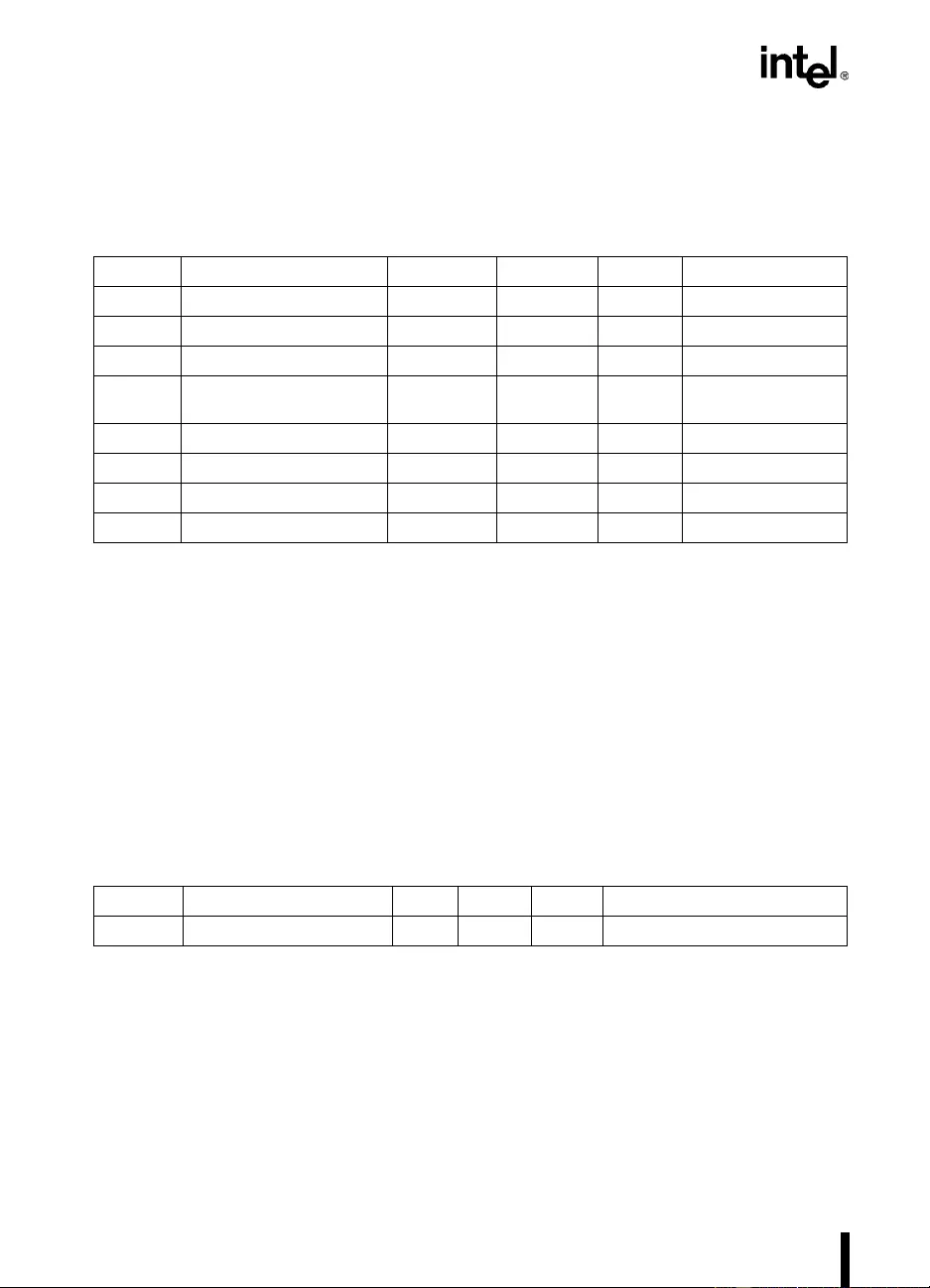

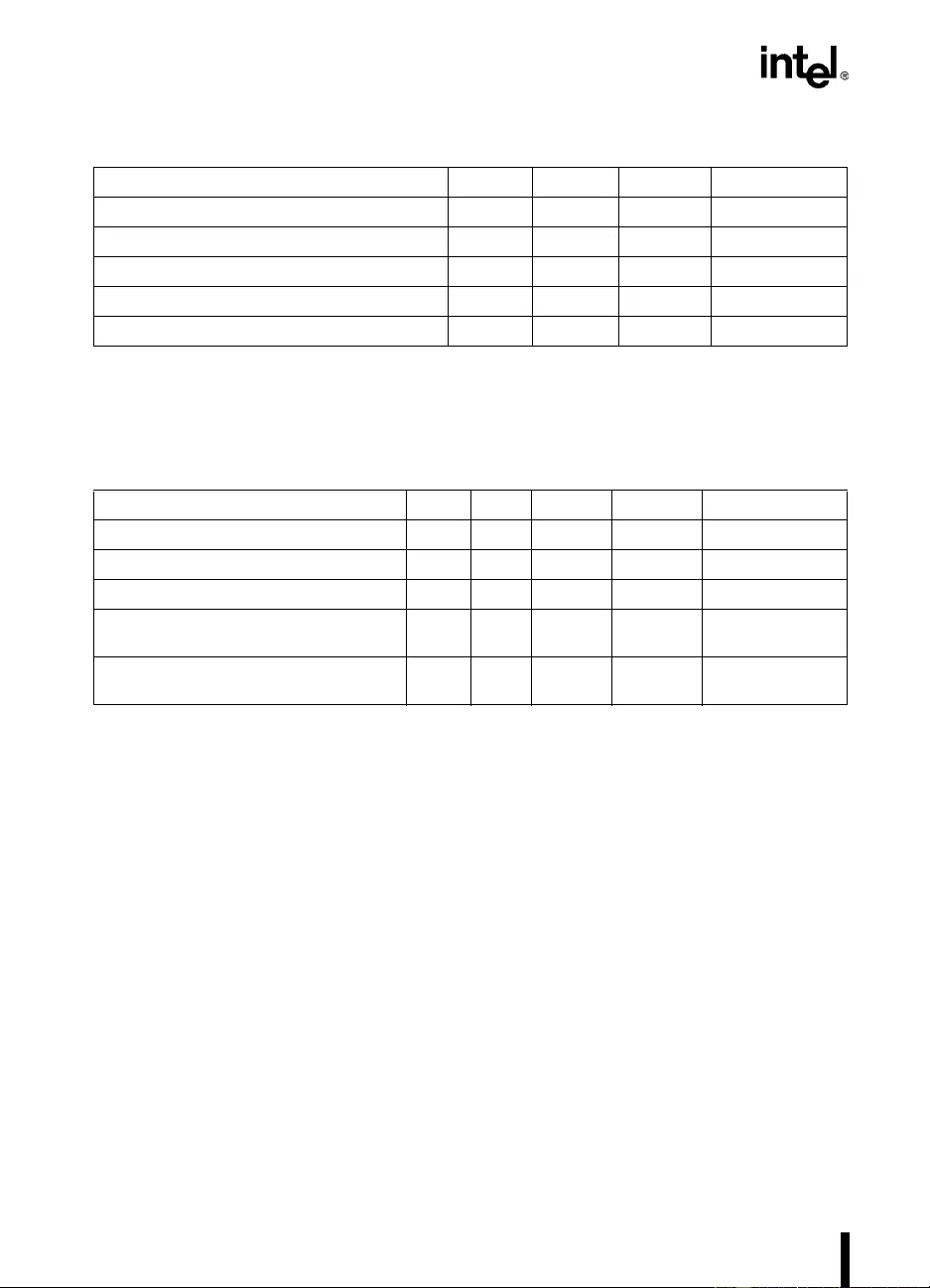

- Table 11-14. Reset Conditions A.C. Specifications

- Table 11-15. APIC Clock and APIC I/O A.C. Specifications

- Table 11-16. Boundary Scan Interface A.C. Specifications

- Table 11-17. Flexible Motherboard (FMB) Power Recommendations

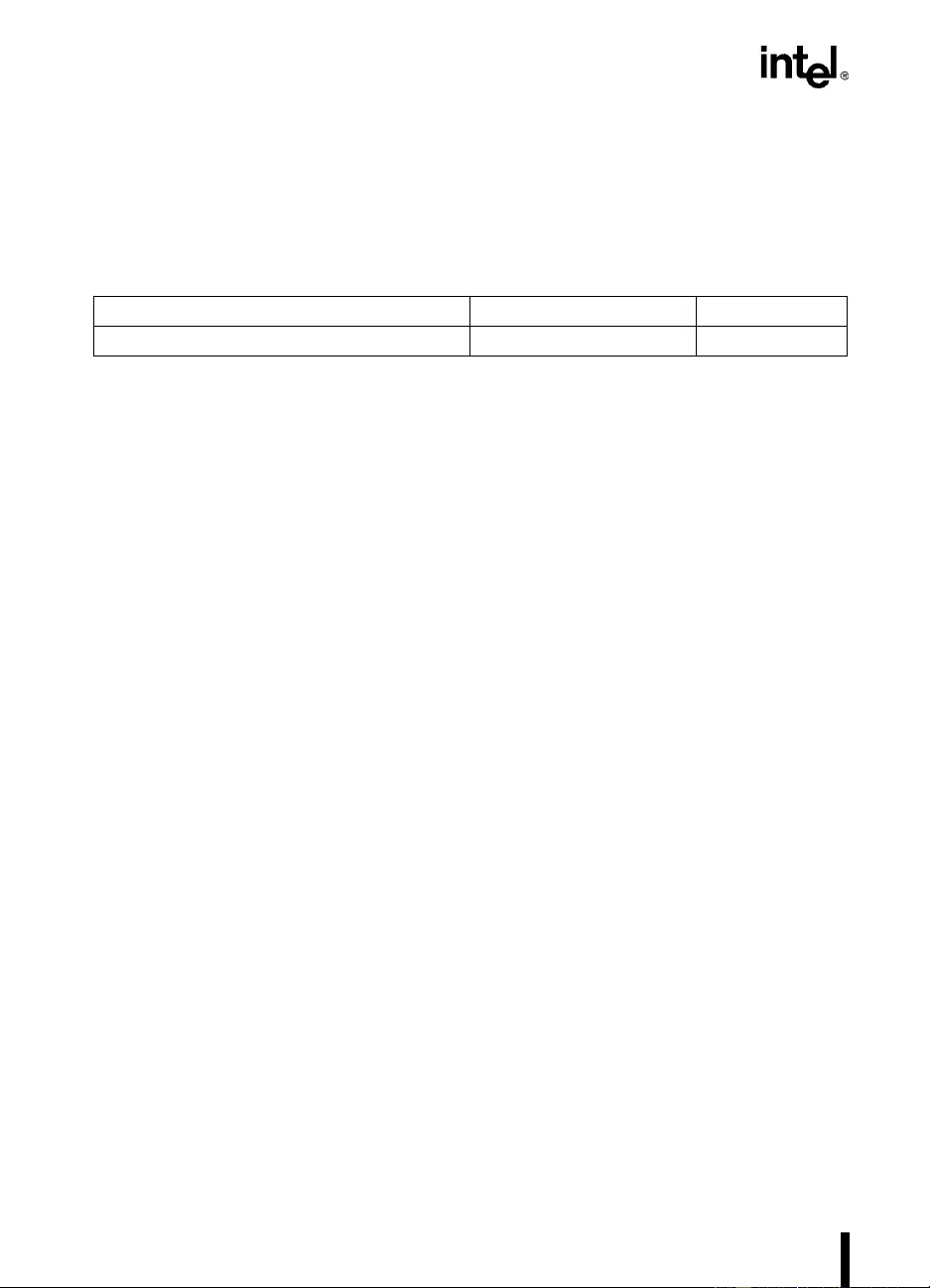

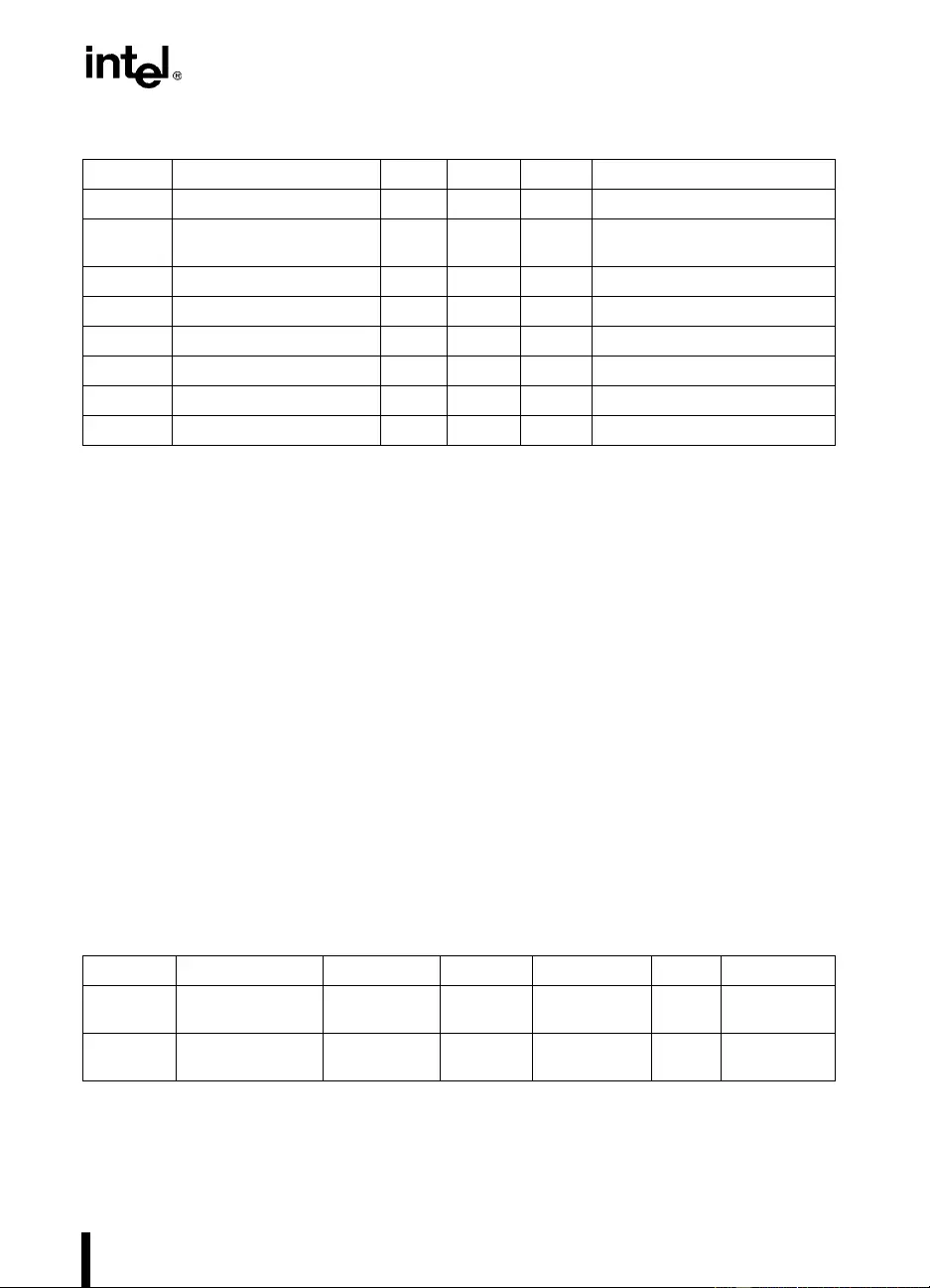

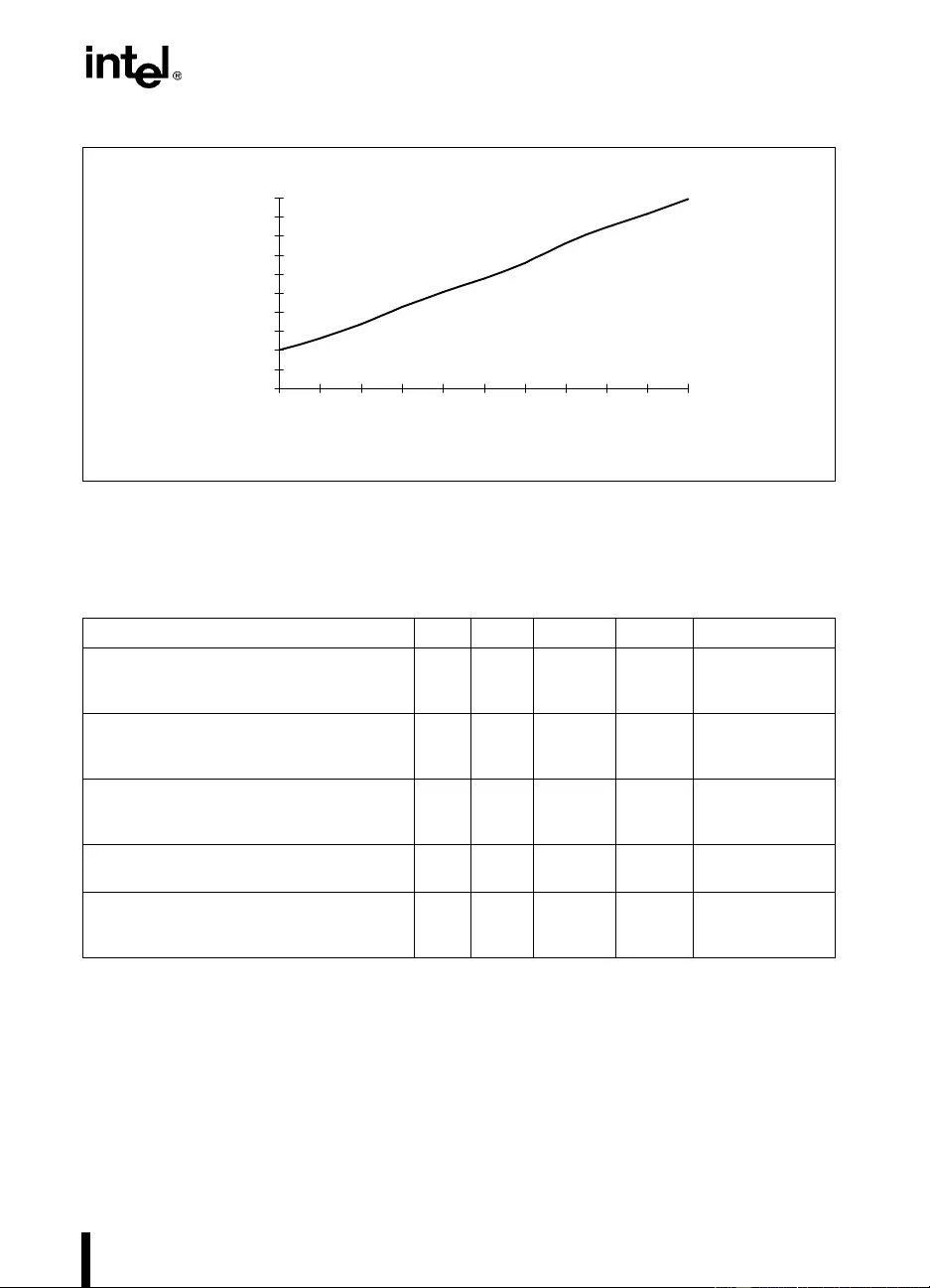

- Table 12-1. System DC Parameters

- Table 12-2. System Topological Guidelines

- Table 12-3. Specifications for Signal Quality

- Table 12-4. I/O Buffer DC Parameters

- Table 12-5. I/O Buffer AC Parameters

- Table 13-1. Signal Ringback Specifications

- Table 14-1. Case-To-Ambient Thermal Resistance

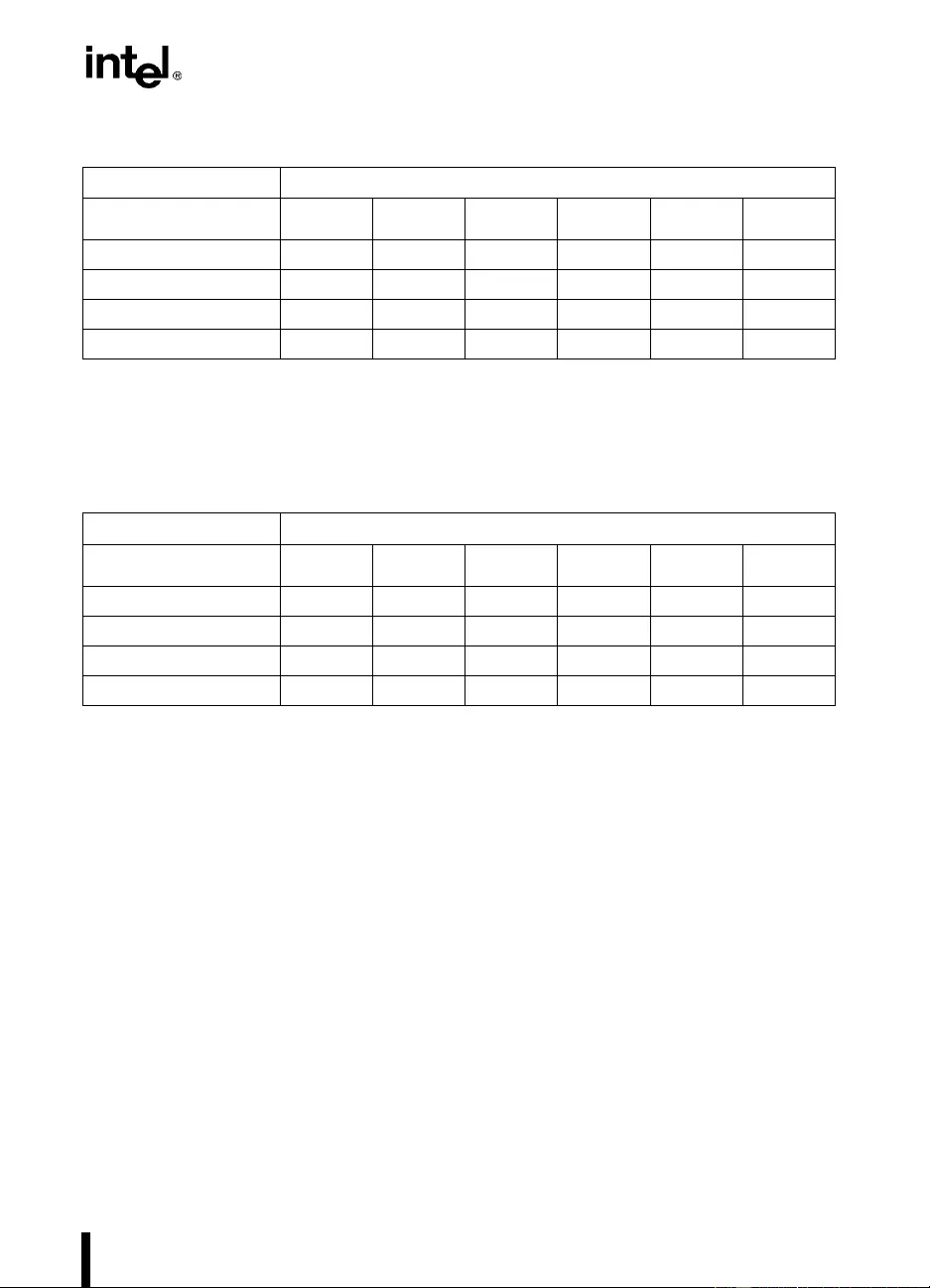

- Table 14-2. Ambient Temperatures Required at Heat Sink for 29.2W and 85° Case

- Table 14-3. Ambient Temperatures Required at Heat Sink for 40W and 85° Case

- Table 15-1. Pentium ® Pro Processor Package

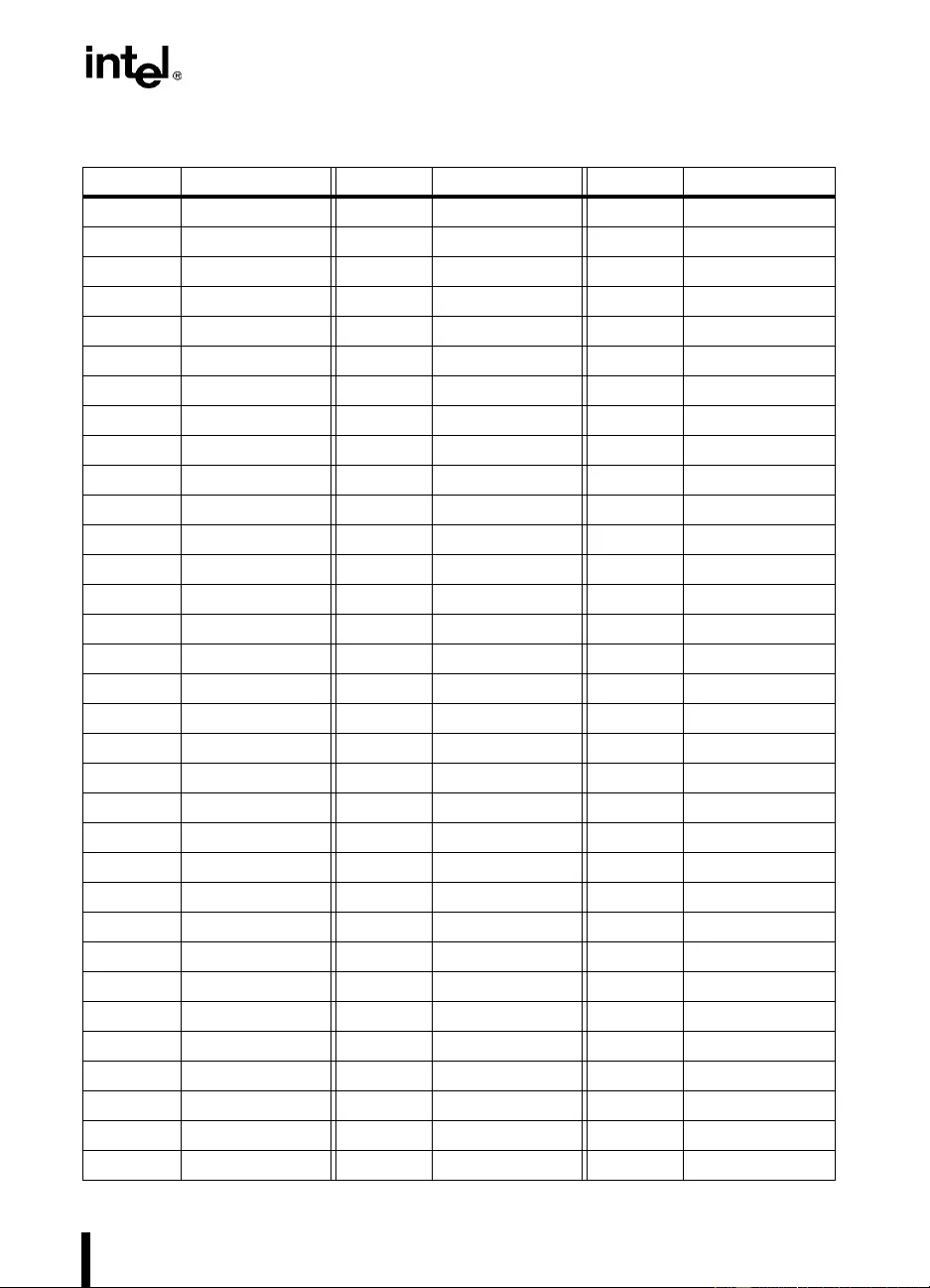

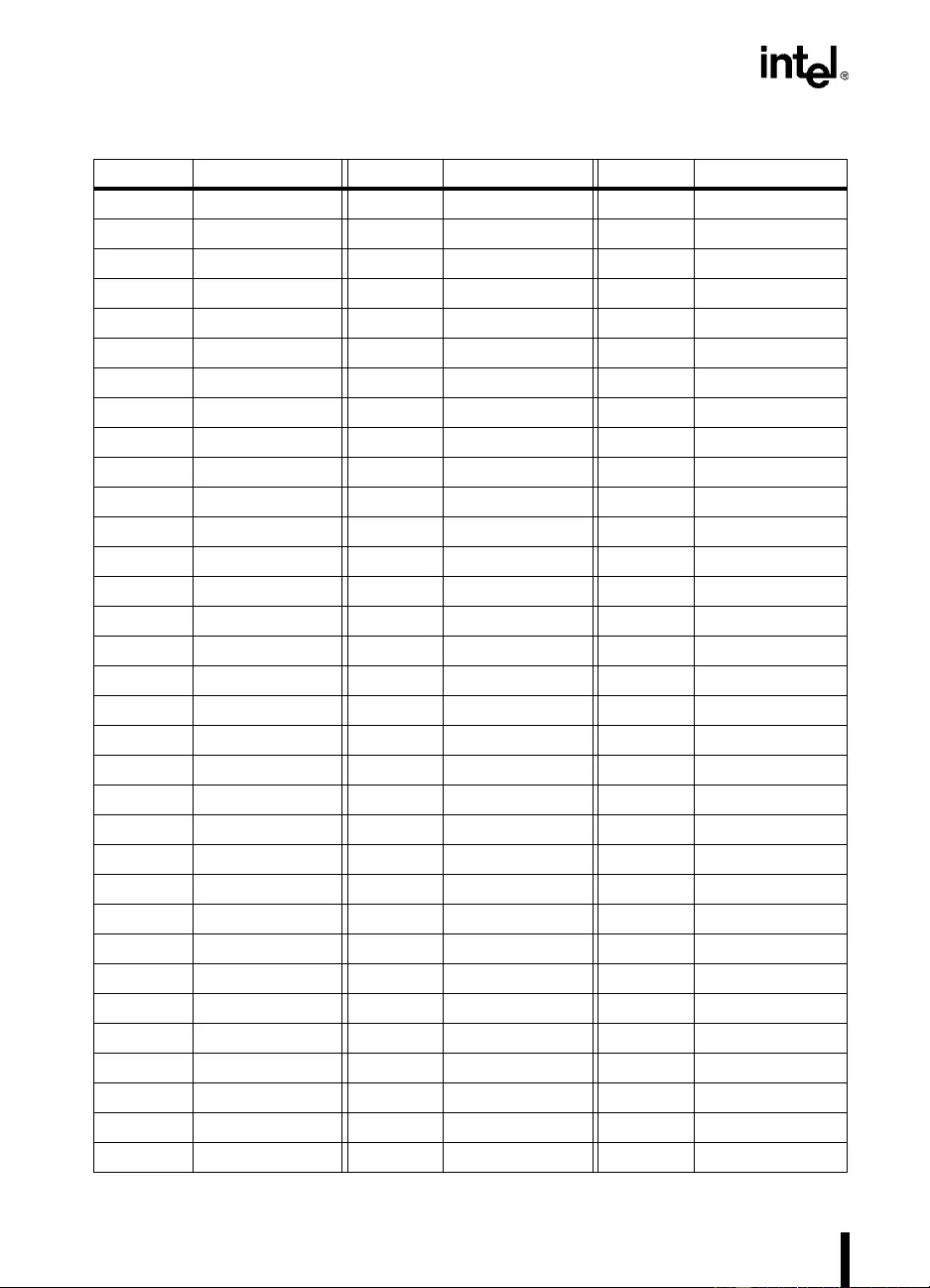

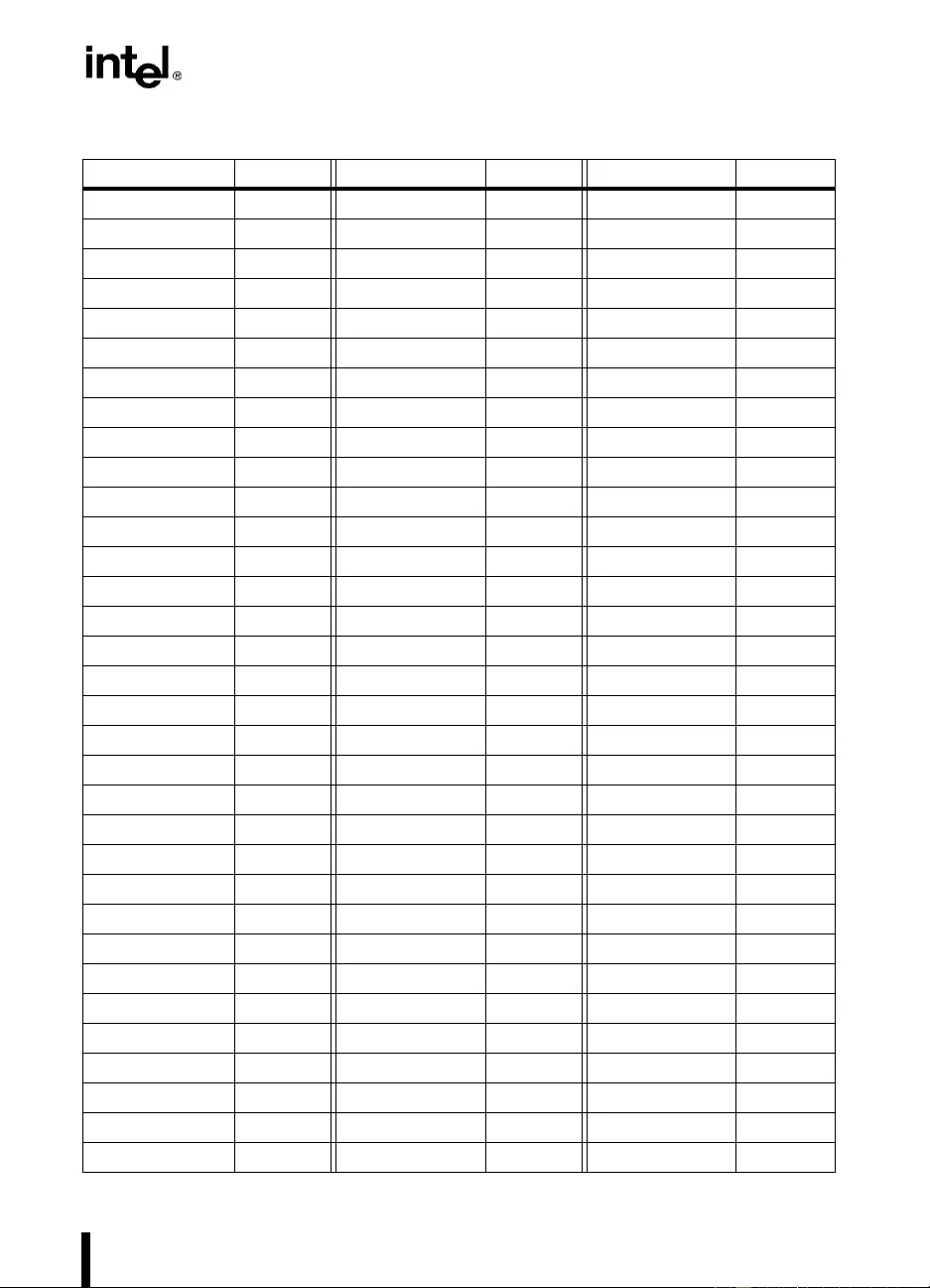

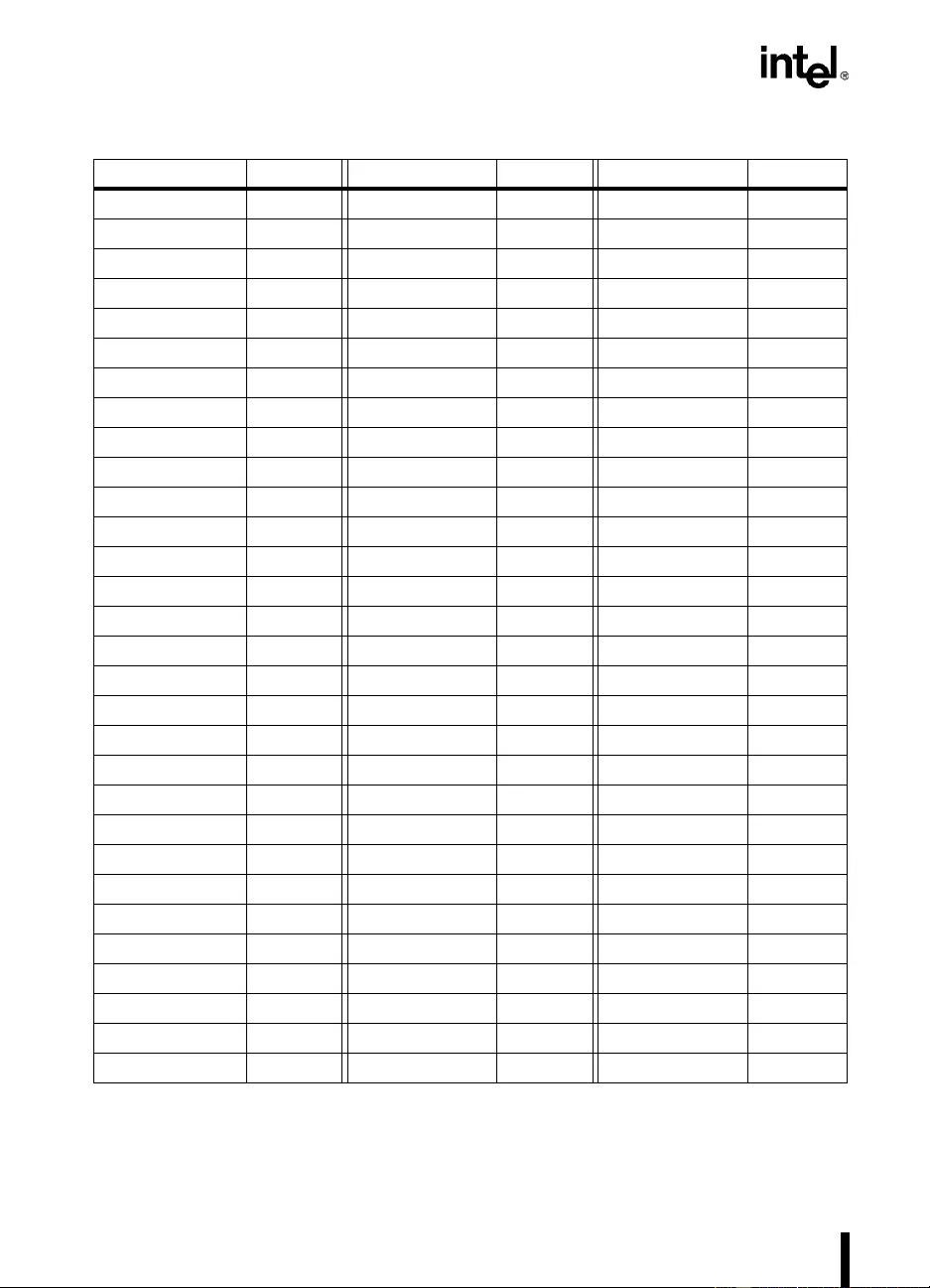

- Table 15-2. Pin Listing in Pin # Order

- Table 15-3. Pin Listing in Alphabetic Order

- Table 16-1. Debug Port Pinout

- Table 16-2. TCK Pull-Up Value

- Table 17-1. OverDrive ® Processor Signal Descriptions

- Table 17-2. Header 8 Pin Reference

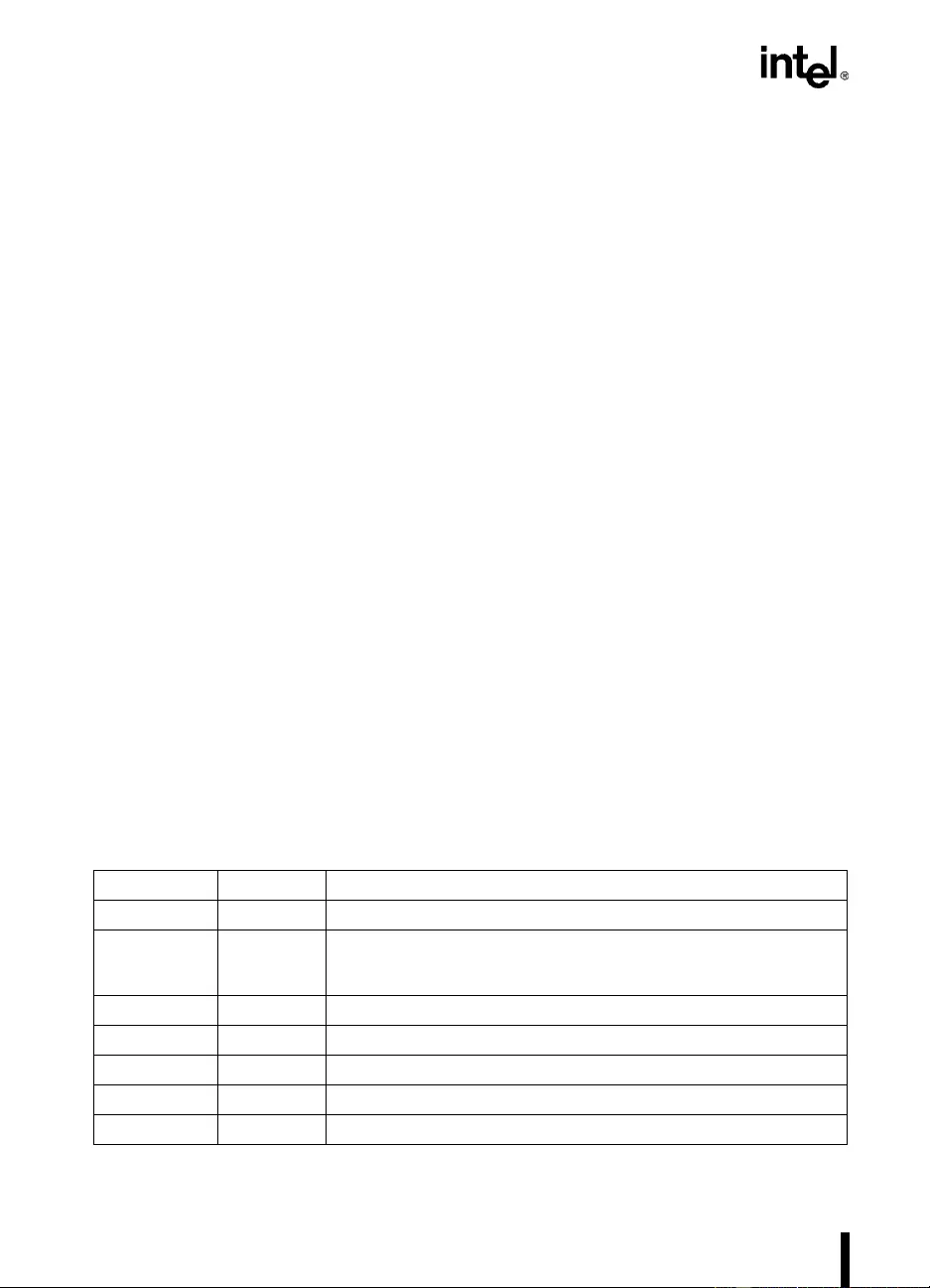

- Table 17-3. OverDrive ® Processor CPUID

- Table 17-4. OverDrive ® Processor D.C. Specifications

- Table 17-5. OverDrive ® VRM Specifications

- Table 17-6. OverDrive ® VRM Power Dissipation for Thermal Design

- Table 17-7. OverDrive ® Processor Thermal Resistance and Maximum Ambient Temperature

- Table 17-8. Electrical Test Criteria for Systems Employing Header 8

- Table 17-9. Electrical Test Criteria for Systems Not Employing Header 8

- Table 17-10. Electrical Test Criteria for all Systems

- Table 17-11. Thermal Test Criteria

- Table 17-12. Mechanical Test Criteria for the OverDrive ® Processor

- Table 17-13. Functional Test Criteria

- Tabl e A- 1. ASZ[1:0]# Signal Decode

- Table A-2. ATTR[7:0]# Field Descriptions

- Table A-3. Special Transaction Encoding on BE[7:0]#

- Table A-4. BR0#(I/O), BR1#, BR2#, BR3# Signals Rotating Interconnect

- Table A-5. BR[3:0]# Signal Agent IDs

- Table A-6. DID[7:0]# Encoding

- Table A-7. EFX[4:0]# Signal Definitions

- Table A-8. LEN[1:0]# Signals Data Transfer Lengths

- Table A-9. Transaction Types Defined by REQa#/REQb# Signals

- Table A-10. Transaction Response Encodings

- Table A-11. Output Signals

- Table A-12. Input Signals

- Table A-13. Input/Output Signals (Single Driver)

- Table A-14. Input/Output Signals (Multiple Driver)

Intel Pro 200 MHz User Manual

Displayed below is the user manual for Pro 200 MHz by Intel which is a product in the Processors category. This manual has pages.

Related Manuals

Pentium® Pro Family

Developer’s Manual

Volume 1:

Specifications

NOTE: The Pentium® Pro Family Developer’s Manual consists of three

books: Specifications, Order Number 242690; Programmer’s Reference

Manual, Order Number 242691; and the Operati ng Syste m Writer’s Guide,

Order Number 242692.

Please refer to all three volumes when evaluating your design needs.

1996

3/26/97 1:28 PM PPRODIS2.DOC

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or

otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions

of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating

to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability,

or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical,

life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined."

Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising

from future changes to them.

The Pentium® Pro processor may contain design defects or errors known as errata which may cause the product to deviate

from published specifications. Such errata are not covered by Intel’s warranty. Current characterized errata are available on

request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product

order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be

obtained from:

Intel Corporation

P.O. Box 7641

Mt. Prospect IL 60056-7641

or call 1-800-879-4683

or visit Intel’s website at http:\\www.intel.com

Copyright © Intel Corporation 1996, 1997.

* Third-party brands and names are the property of their respective owners.

v

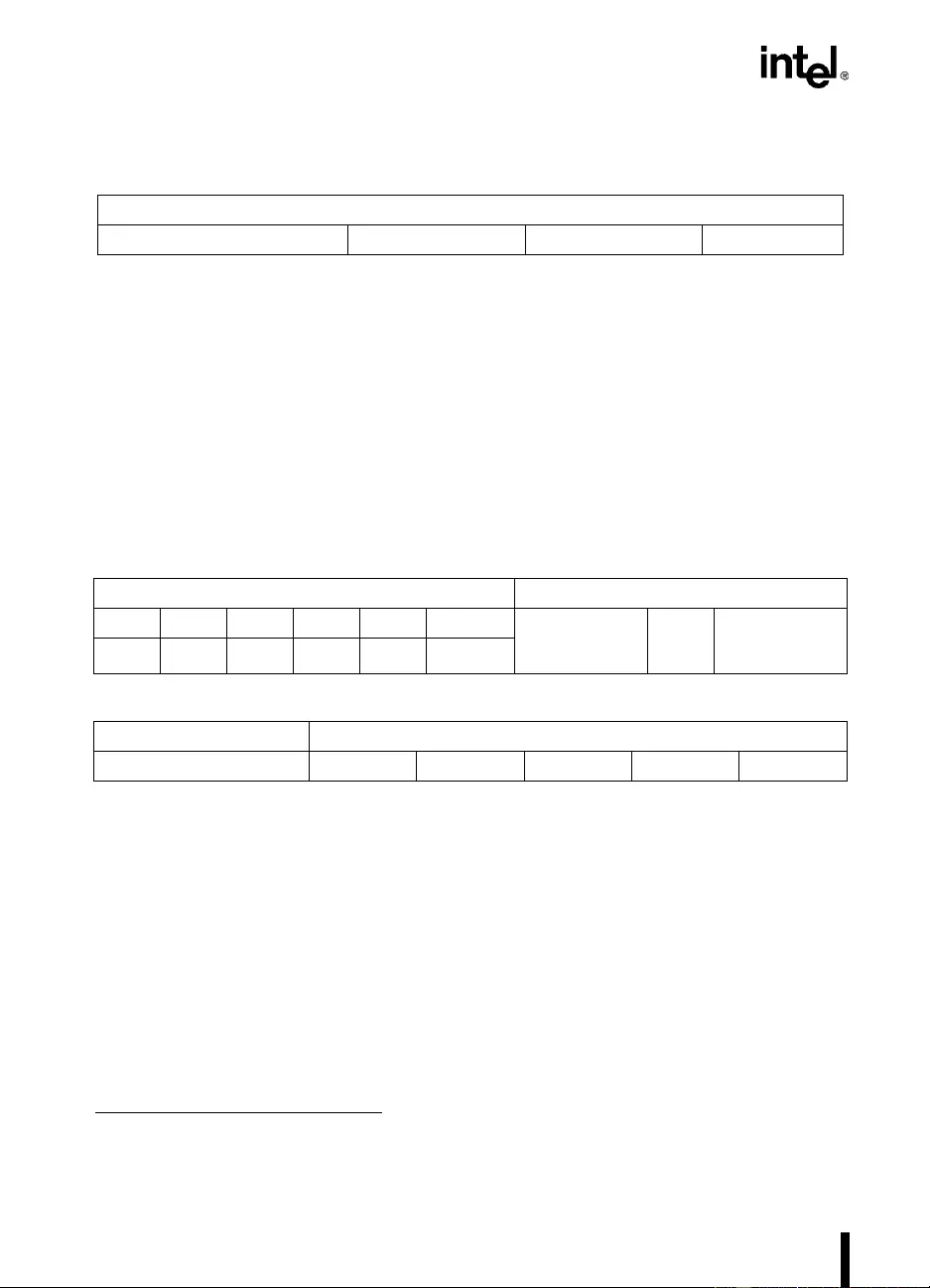

TABLE OF CONTENTS

PAGE

CHAPTER 1

COMPON ENT INTRODUCTION

1.1. BUS FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.2. BUS DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.2.1. System Design Aspects. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-4

1.2.2. Efficient Bus Utilization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-4

1.2.3. Multiprocessor Ready . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-4

1.2.4. Data Integrity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 -5

1.3. SYSTEM OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.4. TERMINOLOGY CLARIFICATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.5. COMPATIBILITY NOTE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

CHAPTER 2

PENTIUM® PRO PROCESSOR ARCHITECTURE OVERVIEW

2.1. FULL CORE UTILIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.2. THE PENTIUM® PRO PROCESSOR PIPELINE . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.2.1. The Fetch/Decode Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

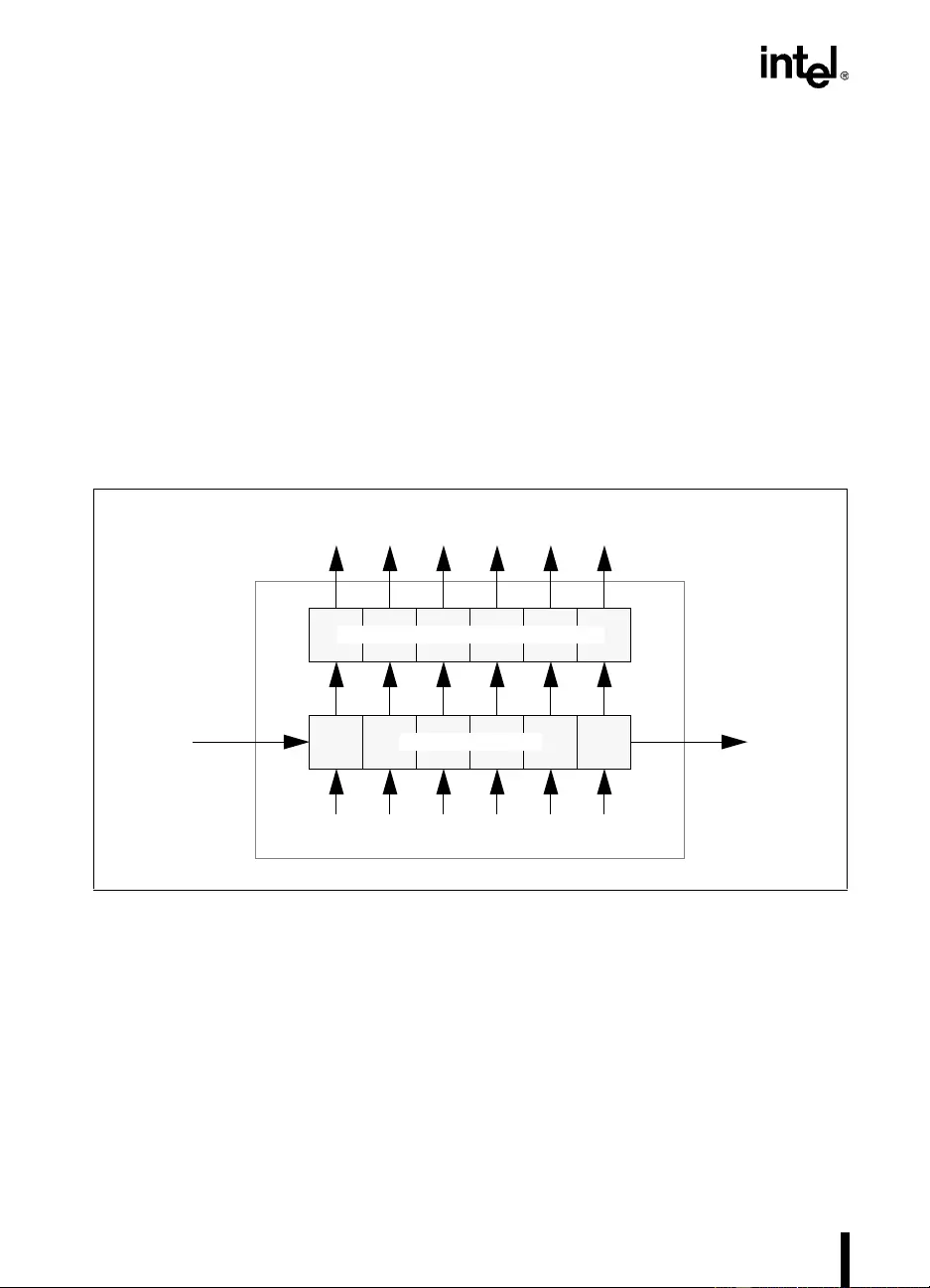

2.2.2. The Dispatch/Execute Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.2.3. The Retire Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

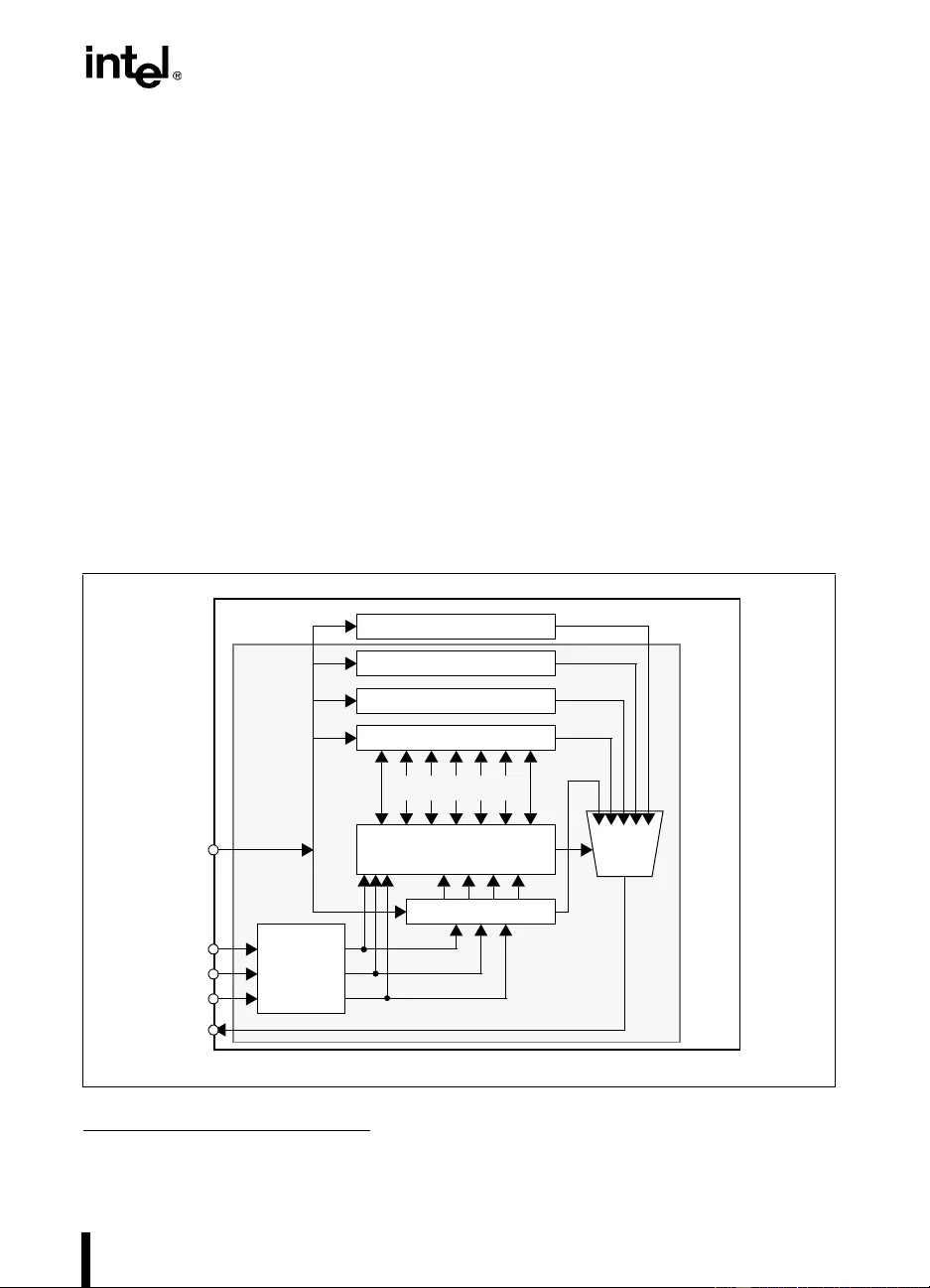

2.2.4. The Bus Interface Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

2.3. ARCHITECTURE SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

CHAPTER 3

BUS OVERVIEW

3.1. SIGNAL AND DIAGRAM CONVENTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.2. SIGNALING ON THE PENTIUM® PRO PROCESSOR BUS. . . . . . . . . . . . . . . . . . 3-2

3.3. PENTIUM® PRO PROCESSOR BUS PROTOCOL OVERVIEW. . . . . . . . . . . . . . . 3-4

3.3.1. Transaction Phase Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-4

3.3.2. Bus Transaction Pipelining and Transaction Tracking . . . . . . . . . . . . . . . . . . . . .3-6

3.3.3. Bus Transactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-7

3.3.4. Data Transfers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-8

3.3.4.1. Line Transfers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-9

3.3.4.2. Part Line Aligned Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 -9

3.3.4.3. Partial Transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-9

3.4. SIGNAL OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3.4.1. Execution Control Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

3.4.2. Arbitration Phase Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12

3.4.3. Request Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-13

3.4.4. Error Phase Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-18

3.4.5. Snoop Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-18

3.4.6. Response Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-20

3.4.7. Data Phase Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-21

3.4.8. Error Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-22

3.4.9. Compatibility Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-23

3.4.10. Diagnostic Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-24

3.4.11. Power, Ground, and Reserved Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-25

TABLE OF CONTENTS

vi

PAGE

CHAPTER 4

BUS PROTOCOL

4.1. ARBITRATION PHASE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.1.1. Protocol Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

4.1.2. Bus Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-2

4.1.3. Internal Bus States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

4.1.3.1. Symmetric Arbitration States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

4.1.3.1.1. Agent ID. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

4.1.3.1.2. Rotating ID. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

4.1.3.1.3. Symmetric Ownership State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

4.1.3.2. Request Stall Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-4

4.1.3.2.1. Request Stall States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-5

4.1.3.2.2. BNR# Sampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-5

4.1.4. Arbitration Protocol Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-5

4.1.4.1. Symmetric Arbitration of a Single Agent After RESET# . . . . . . . . . . . . . . . . . .4-5

4.1.4.2. Signal Deassertion After Bus Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-7

4.1.4.3. Delay of Transaction Generation After Reset. . . . . . . . . . . . . . . . . . . . . . . . . .4-8

4.1.4.4. Symmetric Arbitration with no LOCK# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-9

4.1.4.5. Symmetric Bus Arbitration with no Transaction Generation. . . . . . . . . . . . . .4-10

4.1.4.6. Bus Exchange Among Symmetric and Priority Agents with no LOCK# . . . . .4-11

4.1.4.7. Symmetric and Priority Bus Exchange During LOCK#. . . . . . . . . . . . . . . . . .4-13

4.1.4.8. BNR# Sampling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-14

4.1.5. Symmetric Agent Arbitration Protocol Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-16

4.1.5.1. Reset Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-16

4.1.5.2. Bus Request Assertion. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-16

4.1.5.3. Ownership from Idle State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-16

4.1.5.4. Ownership from Busy State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-17

4.1.5.4.1. Bus Parking and Release with a Single Bus Request . . . . . . . . . . . . . . . .4-17

4.1.5.4.2. Bus Exchange with Multiple Bus Requests . . . . . . . . . . . . . . . . . . . . . . . .4-17

4.1.6. Priority Agent Arbitration Protocol Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-17

4.1.6.1. Reset Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-17

4.1.6.2. Bus Request Assertion. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-18

4.1.6.3. Bus Exchange from an Unlocked Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-18

4.1.6.4. Bus Release . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-18

4.1.7. Bus Lock Protocol Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-18

4.1.7.1. Bus Ownership Exchange from a Locked Bus . . . . . . . . . . . . . . . . . . . . . . . .4-18

4.2. REQUEST PHASE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-18

4.2.1. Bus Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-19

4.2.2. Request Phase Protocol Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-19

4.2.3. Request Phase Protocol Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-20

4.2.3.1. Request Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-20

4.2.3.2. Request Phase Qualifiers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-20

4.3. ERROR PHASE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-20

4.3.1. Bus Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-21

4.4. SNOOP PHASE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-21

4.4.1. Snoop Phase Bus Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-21

4.4.2. Snoop Phase Protocol Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-22

4.4.2.1. Normal Snoop Phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-22

4.4.2.2. Stalled Snoop Phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-23

4.4.3. Snoop Phase Protocol Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-24

4.4.3.1. Snoop Phase Results. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-24

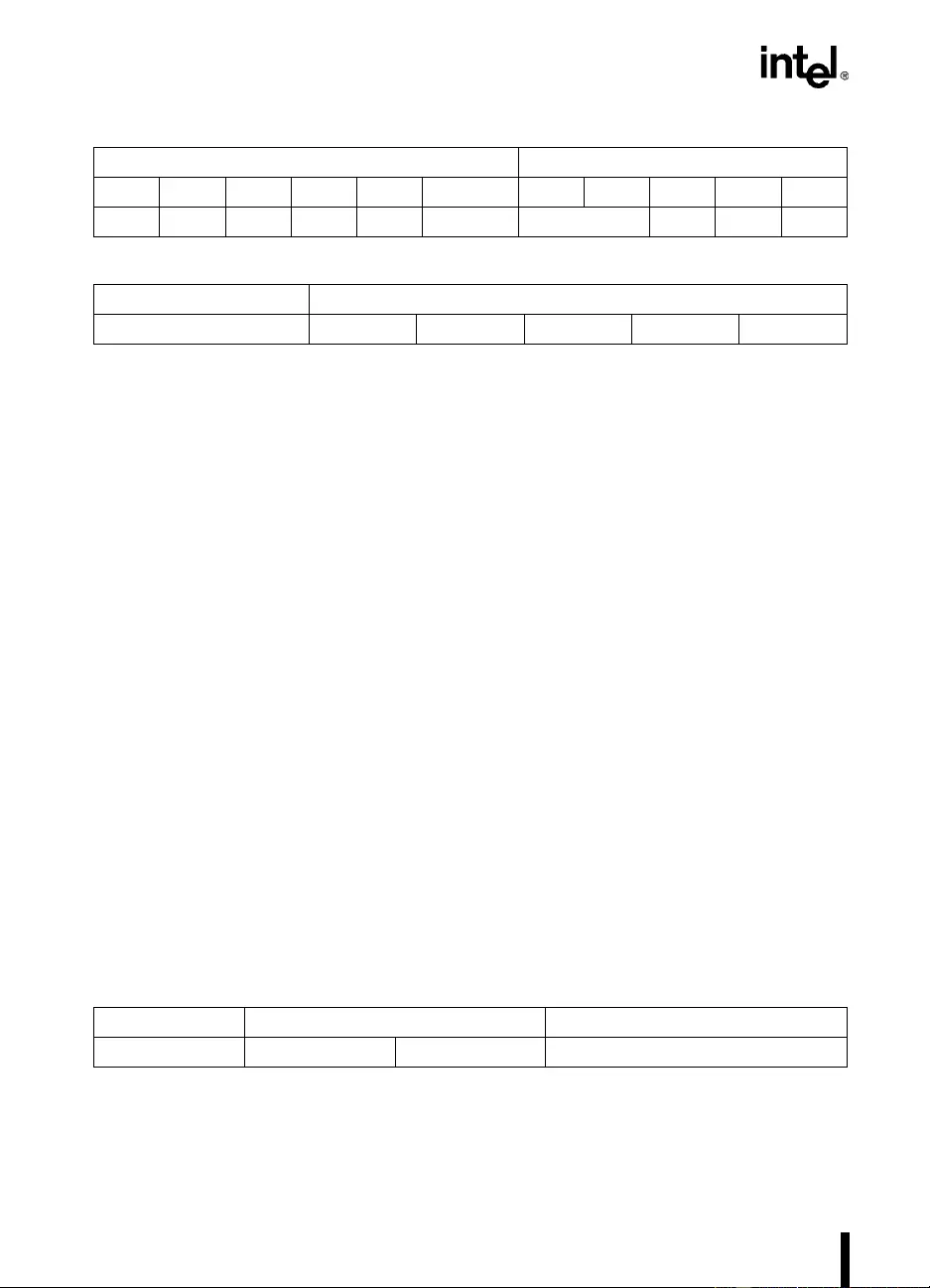

vii

TABLE OF CON TENTS

PAGE

4.4.3.2. Valid Snoop Phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-25

4.4.3.3. Snoop Phase Stall . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-25

4.4.3.4. Snoop Phase Completion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-25

4.4.3.5. Snoop Results Sampling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-25

4.5. RESPONSE PHASE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-25

4.5.1. Response Phase Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-25

4.5.1.1. Bus Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-26

4.5.2. Response Phase Protocol Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-26

4.5.2.1. Response for a Transaction Without Write Data. . . . . . . . . . . . . . . . . . . . . . 4-26

4.5.2.2. Write Data Transaction Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-28

4.5.2.3. Implicit Writeback on a Read Transaction . . . . . . . . . . . . . . . . . . . . . . . . . . 4-29

4.5.2.4. Implicit Writeback with a Write Transaction . . . . . . . . . . . . . . . . . . . . . . . . . 4-30

4.5.3. Response Phase Protocol Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-31

4.5.3.1. Request Initiated TRDY# Assertion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-31

4.5.3.2. Snoop Initiated TRDY# protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-31

4.5.3.3. TRDY# Deassertion Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-31

4.5.3.4. RS[2:0]# Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-32

4.5.3.5. RS[2:0]#, RSP# protocol. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-32

4.6. DATA PHASE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-33

4.6.1. Data Phase Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-33

4.6.1.1. Bus Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-33

4.6.2. Data Phase Protocol Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-33

4.6.2.1. Simple Write Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-33

4.6.2.2. Simple Read Transaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-34

4.6.2.3. Implicit Writeback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-35

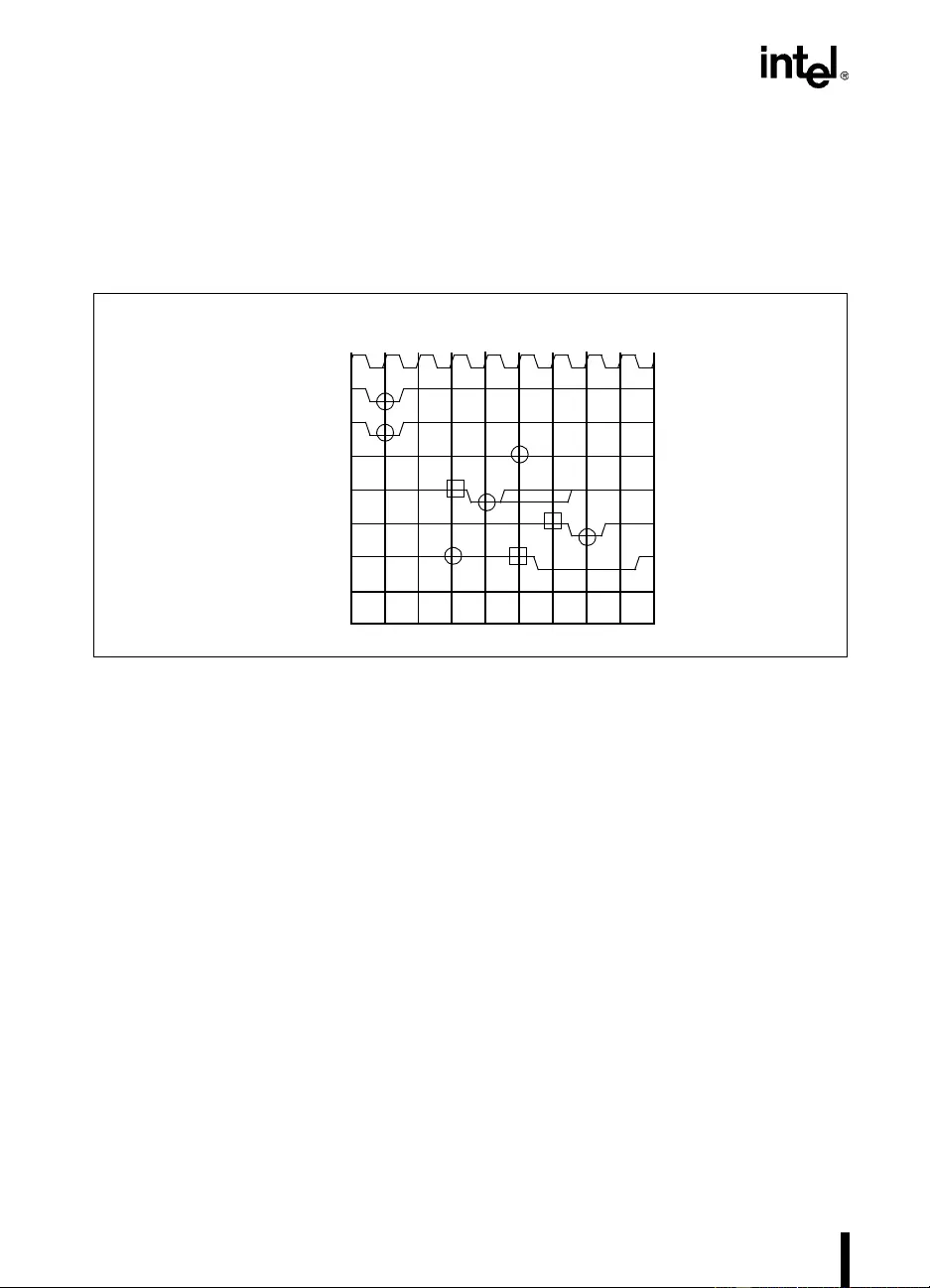

4.6.2.4. Full Speed Read Partial Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-36

4.6.2.5. Relaxed DBSY# Deassertion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-37

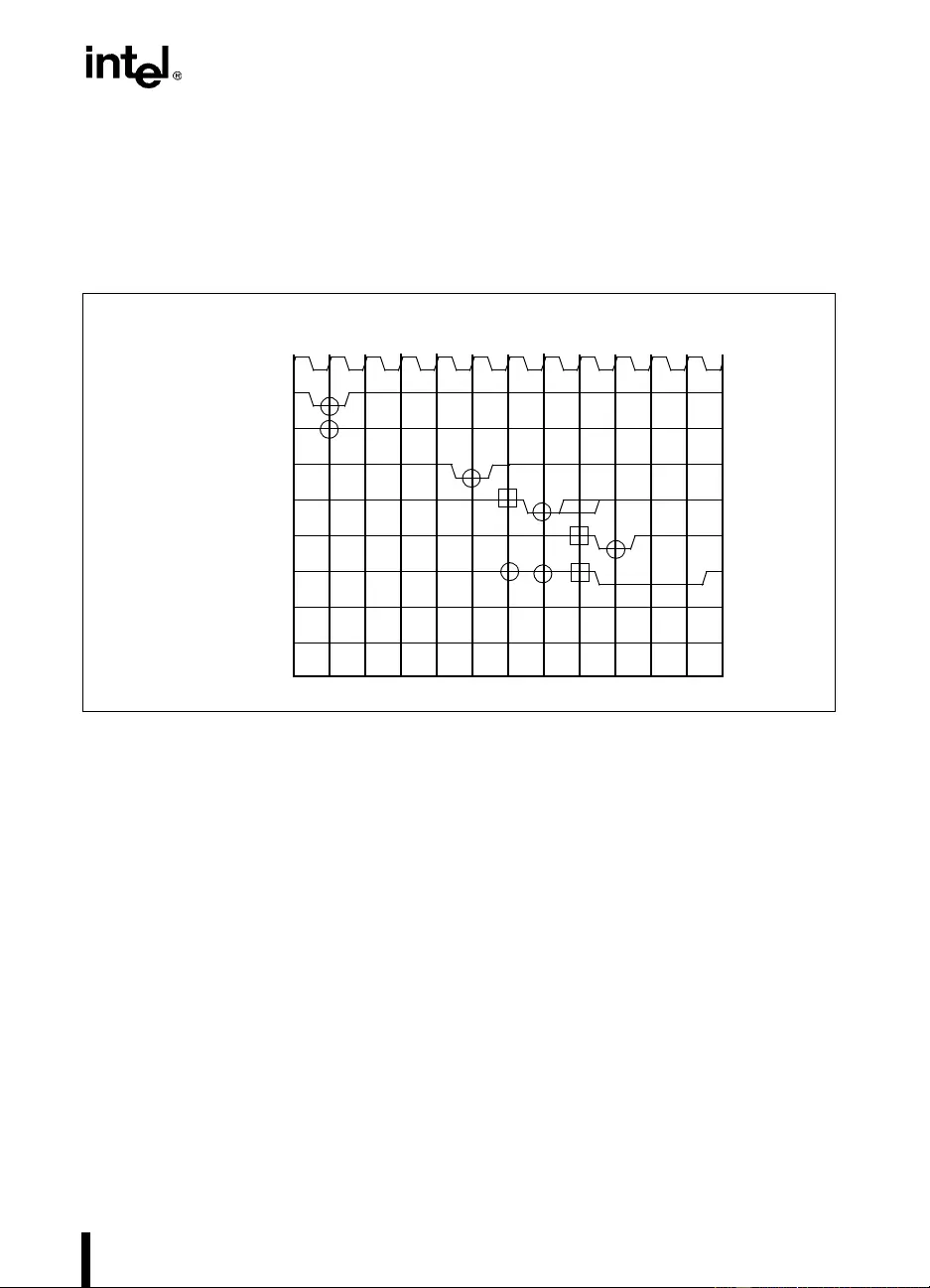

4.6.2.6. Full Speed Read Line Transfers (Same Agent) . . . . . . . . . . . . . . . . . . . . . . 4-38

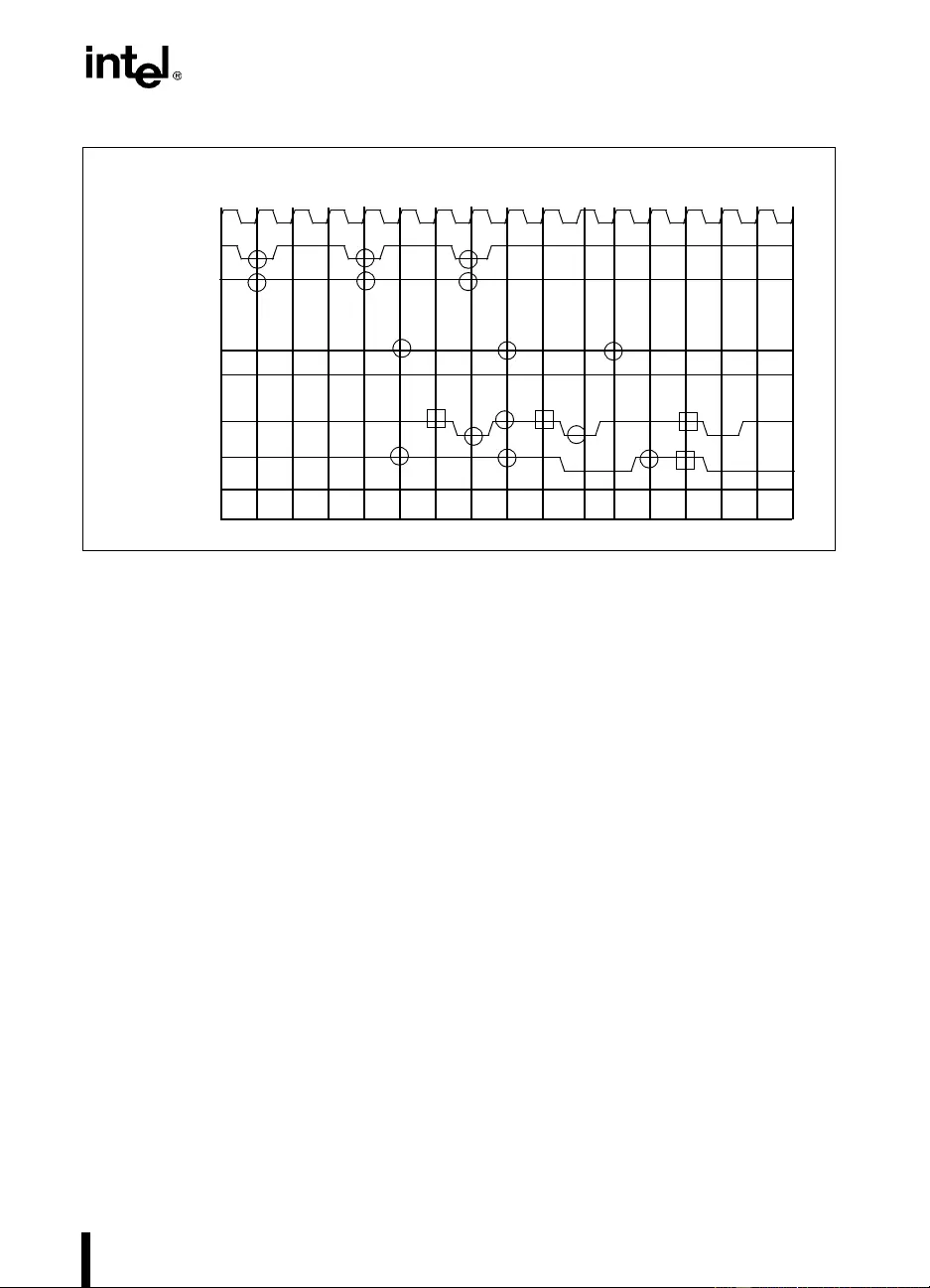

4.6.2.7. Full Speed Write Partial Transactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-39

4.6.2.8. Full Speed Write Line Transactions (Same Agents). . . . . . . . . . . . . . . . . . . 4-40

4.6.3. Data Phase Protocol Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-42

4.6.3.1. Valid Data Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-42

4.6.3.2. Request Initiated Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-42

4.6.3.3. Snoop Initiated Data Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-42

CHAPTER 5

BUS TRANSACTIONS AND OPERATIONS

5.1. BUS TRANSACTIONS SUPPORTED . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.2. BUS TRANSACTION DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.2.1. Memory Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.2.1.1. Memory Read Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5.2.1.2. Memory Write Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5.2.1.3. Memory (Read) Invalidate Transactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5.2.1.4. Reserved Memory Write Transaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

5.2.2. I/O Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-6

5.2.2.1. Request Initiator Responsibilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.2.2.2. Addressed Agent Responsibilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.2.3. Non-memory Central Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5.2.3.1. Request Initiator Responsibilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

5.2.3.2. Central Agent Responsibilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

5.2.3.3. Observing Agent Responsibilities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

5.2.3.4. Interrupt Acknowledge Transaction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

TABLE OF CONTENTS

viii

PAGE

5.2.3.5. Branch Trace Message. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-9

5.2.3.6. Special Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 -9

5.2.3.6.1. Shutdown. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-10

5.2.3.6.2. Flush . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-10

5.2.3.6.3. Halt. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-10

5.2.3.6.4. Sync. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-11

5.2.3.6.5. Flush Acknowledge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-11

5.2.3.6.6. Stop Grant Acknowledge. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-11

5.2.3.6.7. SMI Acknowledge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-11

5.2.4. Deferred Reply Transaction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-12

5.2.4.1. Request Initiator Responsibilities (Deferring Agent). . . . . . . . . . . . . . . . . . . .5-12

5.2.4.2. Addressed Agent Responsibilities (Original Requestor). . . . . . . . . . . . . . . . .5-13

5.2.5. Reserved Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-13

5.3. BUS OPERATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

5.3.1. Implicit Writeback Response. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-13

5.3.1.1. Memory Agent Responsibilities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-14

5.3.1.2. Requesting Agent Responsibilities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-14

5.3.2. Transferring Snoop Responsibility. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-15

5.3.3. Deferred Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-16

5.3.3.1. Response Agent Responsibilities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-17

5.3.3.2. Requesting Agent Responsibilities. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-18

5.3.4. Locked Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-19

5.3.4.1. [Split] Bus Lock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-20

CHAPTER 6

RANGE REGISTERS

6.1. INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.2. RANGE REGISTERS AND PENTIUM® PRO PROCESSOR INSTRUCTION

EXECUTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.3. MEMORY TYPE DESCRIPTIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.3.1. UC Memory Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3

6.3.2. WC Memory Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 -3

6.3.3. WT Memory Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3

6.3.4. WP Memory Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4

6.3.5. WB Memory Type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-4

CHAPTER 7

CACHE PROTOCOL

7.1. LINE STATES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.2. MEMORY TYPES, AND TRANSACTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

7.2.1. Memory Types: WB, WT, WP, and UC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-2

7.2.2. Bus Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-2

7.2.3. Naming Convention for Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-3

CHAPTER 8

DATA INTEGRITY

8.1. ERROR CLASSIFICATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

8.2. PENTIUM® PRO PROCESSOR BUS DATA INTEGRITY ARCHITECTURE . . . . . 8-2

8.2.1. Bus Signals Protected Directly . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-2

8.2.2. Bus Signals Protected Indirectly . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 -4

8.2.3. Unprotected Bus Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-6

ix

TABLE OF CON TENTS

PAGE

8.2.4. Time-out Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-6

8.2.5. Hard-error Response. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.2.6. Bus Error Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.2.6.1. Parity Algorithm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.2.6.2. Pentium® Pro Processor Bus ECC Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.3. ERROR REPORTING MECHANISM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.3.1. MCA Hardware Log . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.3.2. MCA Software Log. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-7

8.3.3. IERR# Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-8

8.3.4. BERR# Signal and Protocol. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-8

8.3.5. BINIT# Signal and Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-9

8.4. PENTIUM® PRO PROCESSOR IMPLEMENTATION . . . . . . . . . . . . . . . . . . . . . . 8-10

8.4.1. Speculative Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-11

8.4.2. Fatal Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-11

8.4.3. Pentium® Pro Processor Time-Out Counter . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-12

CHAPTER 9

CONFIGURATION

9.1. DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

9.1.1. Output Tristate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-2

9.1.2. Built-in Self Test. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.1.3. Data Bus Error Checking Policy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.1.4. Response Signal Parity Error Checking Policy . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.1.5. AERR# Driving Policy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.1.6. AERR# Observation Policy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.1.7. BERR# Driving Policy for Initiator Bus Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.1.8. BERR# Driving Policy for Target Bus Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9.1.9. Bus Error Driving Policy for Initiator Internal Errors. . . . . . . . . . . . . . . . . . . . . . . 9-4

9.1.10. BERR# Observation Policy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9.1.11. BINIT# Driving Policy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9.1.12. BINIT# Observation Policy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9.1.13. In-order Queue Pipelining . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9.1.14. Power-on Reset Vector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-5

9.1.15. FRC Mode Enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-5

9.1.16. APIC Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-5

9.1.17. APIC Cluster ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-5

9.1.18. Symmetric Agent Arbitration ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-6

9.1.19. Low Pow er Standby Enable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

9.2. CLOCK FREQUENCIES AND RATIOS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-9

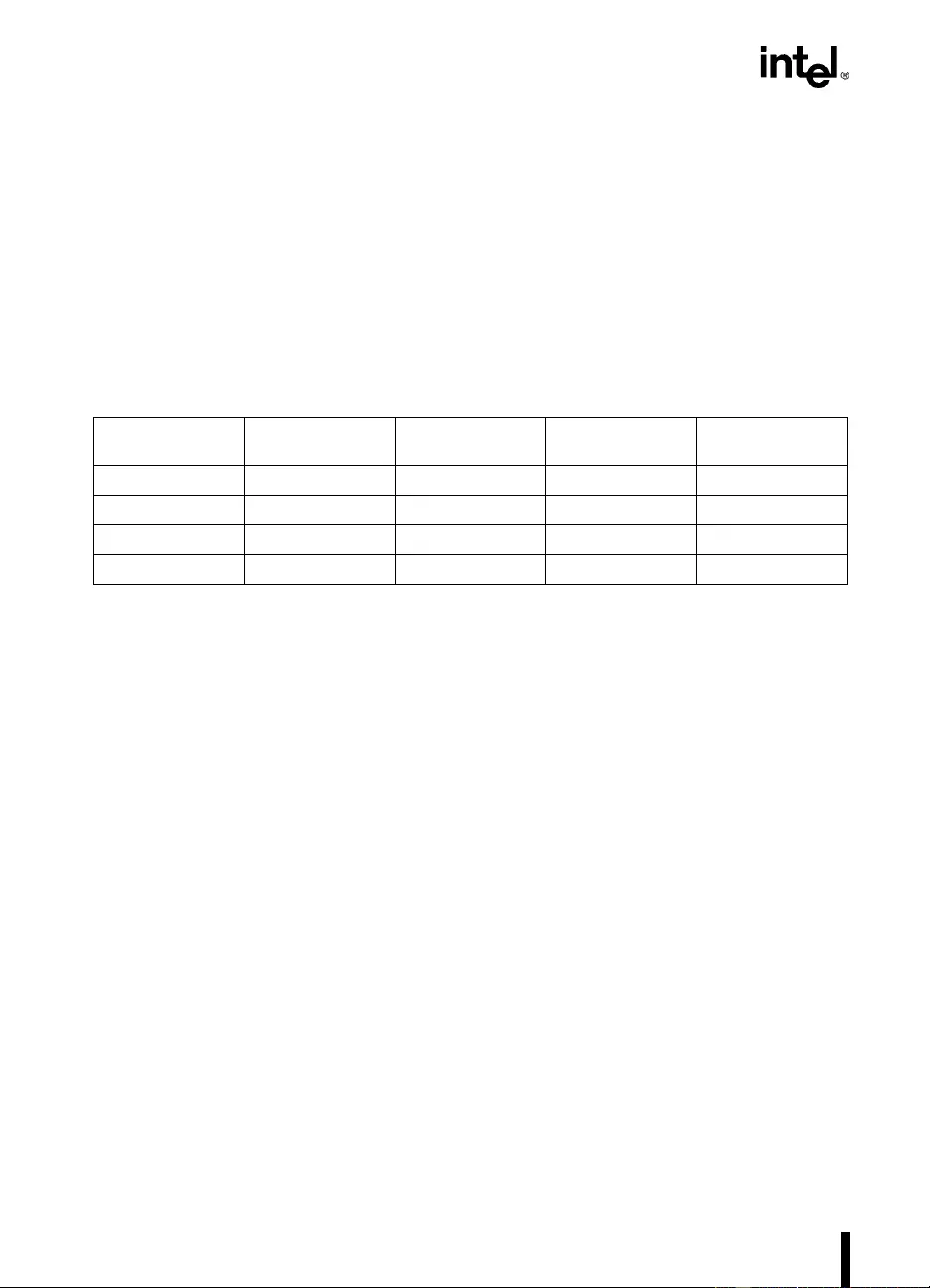

9.2.1. Clock Frequencies and Ratios at Product Introduction . . . . . . . . . . . . . . . . . . . 9-10

9.3. SOFTWARE-PROGRAMMABLE OPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-10

CHAPTER 10

PENTIUM® PRO PROCESSOR TEST ACCESS PORT (TAP)

10.1. INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-2

10.2. ACCESSING THE TAP LOGIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-2

10.2.1. Accessing the Instruction Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-4

10.2.2. Accessing the Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-6

10.3. INSTRUCTION SET. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-6

10.4. DATA REGISTER SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-8

10.4.1. Bypass Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-8

10.4.2. Device ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-8

TABLE OF CONTENTS

x

PAGE

10.4.3. BIST Result Boundary Scan Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-9

10.4.4. Boundary Scan Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-9

10.5. RESET BEHAVIOR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-9

CHAPTER 11

ELECTRICAL SPECIFICATIONS

11.1. THE PENTIUM® PRO PROCESSOR BUS AND VREF. . . . . . . . . . . . . . . . . . . . . 11-1

11.2. POWER MANAGEMENT: STOP GRANT AND AUTO HALT . . . . . . . . . . . . . . . . 11-2

11.3. POWER AND GROUND PINS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-2

11.4. DECOUPLING RECOMMENDATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-3

11.4.1. VccS Decoupling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-4

11.4.2. GTL+ Decoupling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-4

11.4.3. Phase Lock Loop (PLL) Decoupling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-4

11.5. BCLK CLOCK INPUT GUIDELINES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-5

11.5.1. Setting the Core Clock to Bus Clock Ratio . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-5

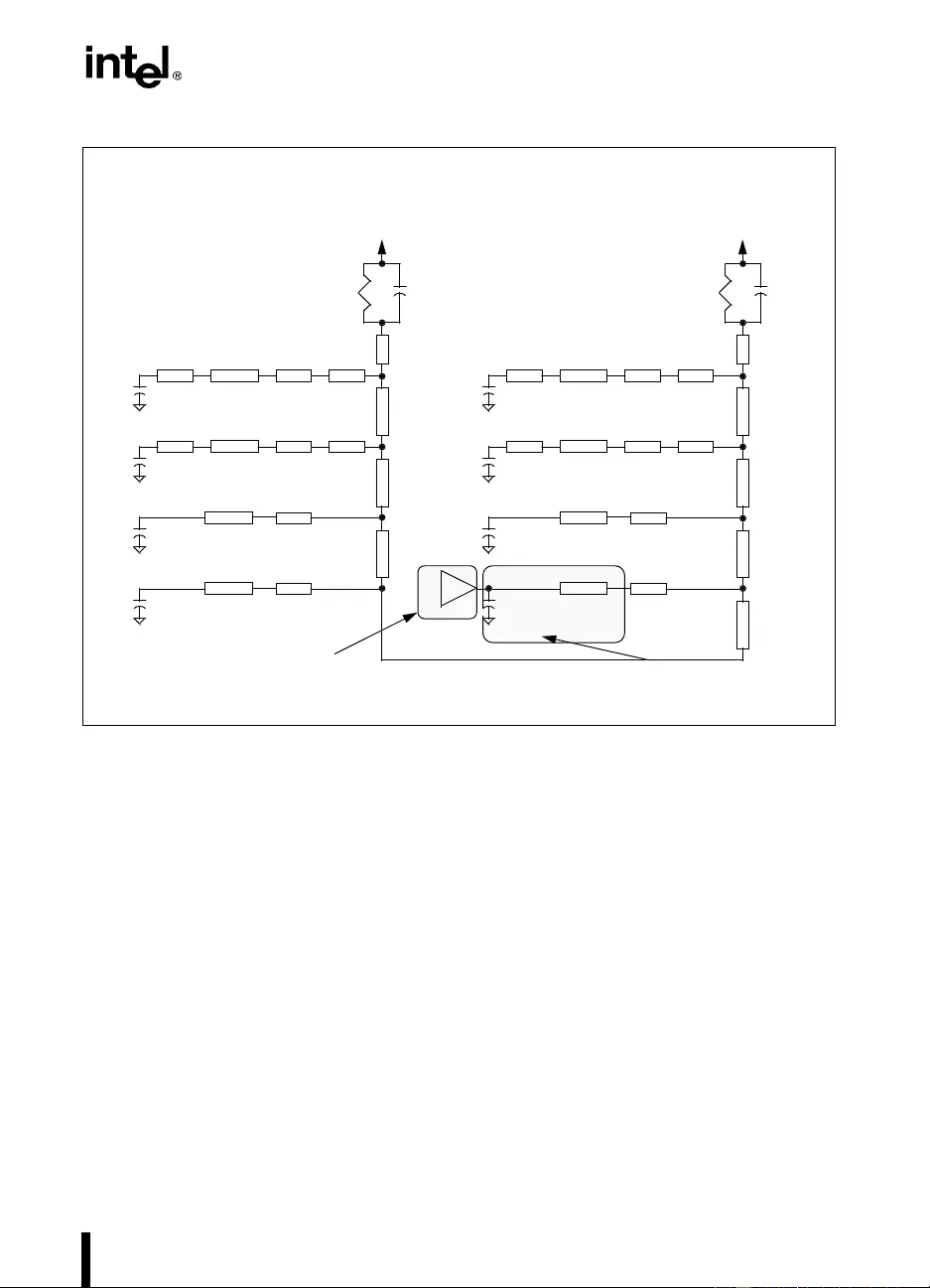

11.5.2. Mixing Processors of Different Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-7

11.6. VOLTAGE IDENTIFICATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-7

11.7. JTAG CONNECTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-8

11.8. SIGNAL GROUPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-9

11.8.1. Asynchronous vs. Synchronous . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-9

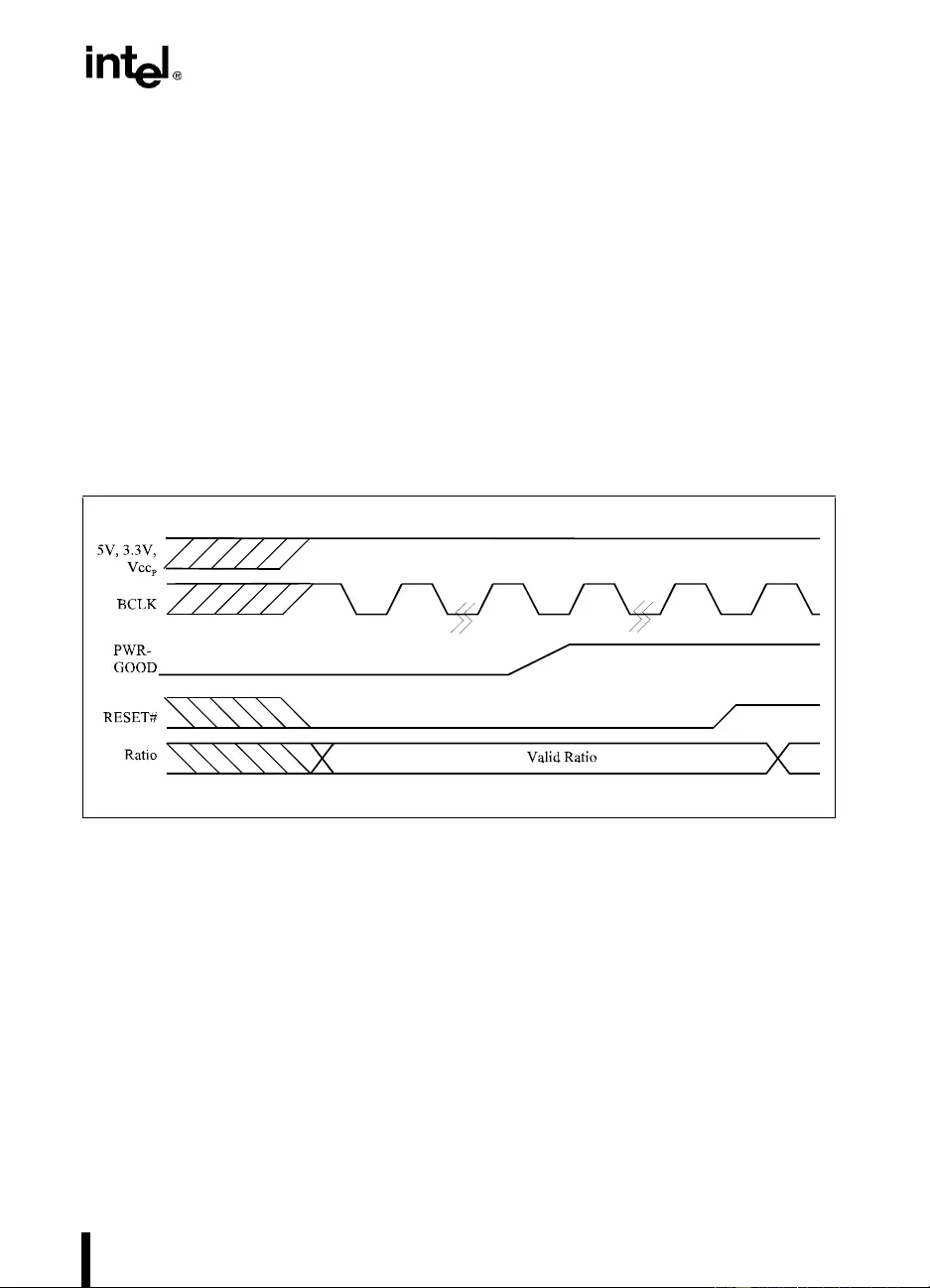

11.9. PWRGOOD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-11

11.10. THERMTRIP# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-11

11.11. UNUSED PINS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-12

11.12. MAXIMUM RATINGS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-12

11.13. D.C. SPECIFICATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-14

11.14. GTL+ BUS SPECIFICATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-17

11.15. A.C. SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-18

11.16. FLEXIBLE MOTHERBOARD RECOMMENDATIONS. . . . . . . . . . . . . . . . . . . . . 11-28

CHAPTER 12

GTL+ INTERFACE SPECIFICATION

12.1. SYSTEM SPECIFICATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-1

12.1.1. System DC Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-2

12.1.2. Topological Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-4

12.1.3. System AC Parameters: Signal Quality. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-4

12.1.3.1. Ringback Tolerance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-6

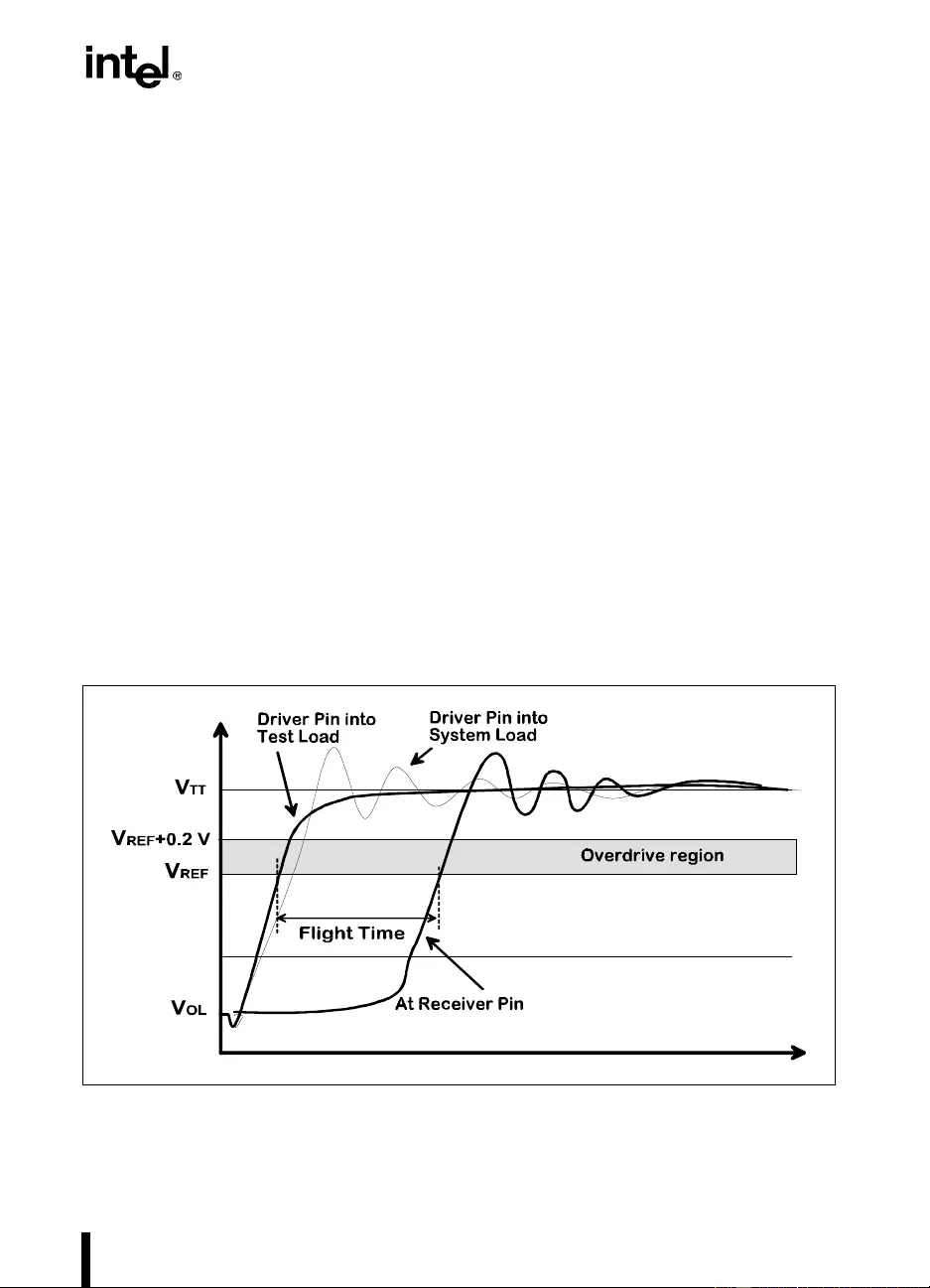

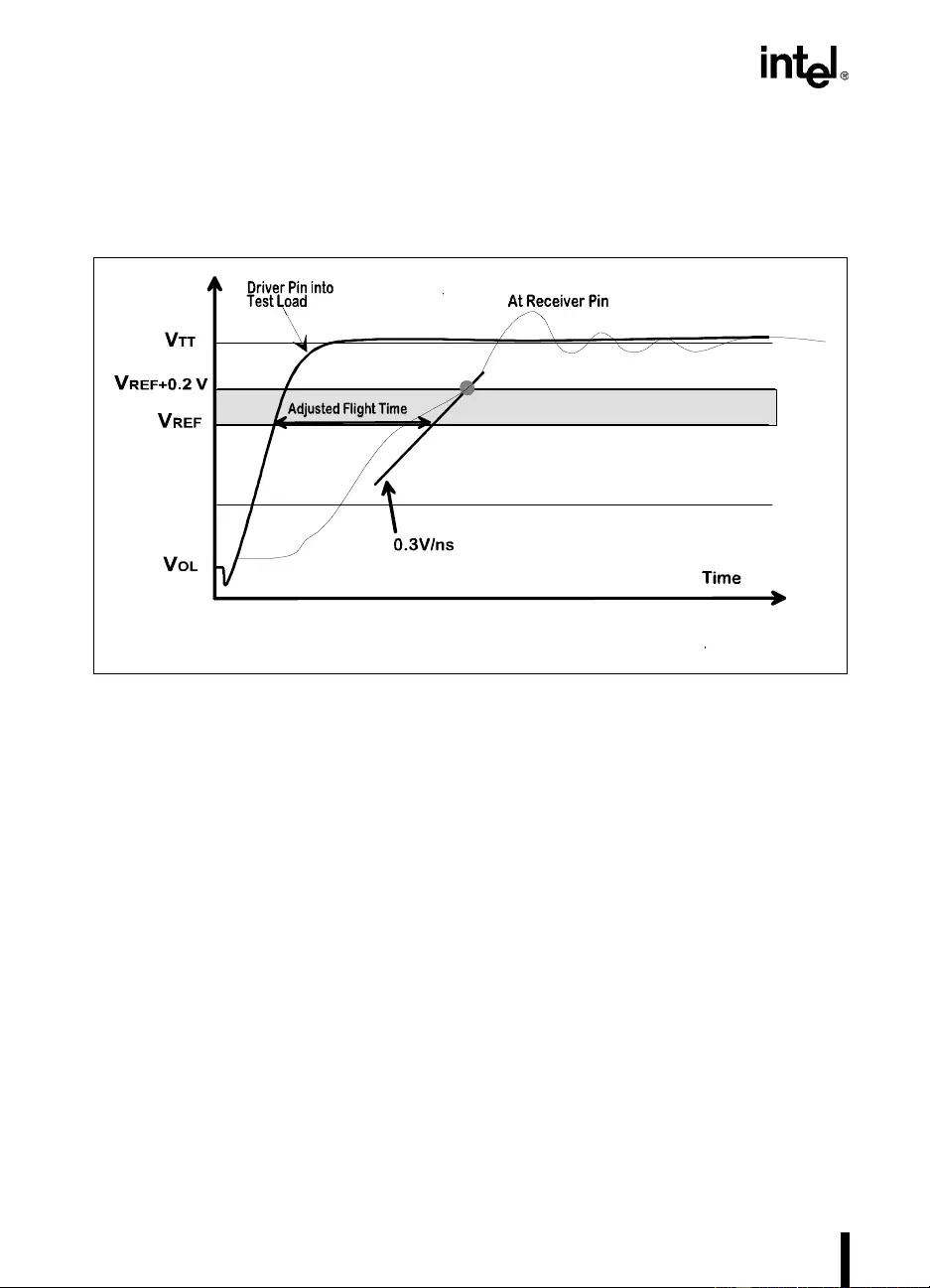

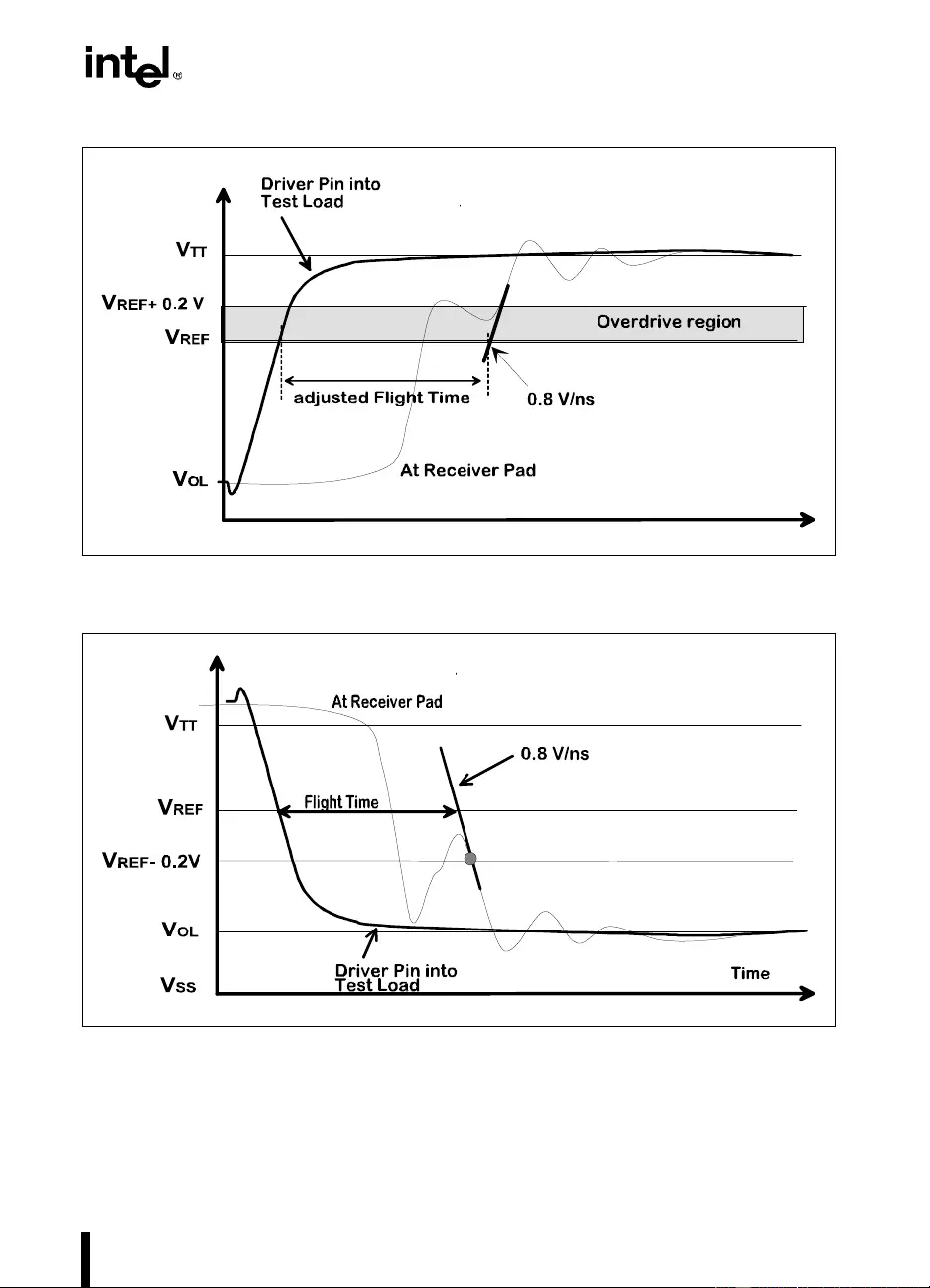

12.1.4. AC Parameters: Flight Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-8

12.2. GENERAL GTL+ I/O BUFFER SPECIFICATION . . . . . . . . . . . . . . . . . . . . . . . . 12-12

12.2.1. I/O Buffer DC Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-12

12.2.2. I/O Buffer AC Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-13

12.2.2.1. Output Driver Acceptance Criteria . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-15

12.2.3. Determining Clock-To-Out, Setup and Hold . . . . . . . . . . . . . . . . . . . . . . . . . . .12-17

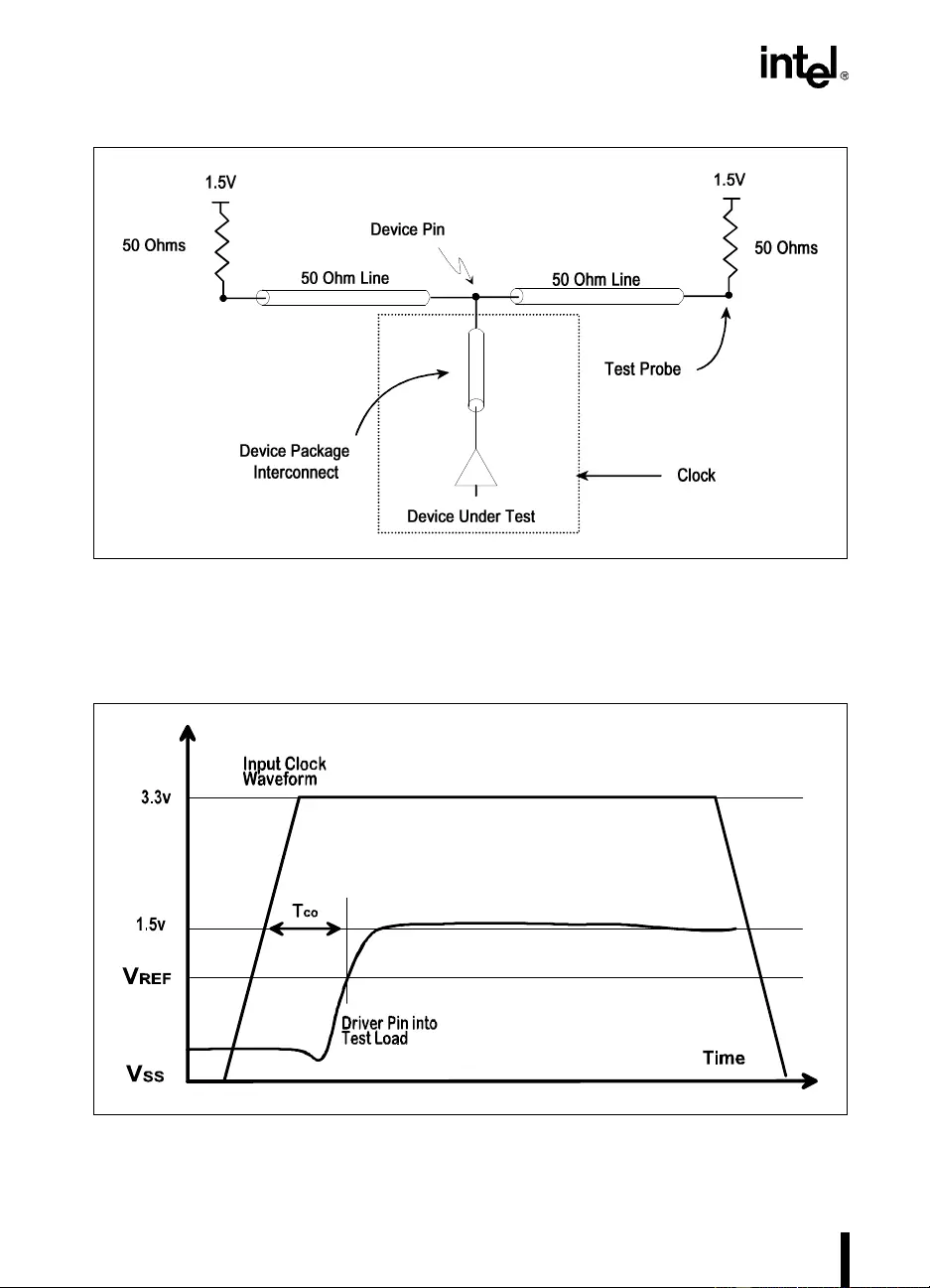

12.2.3.1. Clock-to-Output Time, TCO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-17

12.2.3.2. Minimum Setup and Hold Times. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-19

12.2.3.3. Receiver Ringback Tolerance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-21

12.2.4. System-Based Calculation of Required Input and Output Timings . . . . . . . . . .12-22

12.2.4.1. Calculating Target TCO-max, and TSU-Min. . . . . . . . . . . . . . . . . . . . . . . . .12-22

12.2.5. Calculating Target THOLD-MIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-23

12.3. PACKAGE SPECIFICATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-23

12.3.1. Package Trace Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-23

12.3.2. Package Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-24

12.4. REF8N NETWORK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-24

12.4.1. Ref8N HSPICE Netlist. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-26

xi

TABLE OF CON TENTS

PAGE

CHAPTER 13

3.3V TOLERANT SIGNAL QUALITY SPECIFICATIONS

13.1. OVERSHOOT/UNDERSHOOT GUIDELINES . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-1

13.2. RINGBACK SPECIFICATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-2

13.3. SETTLING LIMIT GUIDELINE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-3

CHAPTER 14

THERMAL SPECIFICATIONS

14.1. THERMAL PARAMETERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-1

14.1.1. Ambient Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-1

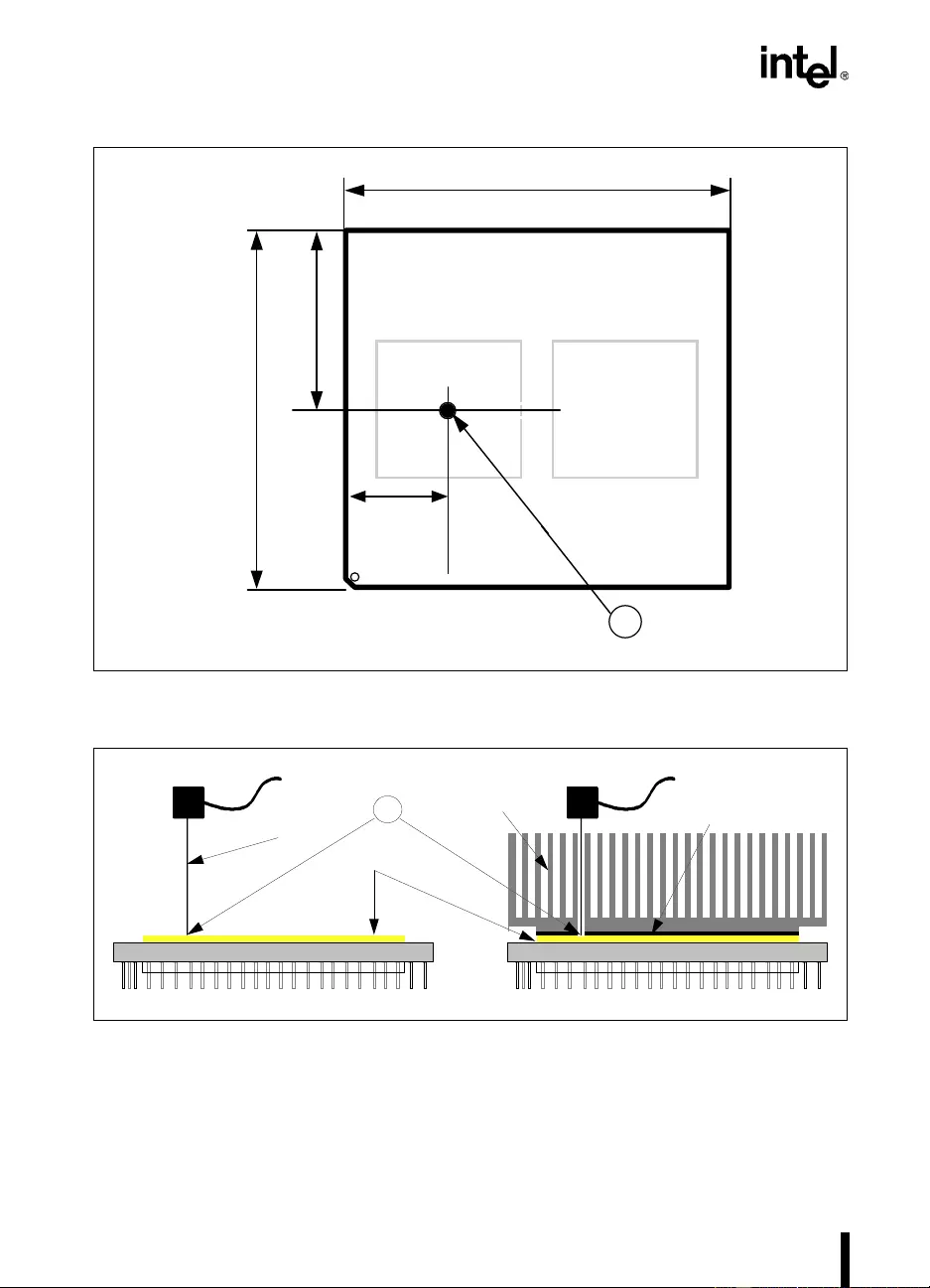

14.1.2. Case Temperature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-1

14.1.3. Thermal Resistance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-3

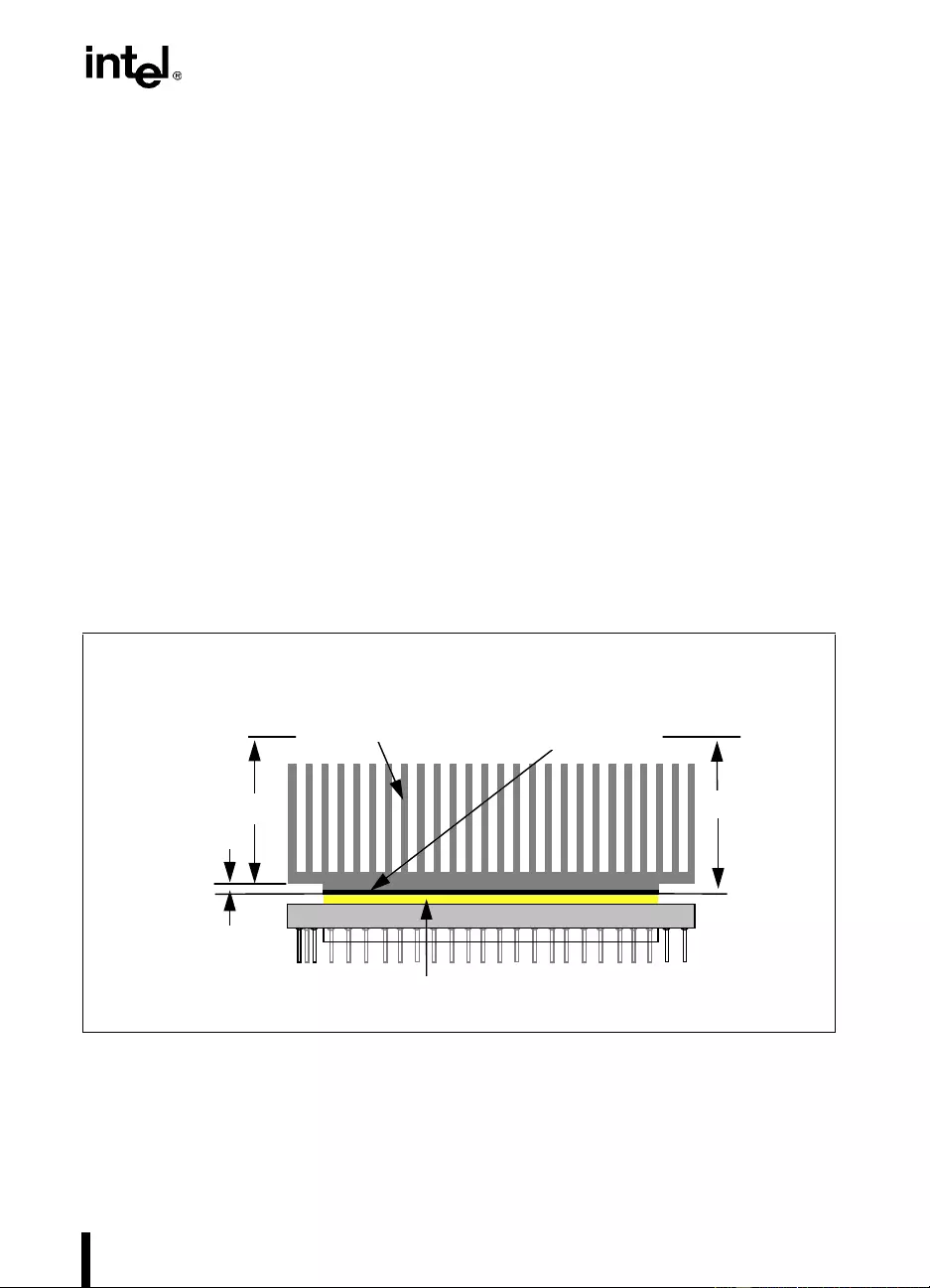

14.2. THERMAL ANALYSIS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-4

CHAPTER 15

MECHANICAL SPECIFICATIONS

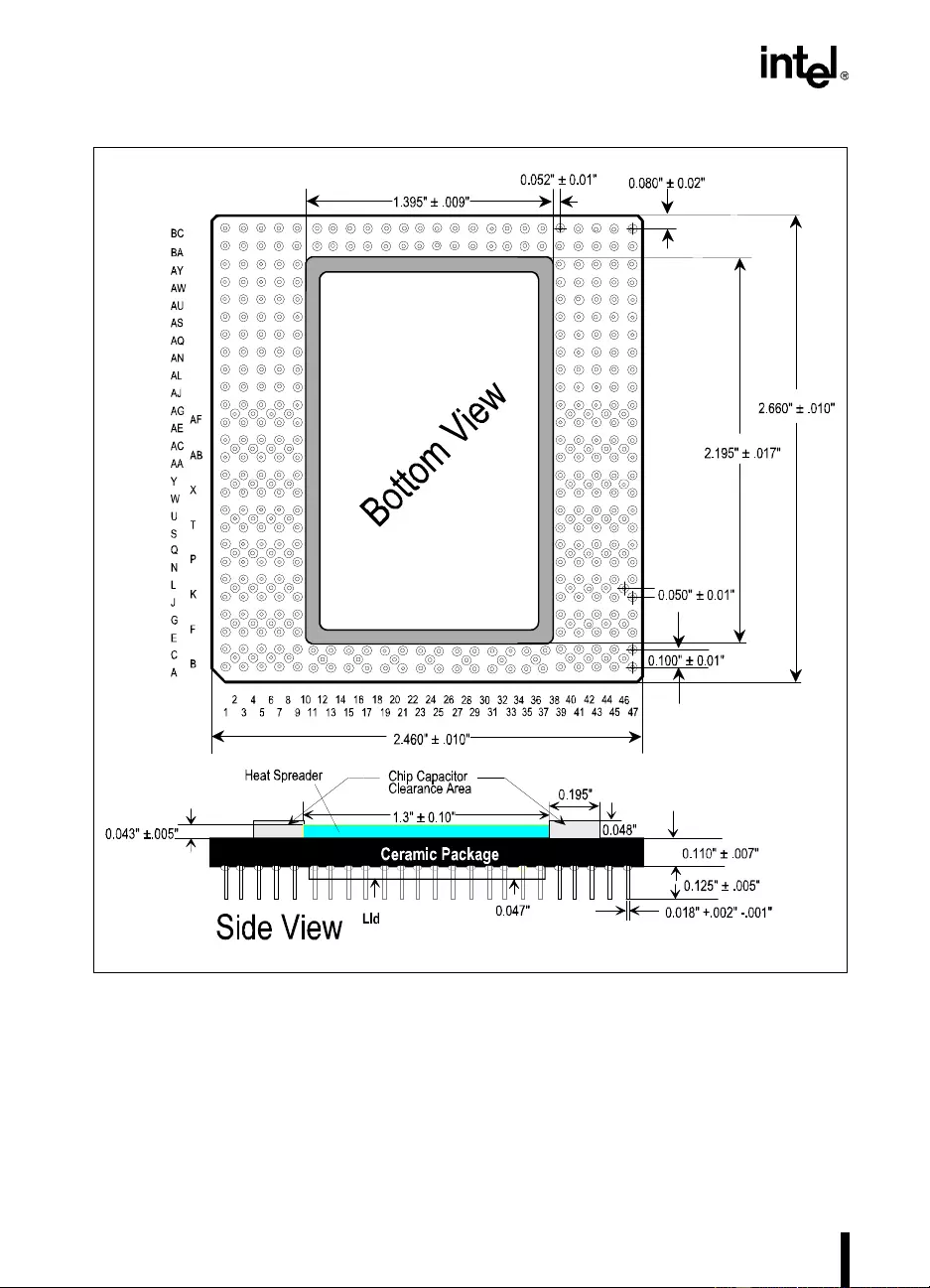

15.1. DIMENSIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-1

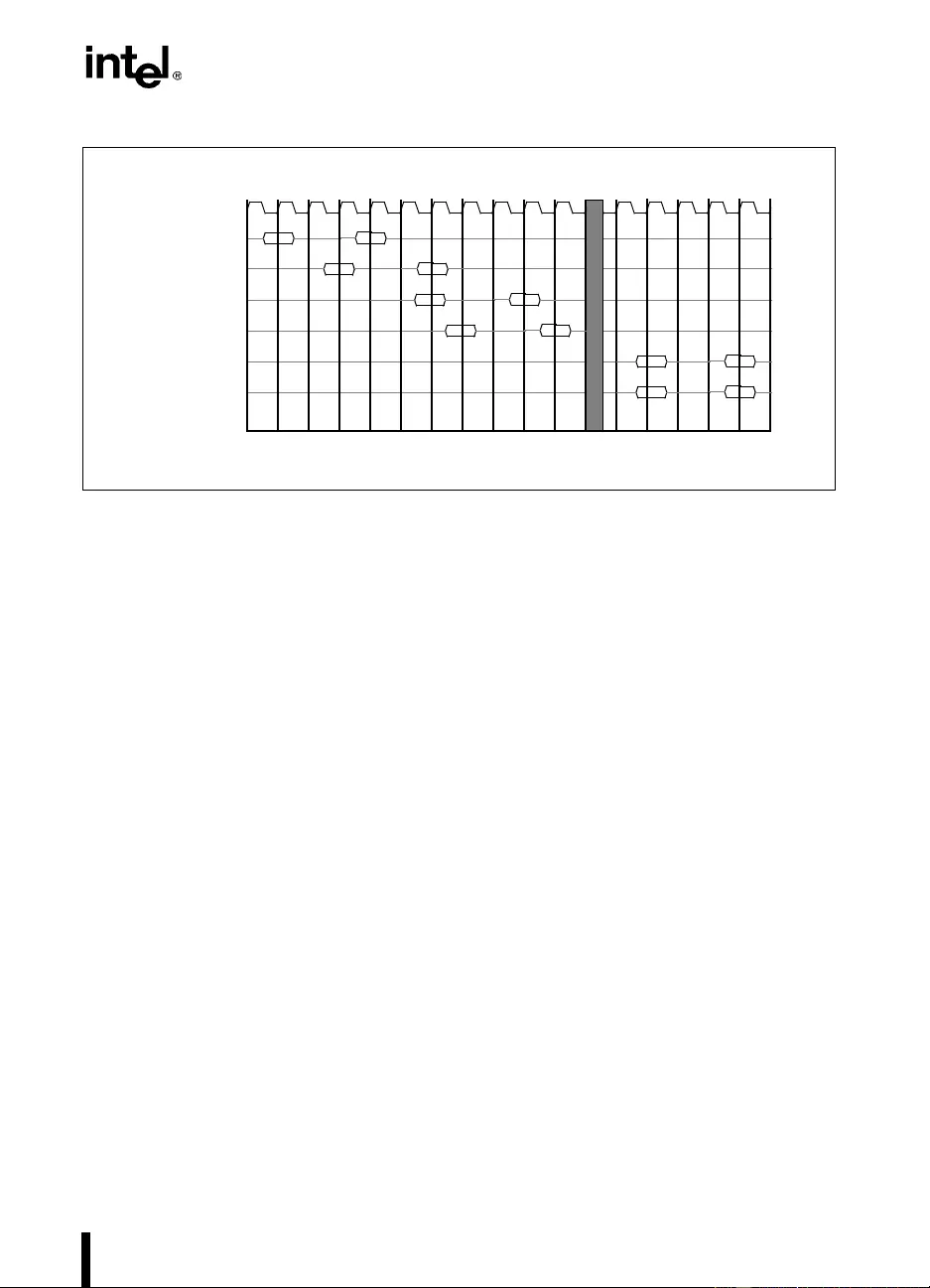

15.2. PINOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-4

CHAPTER 16

TOOLS

16.1. ANALOG MODELING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-1

16.2. IN-TARGET PROBE FOR THE PENTIUM® PRO PROCESSOR (ITP) . . . . . . . . . 16-1

16.2.1. Primary Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-2

16.2.2. Debug Port Connector Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-2

16.2.3. Debug Port Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-2

16.2.4. Signal Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-3

16.2.4.1. Signal Note 1: RESET#, PRDYx#. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-4

16.2.4.2. Signal Note 2: DBRESET# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-4

16.2.4.3. Signal Note 3: POWERON . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-4

16.2.4.4. Signal Note 4: DBINST#. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-4

16.2.4.5. Signal Note 5: TDO and TDI. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-4

16.2.4.6. Signal Note 6: PREQ# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-4

16.2.4.7. Signal Note 7: TRST#. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-5

16.2.4.8. Signal Note 8: TCK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-5

16.2.4.9. Signal Note 9: TMS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-6

16.2.5. Debug Port Layout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-7

16.2.5.1. Signal Quality Notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-9

16.2.5.2. Debug Port Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-9

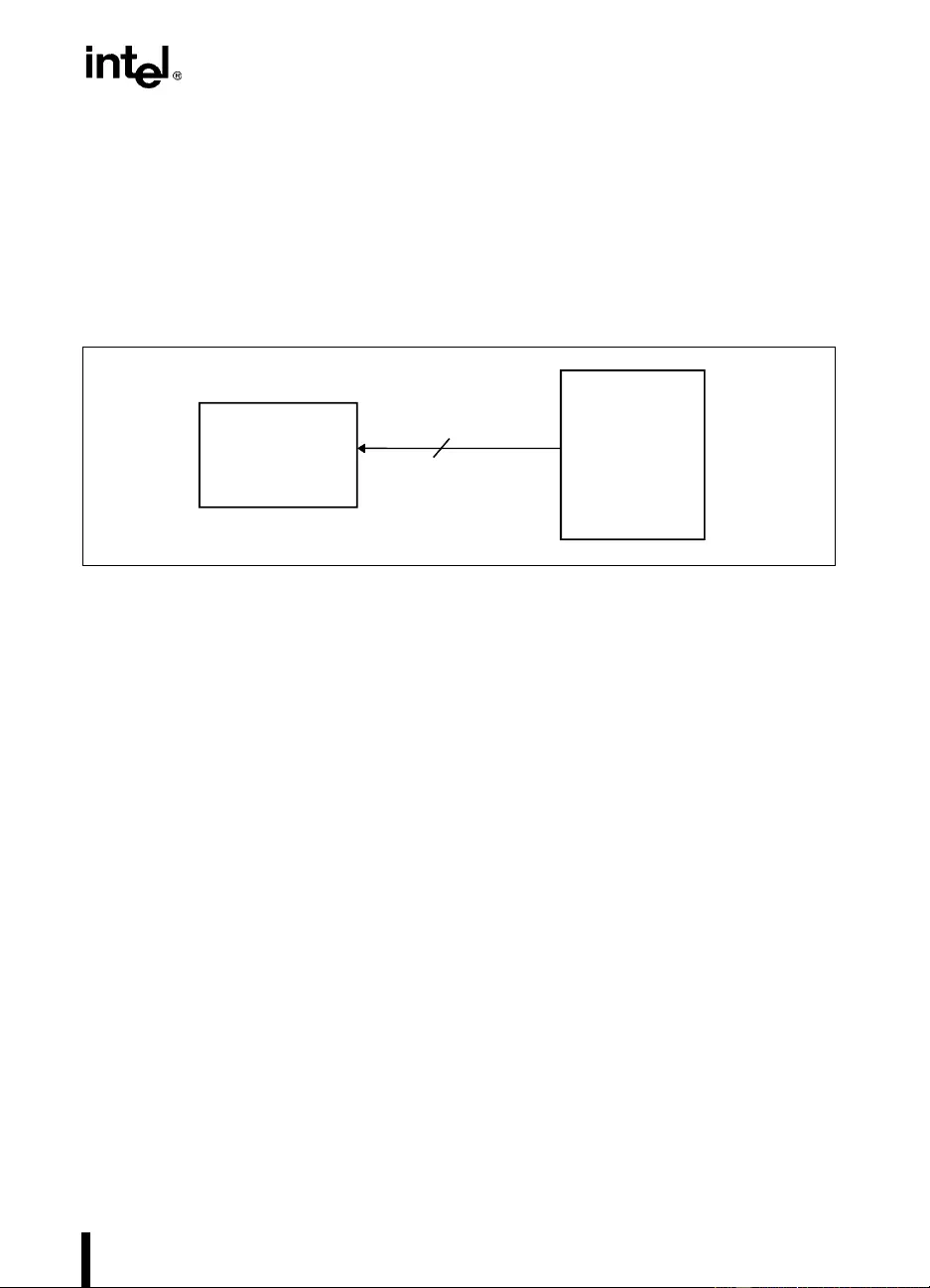

16.2.6. Using Boun dary Scan to Communicate to the P entium® Pro Processor. . . . . 16-10

CHAPTER 17

OVERDRIVE® PROCESSOR SOCKET SPECIFICATION

17.1. INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-1

17.1.1. Terminology. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-1

17.2. MECHANICAL SPECIFICATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-2

17.2.1. Vendor Contacts for Socket 8 and Header 8. . . . . . . . . . . . . . . . . . . . . . . . . . . 17-3

17.2.2. Socket 8 Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-3

17.2.2.1. Socket 8 Pinout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-3

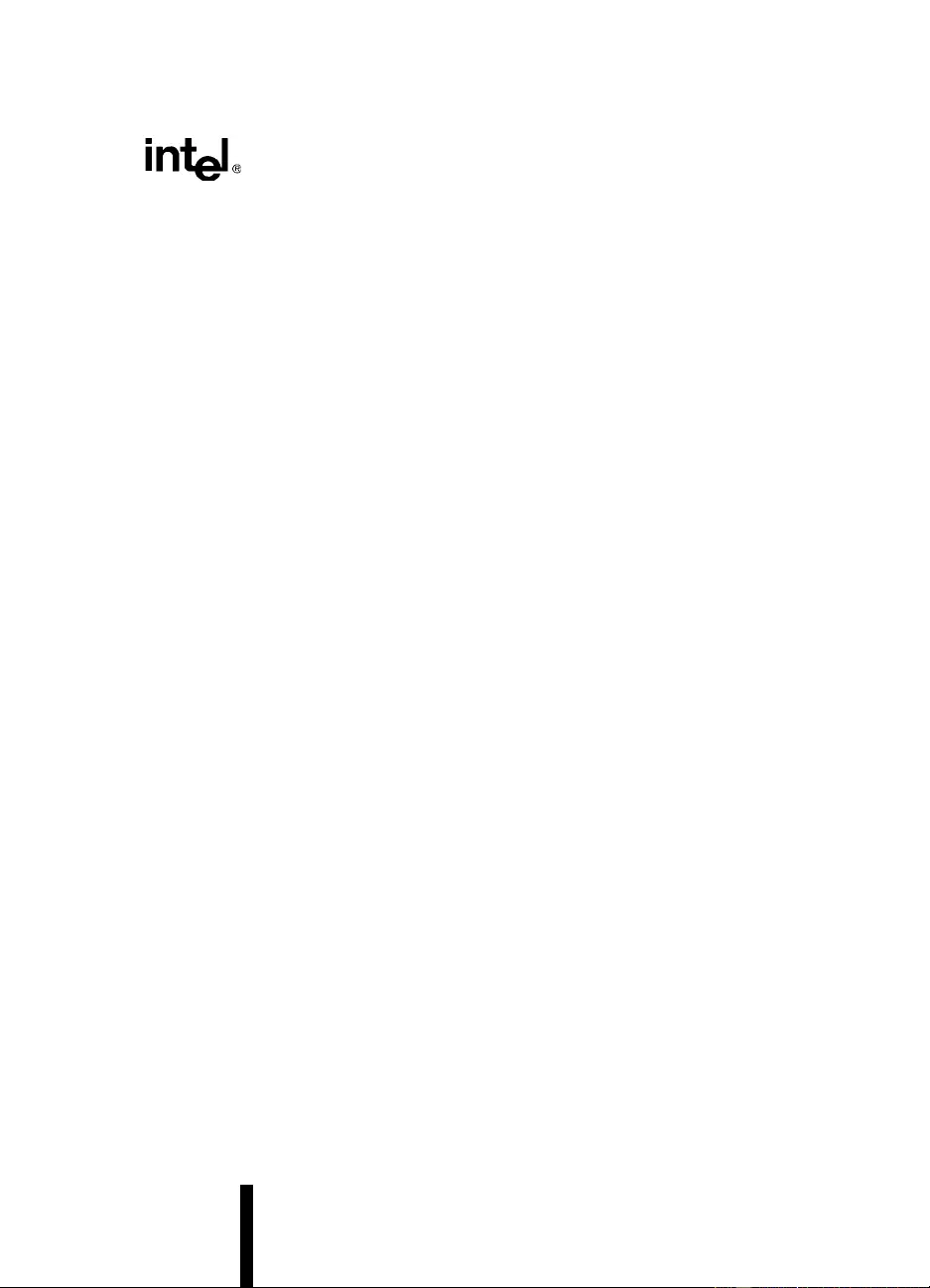

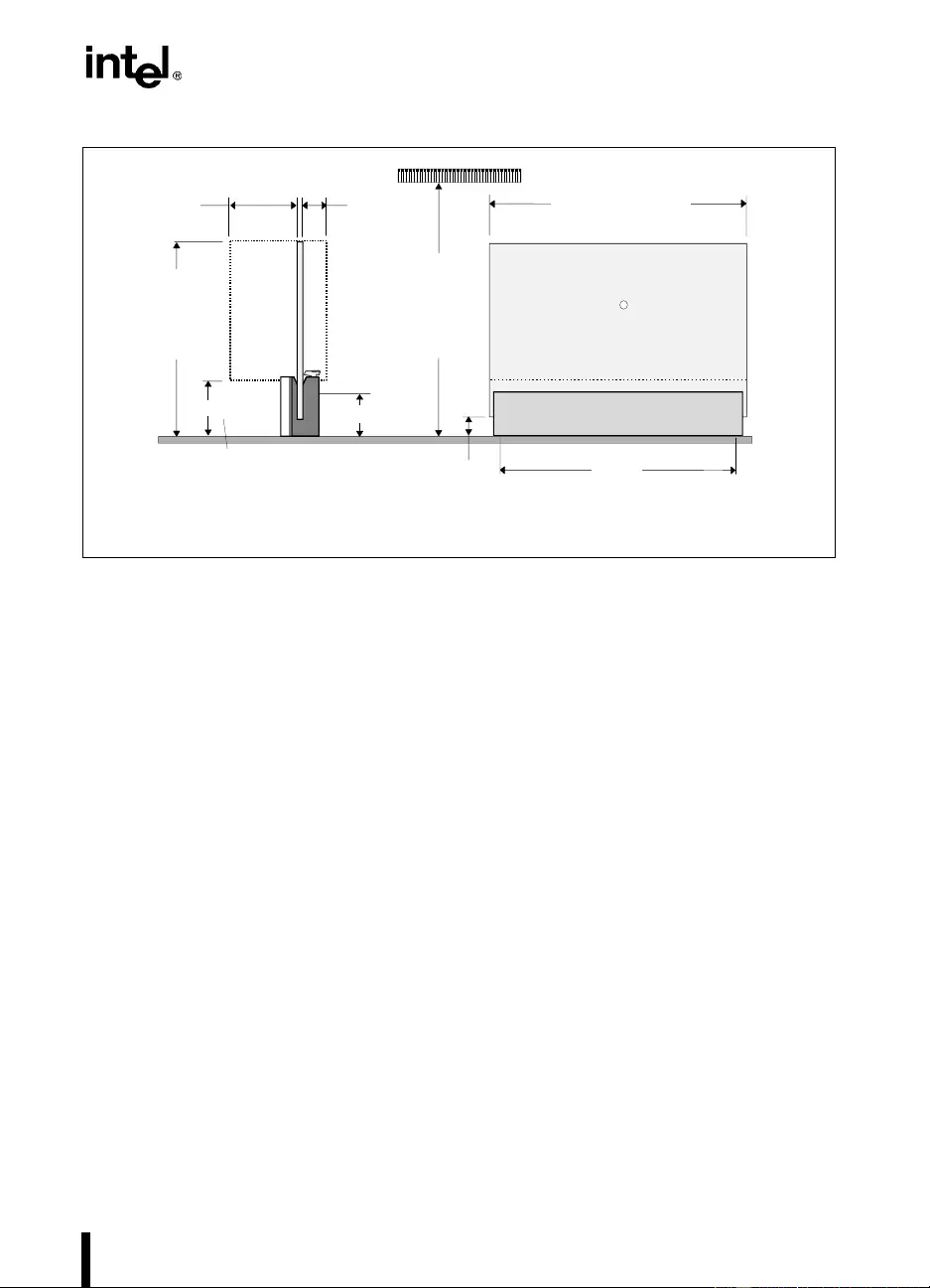

17.2.2.2. Socket 8 Space Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-4

17.2.2.3. Socket 8 Clip Attachment Tabs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-7

TABLE OF CONTENTS

xii

PAGE

17.2.3. OverDrive® Voltage Regulator Module Definition . . . . . . . . . . . . . . . . . . . . . . . .17-8

17.2.3.1. OverDrive® VRM Requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-8

17.2.3.2. OverDrive® VRM Location . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-8

17.2.3.3. OverDrive® VRM Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-8

17.2.3.4. OverDrive® VRM Space Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 7-10

17.3. FUNCTIONAL OPERATION OF OVERDRIVE® PROCESSOR SIGNALS . . . . . 17-11

17.3.1. Fan/Heatsink Power (VCC5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-11

17.3.2. Upgrade Present Signal (UP#) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-11

17.3.3. BIOS Considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 7-13

17.3.3.1. OverDrive® processor CPUID. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-14

17.3.3.2. Common Causes of Upgradability Problems due to BIOS. . . . . . . . . . . . . .17-14

17.4. OVERDRIVE® PROCESSOR ELECTRICAL SPECIFICATIONS . . . . . . . . . . . . 17-14

17.4.1. D.C. Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-15

17.4.1.1. OverDrive® Processor D.C. Specifications . . . . . . . . . . . . . . . . . . . . . . . . . .17-15

17.4.1.2. OverDrive® VRM D.C. Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-16

17.4.2. OverDrive® Processor Decoupling Requirements. . . . . . . . . . . . . . . . . . . . . . .17-16

17.4.3. A.C. Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-17

17.5. THERMAL SPECIFICATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-17

17.5.1. OverDrive® Processor Cooling Requirements. . . . . . . . . . . . . . . . . . . . . . . . . .17-17

17.5.1.1. Fan/heatsink Cooling Solution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-17

17.5.2. OEM Processor Cooling Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-17

17.5.3. OverDrive® VRM Cooling Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-18

17.5.4. Thermal Equations and Data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-18

17.6. CRITERIA FOR OVERDRIVE® PROCESSOR . . . . . . . . . . . . . . . . . . . . . . . . . . 17-19

17.6.1. Related Documents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-20

17.6.2. Electrical Criteria . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-20

17.6.2.1. OverDrive® Processor Electrical Criteria. . . . . . . . . . . . . . . . . . . . . . . . . . . .17-20

17.6.2.2. Pentium® Pro Processor Electrical Criteria. . . . . . . . . . . . . . . . . . . . . . . . . .17-22

17.6.3. Thermal Criteria. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-22

17.6.3.1. OverDrive® Processor Cooling Requirements (Systems Testing Only) . . . .17-22

17.6.3.2. Pentium® Pro Processor Cooling Requirements (Systems Testing Only) . .17-23

17.6.3.3. Voltage Regulator Modules (Systems Employing a Header 8 Only) . . . . . .17-23

17.6.4. Mechanical Criteria . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-23

17.6.4.1. OverDrive® Processor Clearance and Airspace Requirements . . . . . . . . . .17-23

17.6.4.2. OverDrive® VRM Clearance and Airspace Requirements . . . . . . . . . . . . . .1 7-24

17.6.5. Functional Criteria . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-24

17.6.5.1. Software Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-24

17.6.5.2. BIOS Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-24

17.6.6. End User Criteria. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-25

17.6.6.1. Qualified OverDrive® Processor Components . . . . . . . . . . . . . . . . . . . . . . .17-25

17.6.6.2. Visibility and Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-25

17.6.6.3. Jumper Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-25

17.6.6.4. BIOS Changes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-25

17.6.6.5. Documentation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-25

17.6.6.6. Upgrade Removal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-25

APPENDIX A

SIGNALS REFERENCE

A.1. ALPHABETICAL SIGNALS REFERENCE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

A.1.1. A[35:3]# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-1

A.1.2. A20M# (I). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

A.1.3. ADS# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

A.1.4. AERR# (I/O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

xiii

TABLE OF CON TENTS

PAGE

A.1.5. AP[1:0]# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

A.1.6. ASZ[1:0]# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

A.1.7. ATTR[7:0]# (I/O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

A.1.8. BCLK (I). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

A.1.9. BE[7:0]# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

A.1.10. BERR# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-6

A.1.11. BINIT# (I/O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-6

A.1.12. BNR# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-7

A.1.13. BP[3:2]# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-7

A.1.14. BPM[1:0]# (I/O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-7

A.1.15. BPRI# (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-8

A.1.16. BR0#(I/O), BR[3:1]# (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-8

A.1.17. BREQ[3:0]# (I/O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-9

A.1.18. D[63:0]# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-10

A.1.19. DBSY# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-10

A.1.20. DEFER# (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-10

A.1.21. DEN# (I/0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-11

A.1.22. DEP[7:0]# (I/O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-11

A.1.23. DID[7:0]# (I/O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-11

A.1.24. DRDY# (I/O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-12

A.1.25. DSZ[1:0]# (I/O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-12

A.1.26. EXF[4:0]# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-13

A.1.27. FERR# (O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-13

A.1.28. FLUSH# (I). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-13

A.1.29. FRCERR(I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-14

A.1.30. HIT# (I/O), HITM#(I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-14

A.1.31. IERR# (O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-15

A.1.32. IGNNE# (I). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-15

A.1.33. INIT# (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-15

A.1.34. INTR (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-16

A.1.35. LEN[1:0]# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-16

A.1.36. LINT[1:0] (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-16

A.1.37. LOCK# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-17

A.1.38. NMI (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-17

A.1.39. PICCLK (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-17

A.1.40. PICD[1:0] (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-17

A.1.41. PWR_GD (I). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-18

A.1.42. REQ[4:0]# (I/O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-18

A.1.43. RESET# (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-19

A.1.44. RP# (I/O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-19

A.1.45. RS[2:0]#(I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-20

A.1.46. RSP# (I). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-21

A.1.47. SMI# (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-21

A.1.48. SMMEM# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-21

A.1.49. SPLCK# (I/O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-22

A.1.50. STPCLK# (I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-22

A.1.51. TCK (I). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-22

A.1.52. TDI(I) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-22

A.1.53. TDO (O). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-22

A.1.54. TMS (I). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-22

A.1.55. TRDY# (I). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-23

A.1.56. TRST# (I). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-23

A.2. SIGNAL SUMMARIES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-24

xiv

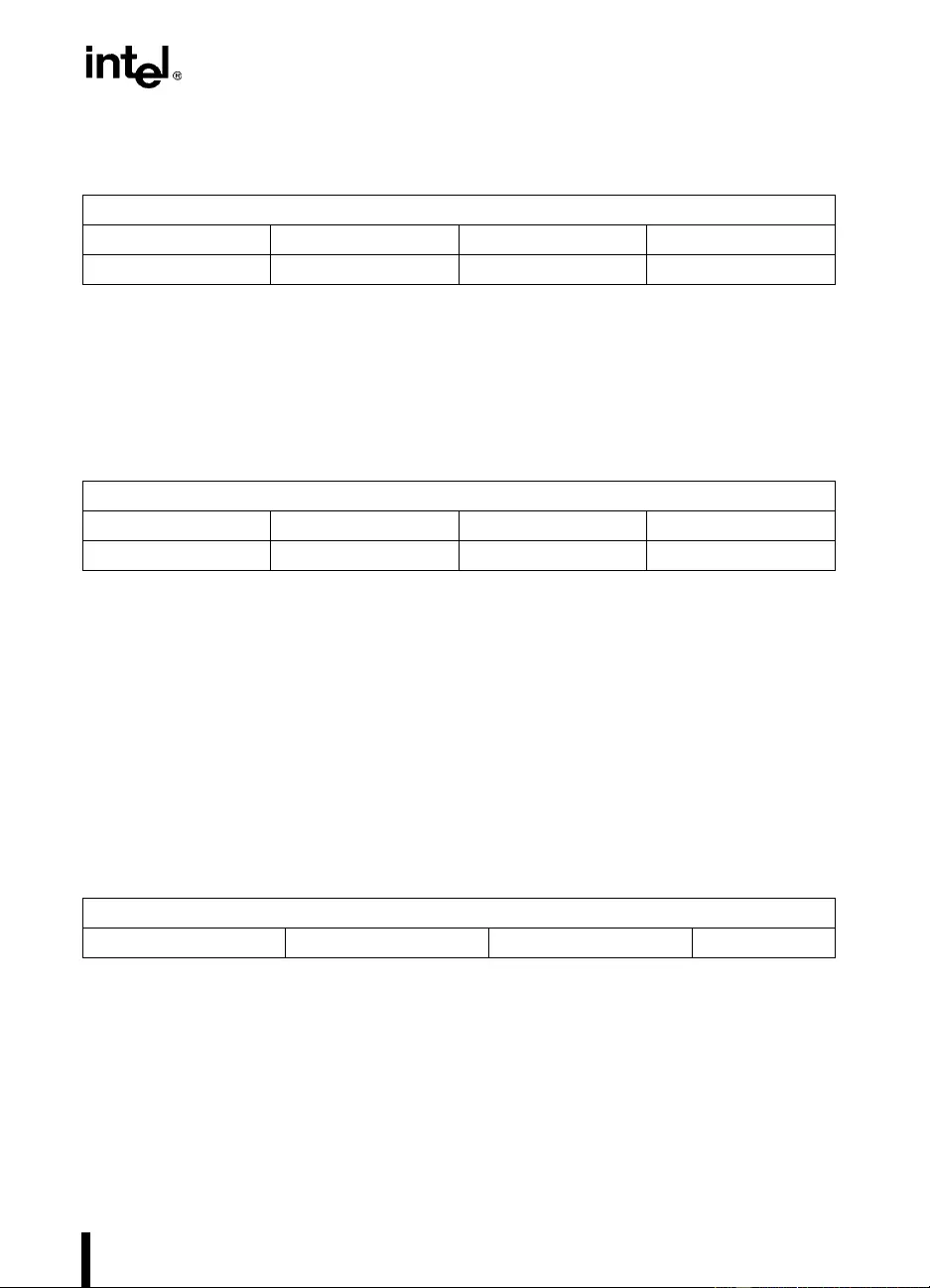

TABLE OF FIGURES

PAGE

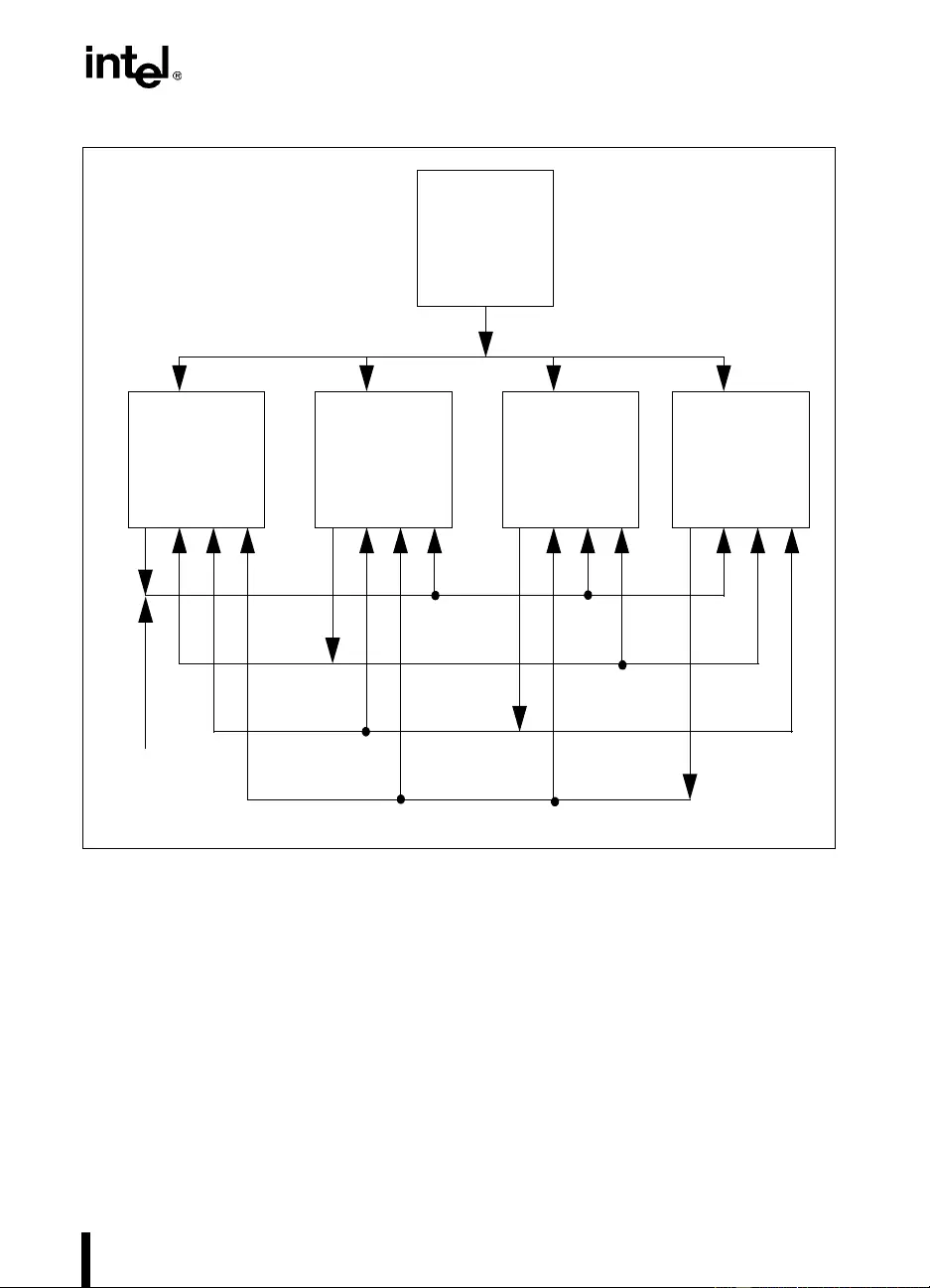

Figure 1-1. The Pentium® Pro Processor In tegrating the CPU, L2 C ache,

APIC and Bus Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

Figure 1-2. Pentium® Pro Processor System Interface Block Diagram. . . . . . . . . . . . . . . .1-5

Figure 2-1. Three Engines Communicating Using an Instruction Pool . . . . . . . . . . . . . . . .2-1

Figure 2-2. A Typical Code Fragment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

Figure 2-3. The Three Core Engines Interface with Memory via Unified Caches. . . . . . . .2-3

Figure 2-4. Inside the Fetch/Decode Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

Figure 2-5. Inside the Dispatch/Execute Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

Figure 2-6. Inside the Retire Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

Figure 2-7. Inside the Bus Interface Unit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

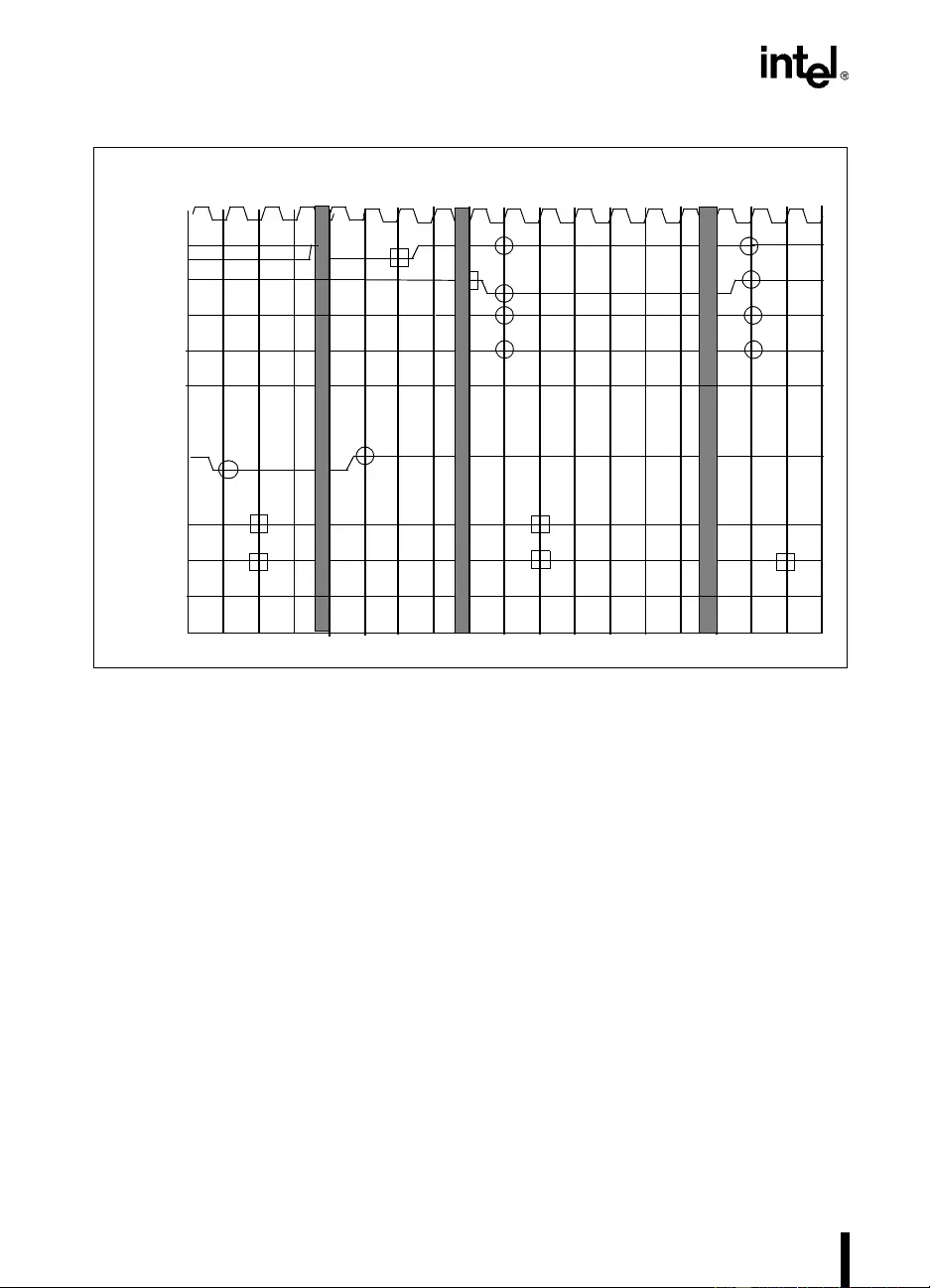

Figure 3-1. Latched Bus Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-3

Figure 3-2. Pentium® Pro Processor Bus Transaction Phases. . . . . . . . . . . . . . . . . . . . . .3-5

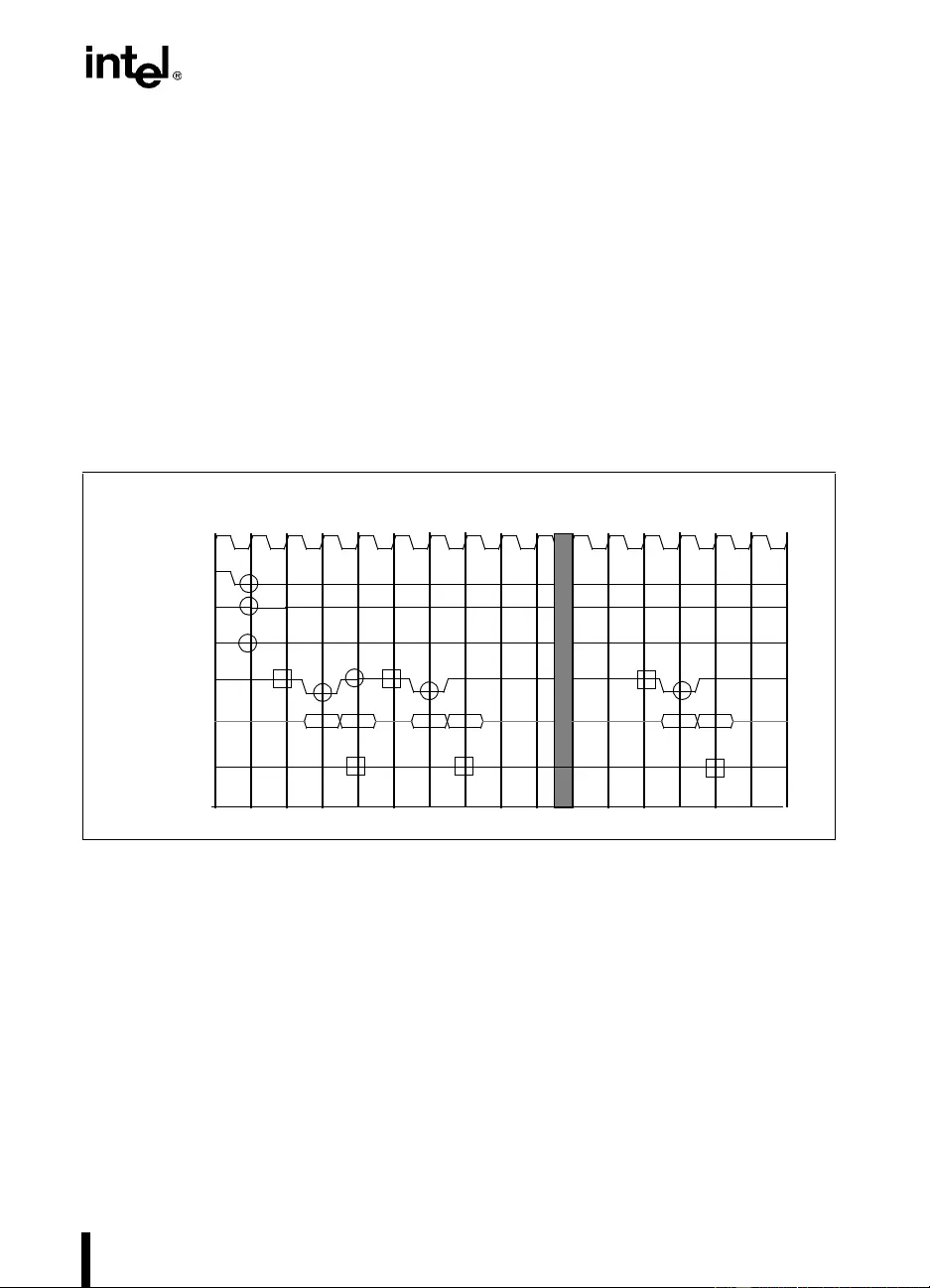

Figure 4-1. BR[3:0]# Physical Interconnection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

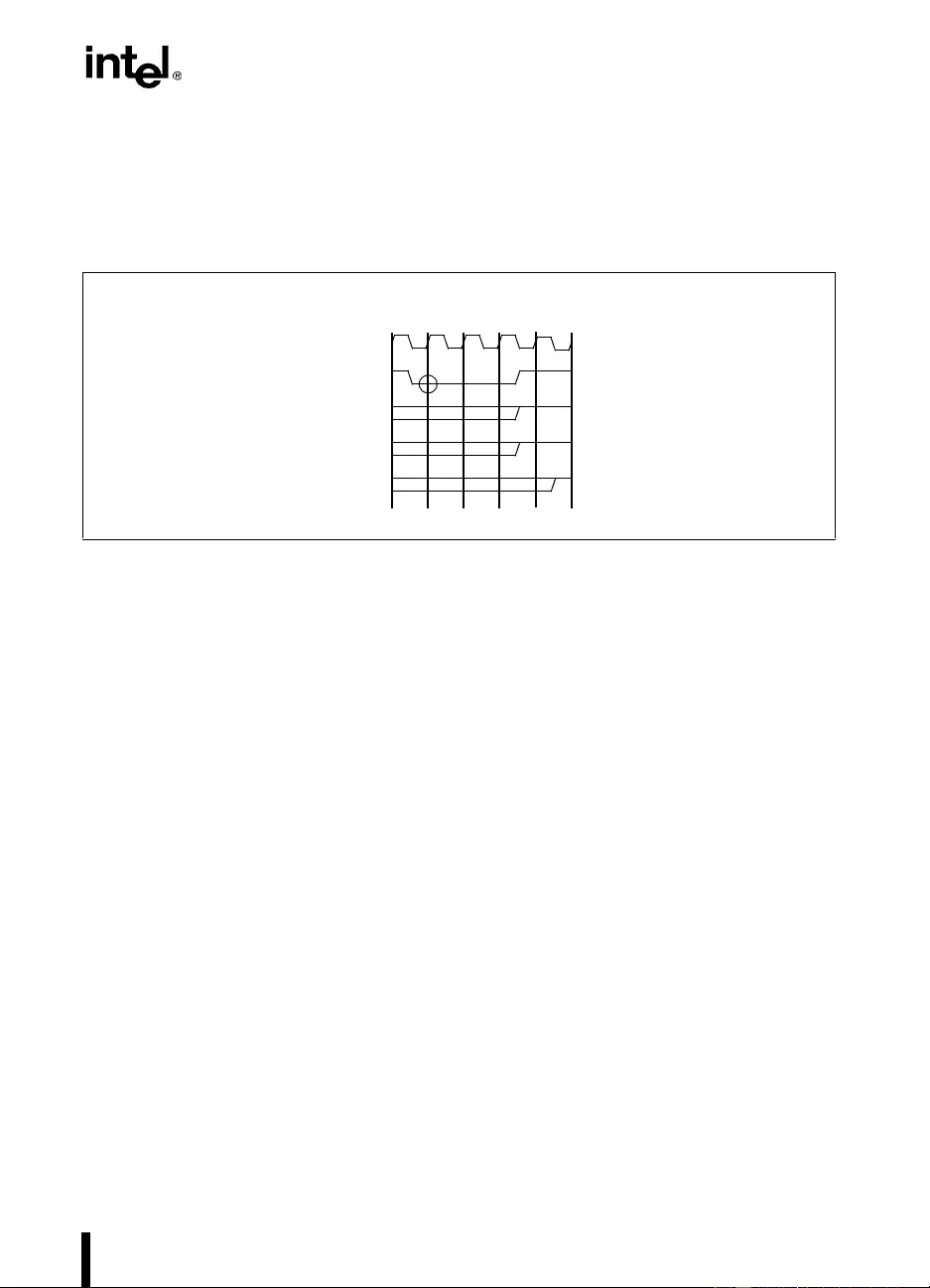

Figure 4-2. Symmetric Arbitration of a Single Agent After RESET# . . . . . . . . . . . . . . . . . .4-6

Figure 4-3. Signal Deassertion After Bus Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-7

Figure 4-4. Delay of Transaction Generation After Reset. . . . . . . . . . . . . . . . . . . . . . . . . .4-8

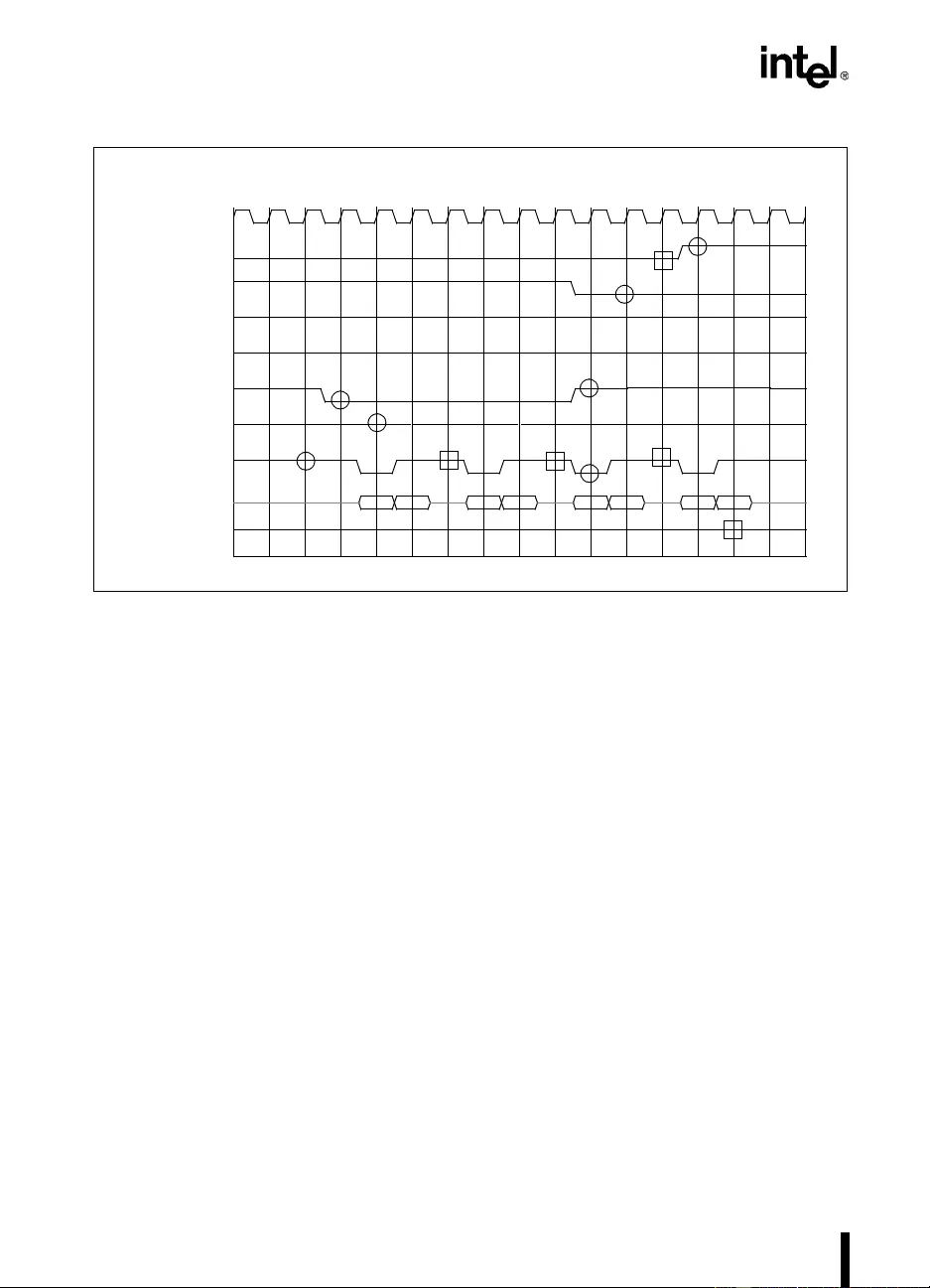

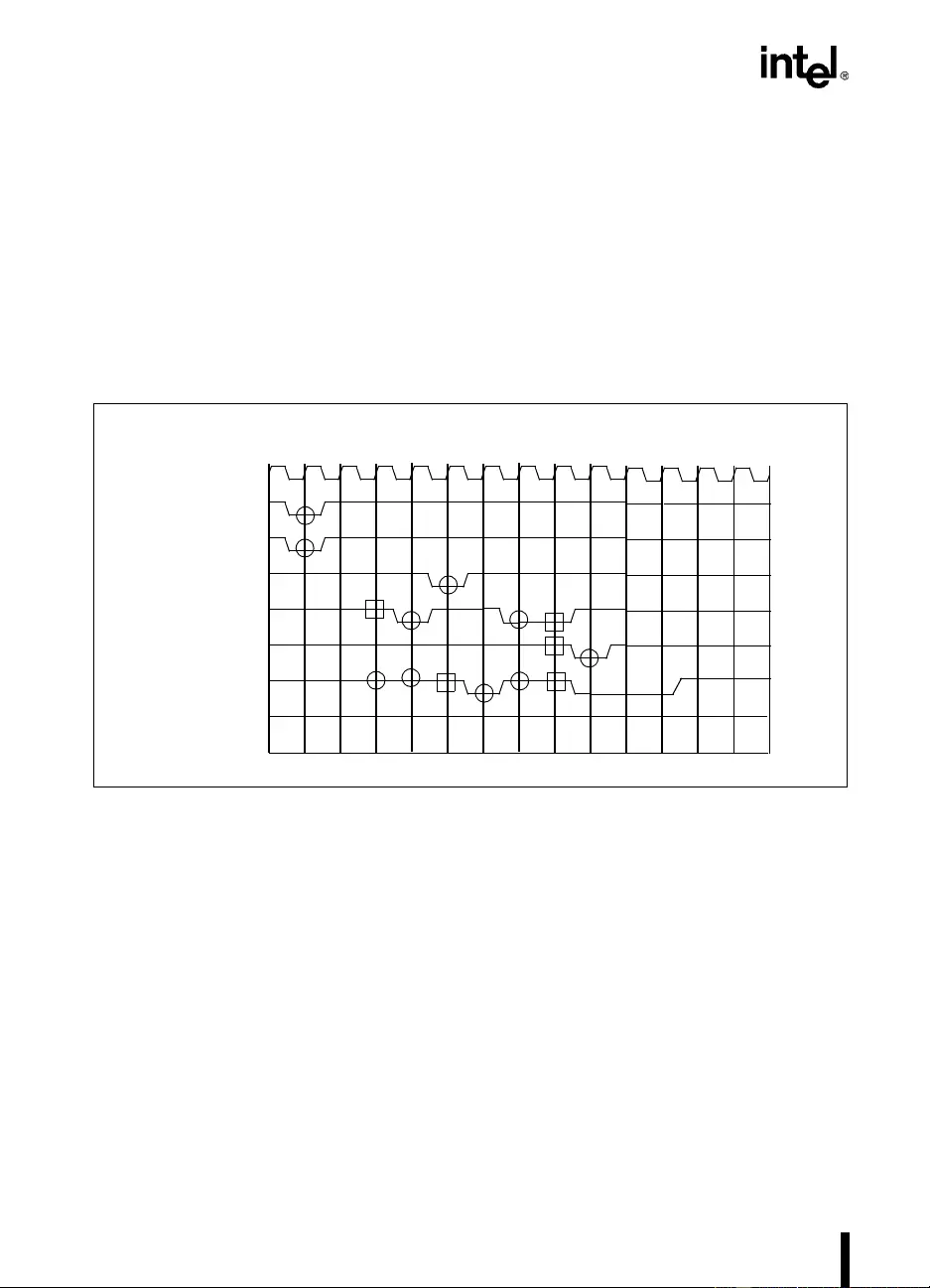

Figure 4-5. Symmetric Bus Arbitration with no LOCK#. . . . . . . . . . . . . . . . . . . . . . . . . . . .4-9

Figure 4-6. Symmetric Arbitration with no Transaction Generation . . . . . . . . . . . . . . . . .4-11

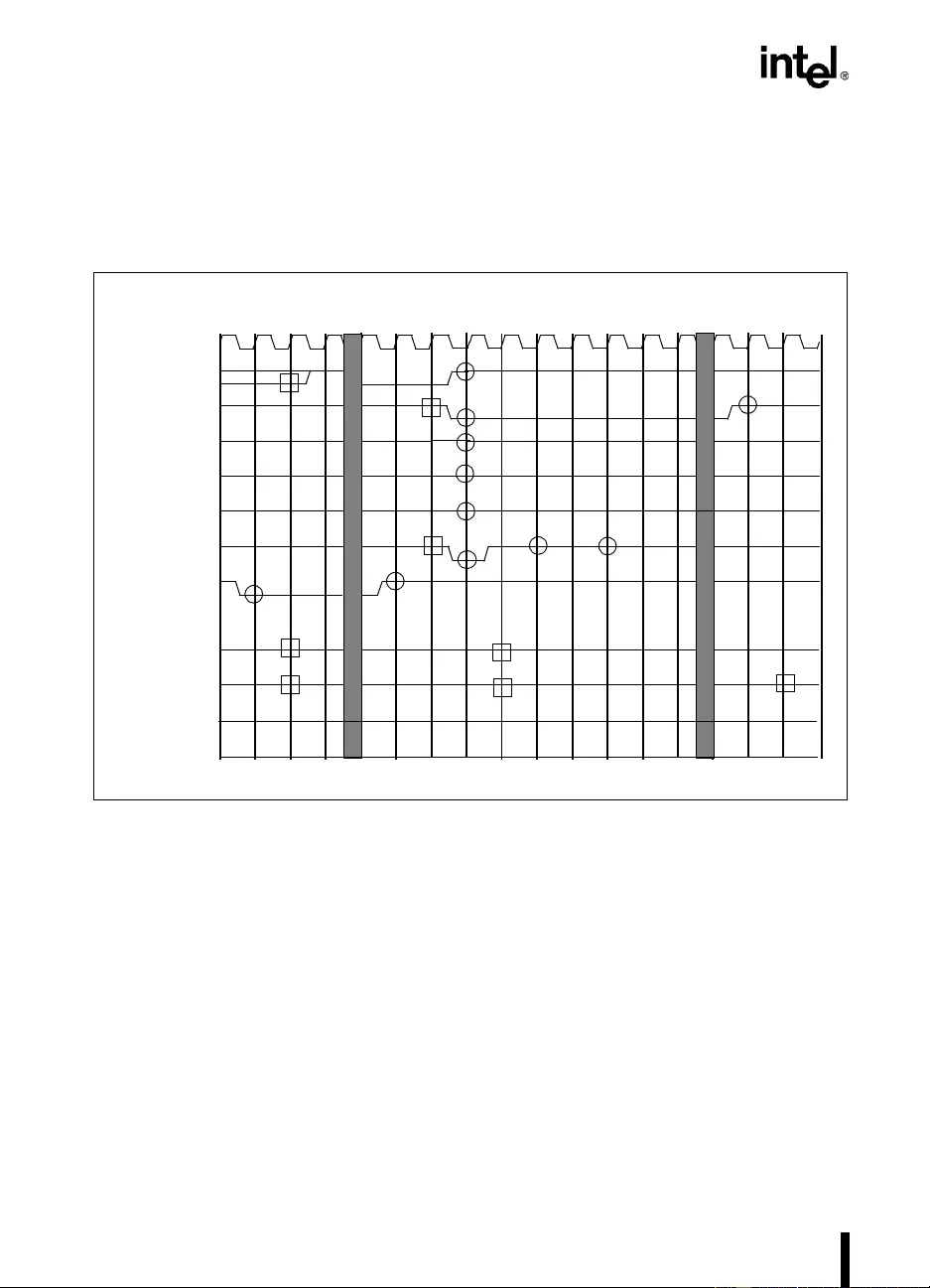

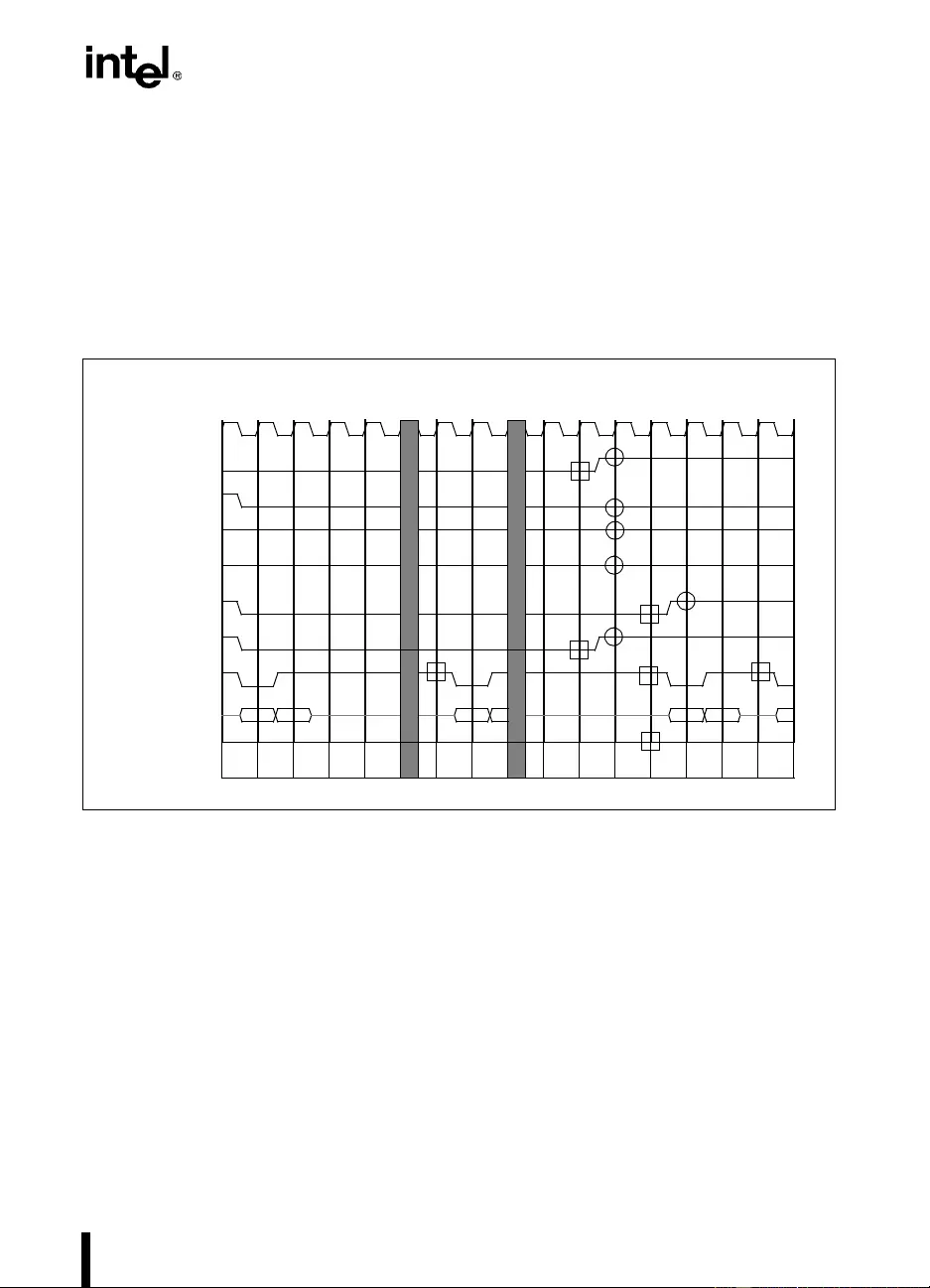

Figure 4-7. Bus Exchange Among Symmetric and Priority Agent with no LOCK# . . . . . .4-12

Figure 4-8. Symmetric and Priority Bus Exchange During LOCK#. . . . . . . . . . . . . . . . . .4-13

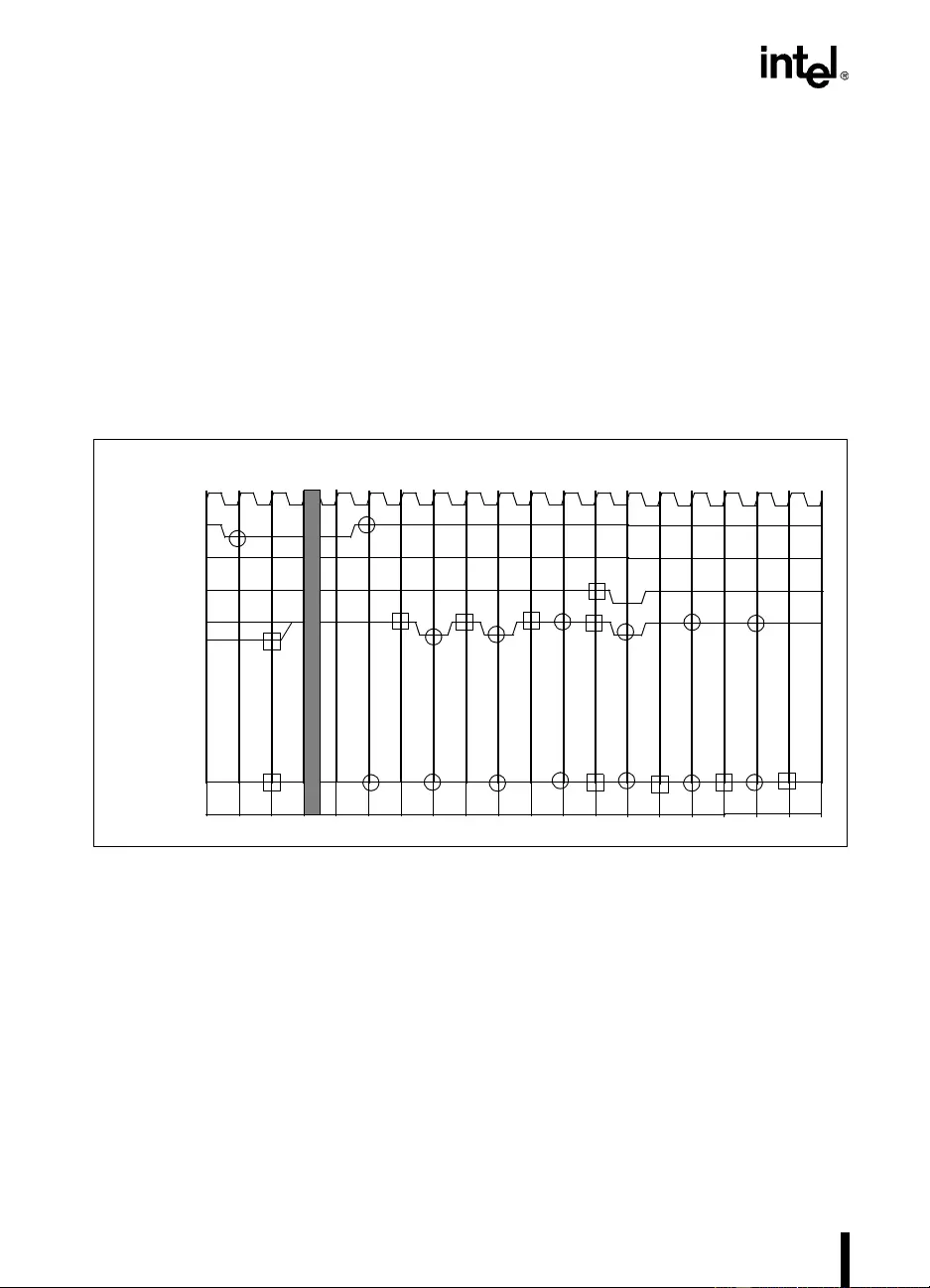

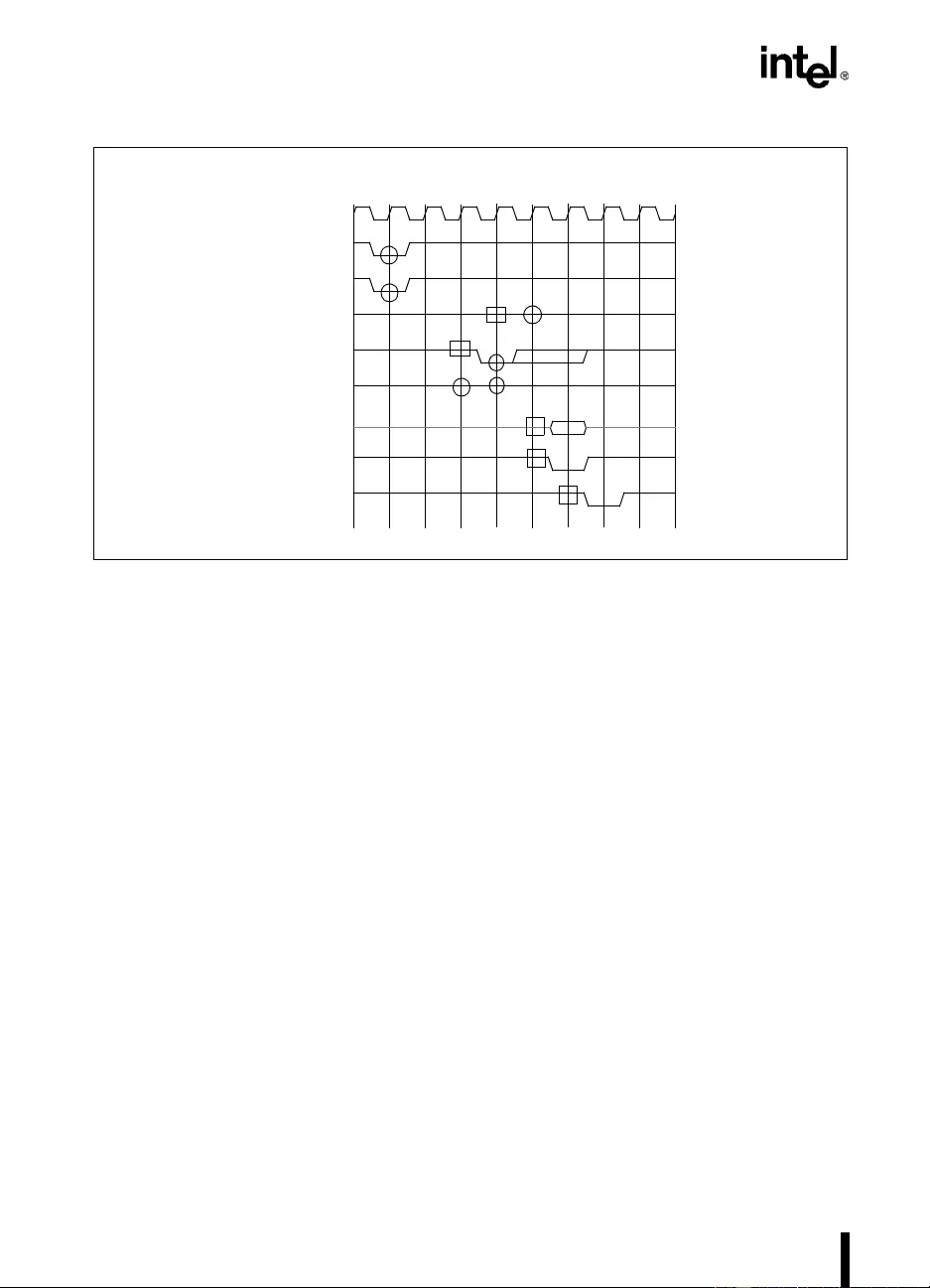

Figure 4-9. BNR# Sampling After RESET#. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-14

Figure 4-10. BNR# Sampling After ADS#. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-15

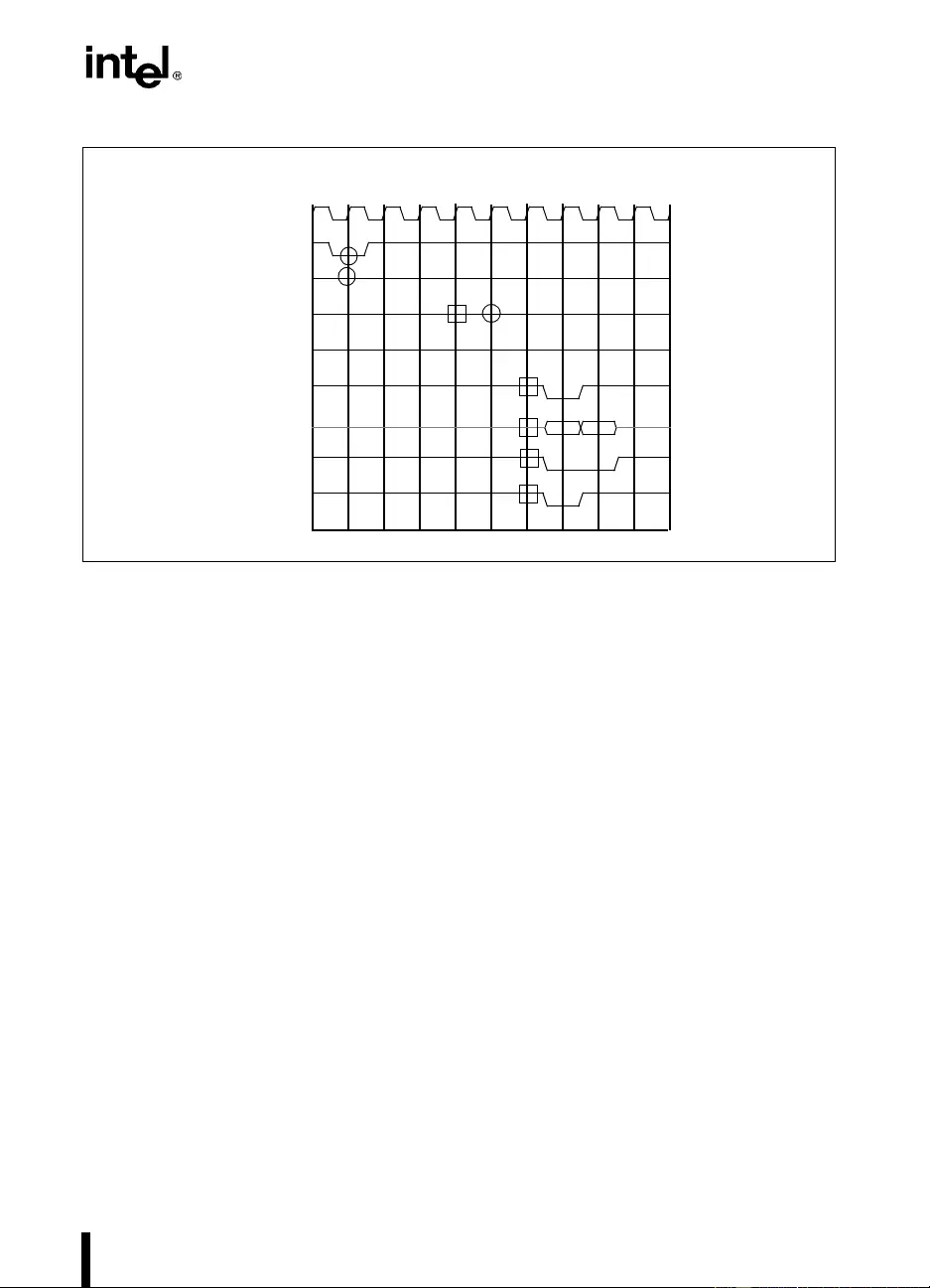

Figure 4-11. Request Generation Phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-19

Figure 4-12. Four-C lock Snoop Phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-22

Figure 4-13. Snoop Phase Stall Due to a Slower Agent. . . . . . . . . . . . . . . . . . . . . . . . . . .4-23

Figure 4-14. RS[2:0]# Activation with no TRDY# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-27

Figure 4-15. RS[2:0]# Activation with Request Initiated TRDY#. . . . . . . . . . . . . . . . . . . . .4-28

Figure 4-16. RS[2:0]# Activation with Snoop Initiated TRDY# . . . . . . . . . . . . . . . . . . . . . .4-29

Figure 4-17. RS[2:0]# Activation After Two TRDY# Assertions . . . . . . . . . . . . . . . . . . . . .4-30

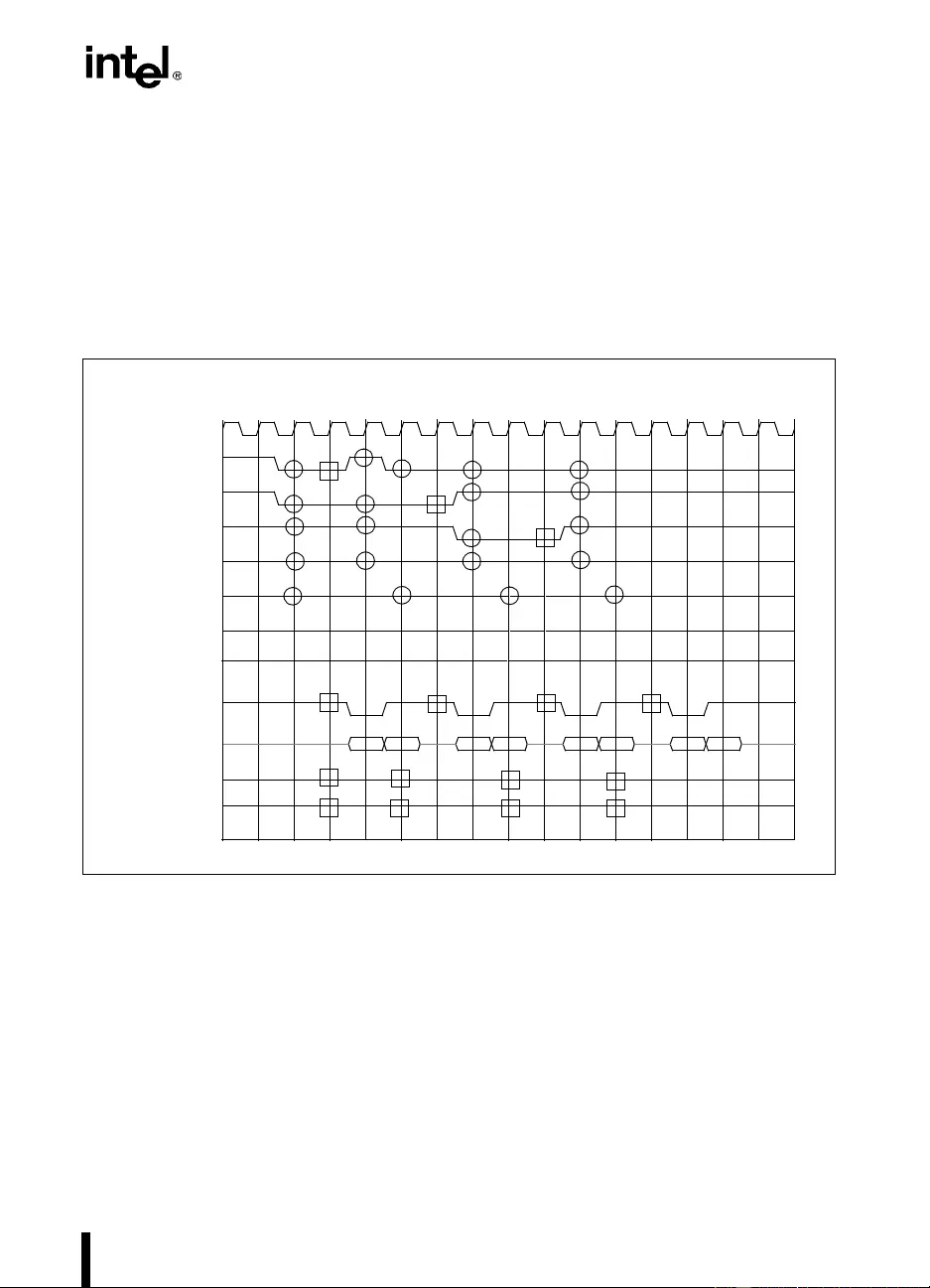

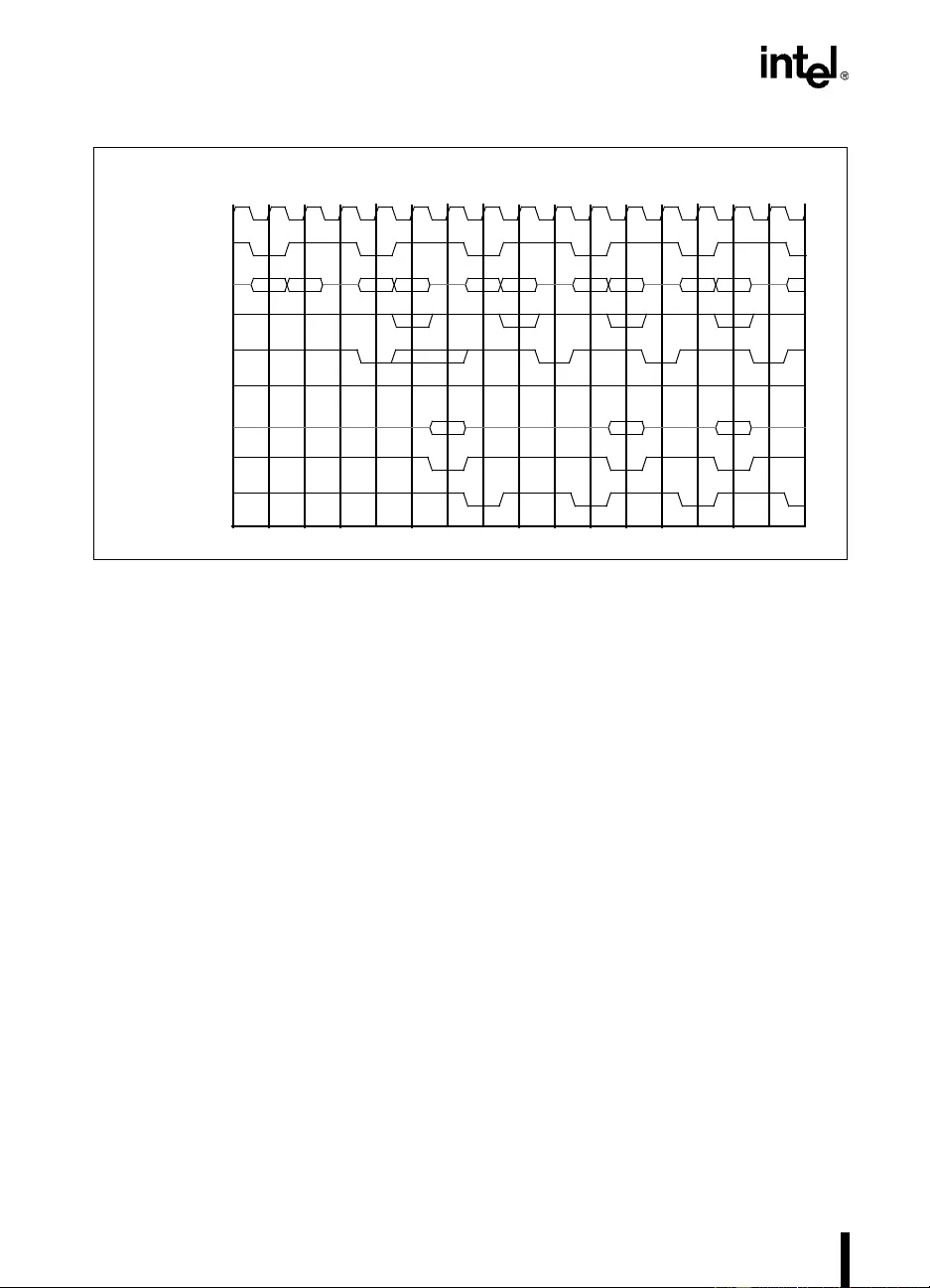

Figure 4-18. Request Initiated Data Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-34

Figure 4-19. Response Initiated Data Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-35

Figure 4-20. Snoop Initiated Data Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-36

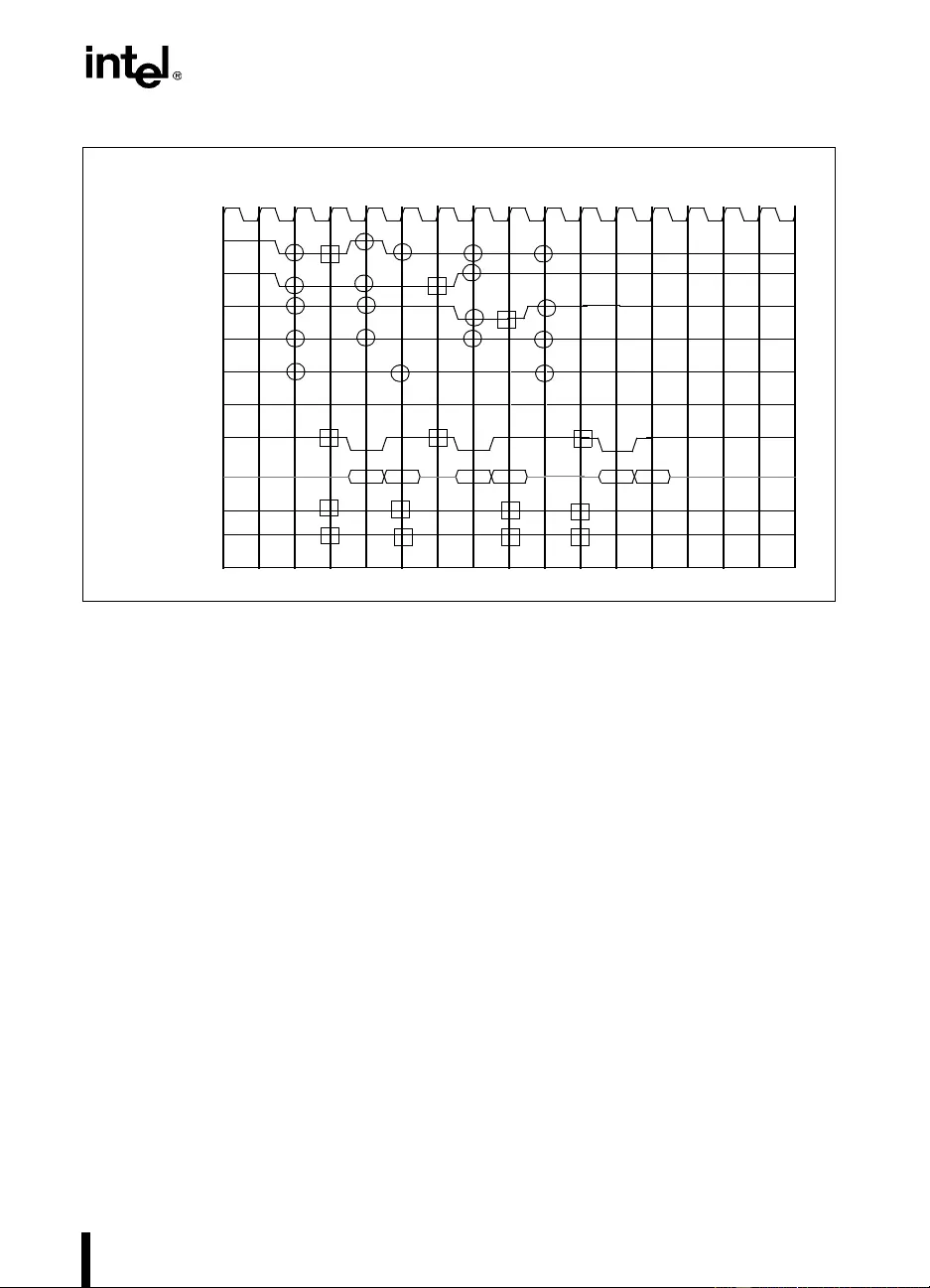

Figure 4-21. Full Speed Read Partial Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-37

Figure 4-22. Relaxed DBSY# Deassertion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-38

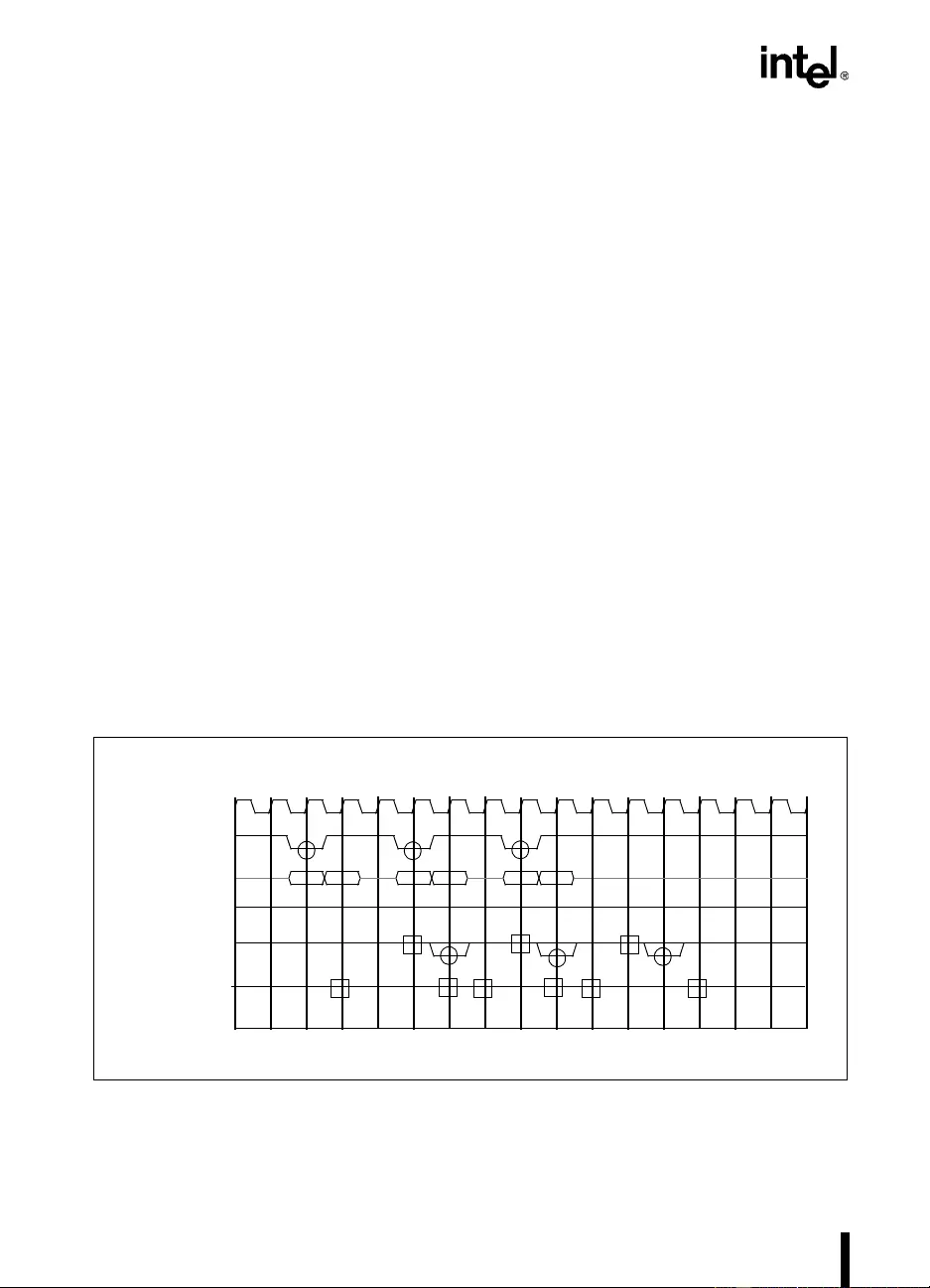

Figure 4-23. Full Speed Read Line Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-39

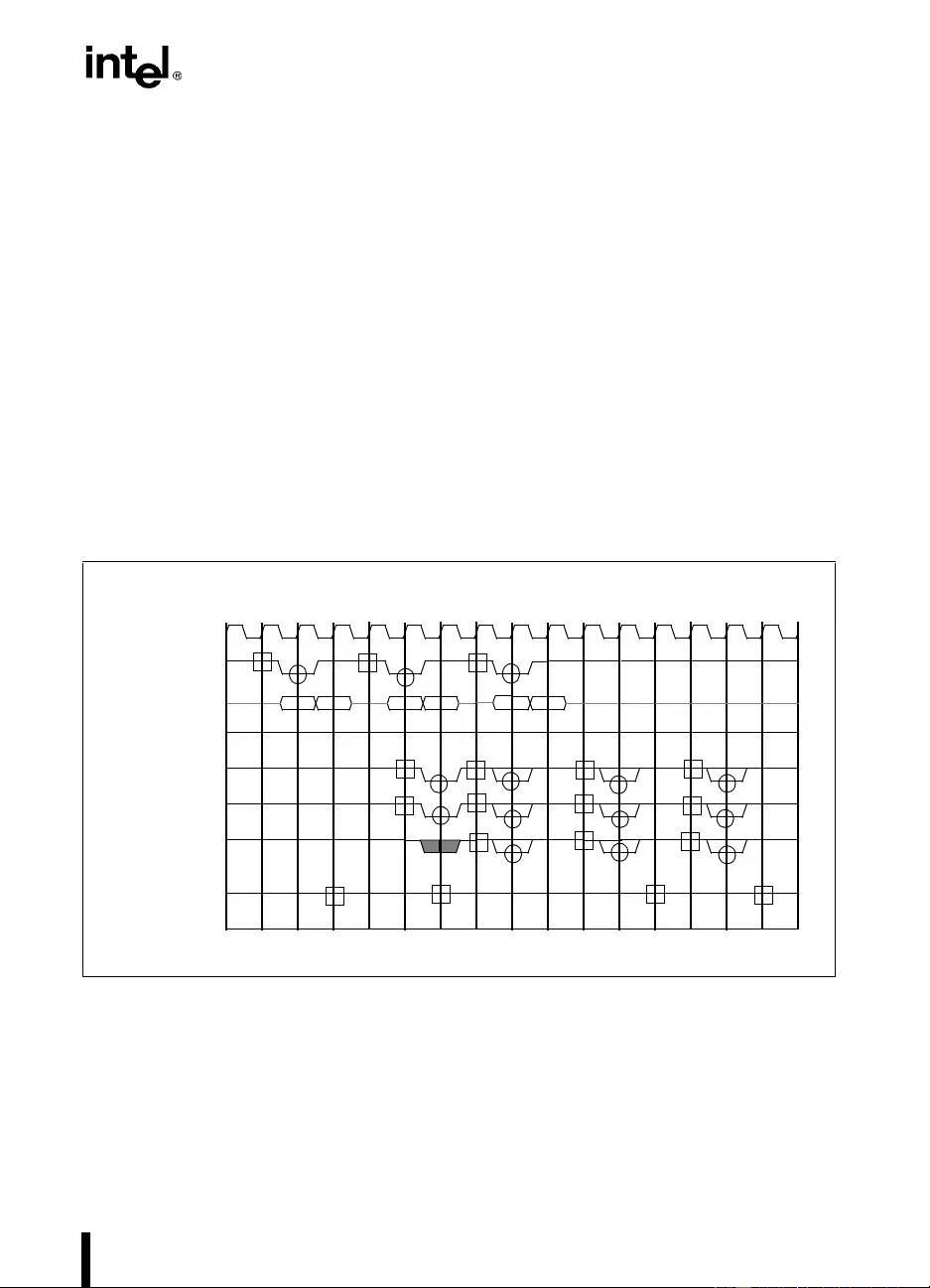

Figure 4-24. Full Speed Write Partial Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-40

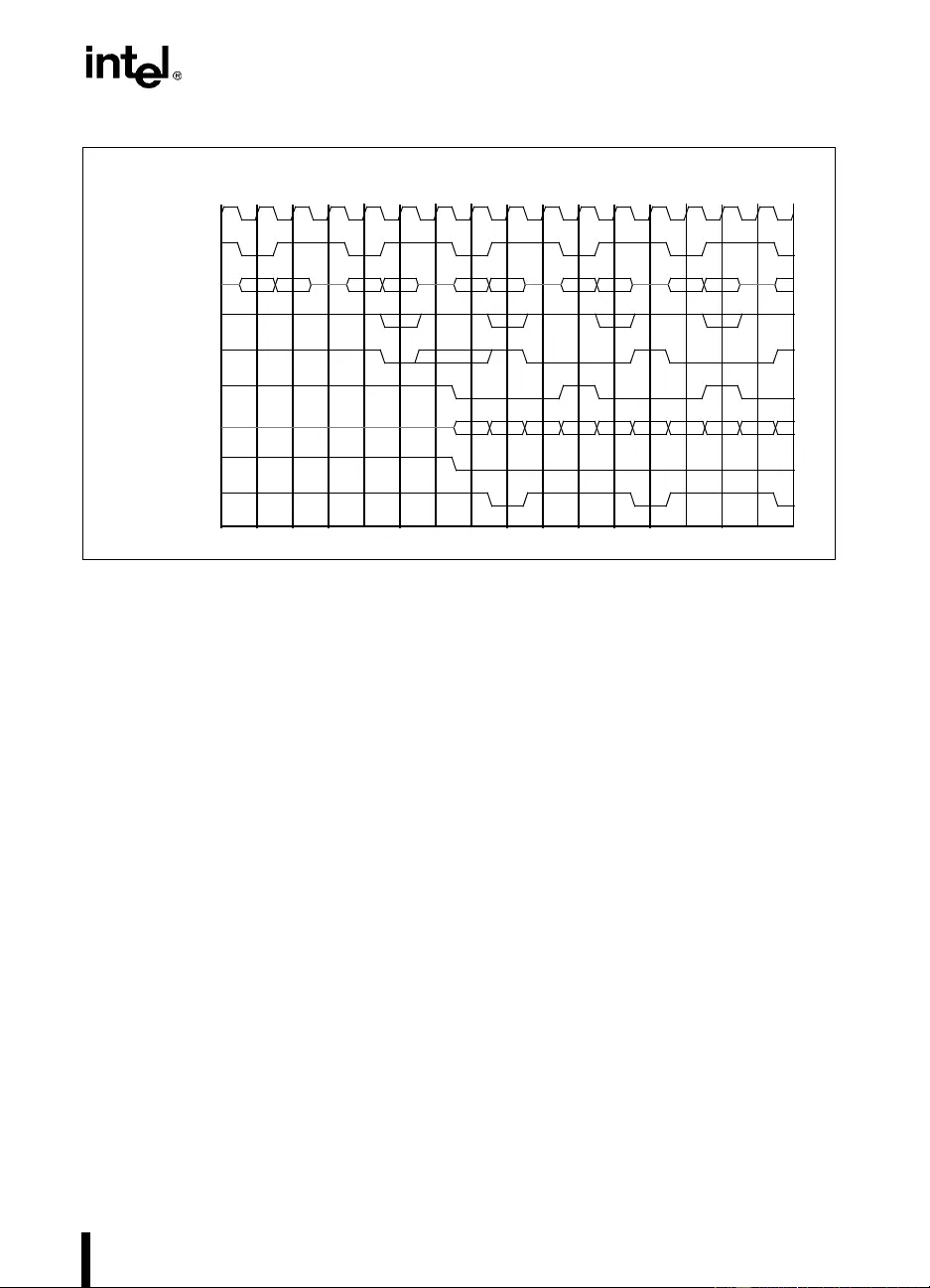

Figure 4-25. Full Speed Write Line Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-41

Figure 5-1. Bus Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

Figure 5-2. Response Responsibility Pickup Effect on an Outstanding Invalidation

Transaction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-15

Figure 5-3. Deferred Response Followed by a Deferred Reply to a Read Operation. . . .5-18

Figure 8-1. BERR# Protocol Mechanism . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-8

Figure 8-2. BINIT# Protocol Mechanism. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-10

Figure 8-3. Pentium® Pro Processor Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-11

Figure 9-1. Hardware Configuration Signal Sampling. . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-1

Figure 9-2. BR[3:0]# Physical Interconnection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-7

Figure 10-1. Simplified Block Diagram of Pentium® Pro Processor TAP logic . . . . . . . . . .10-1

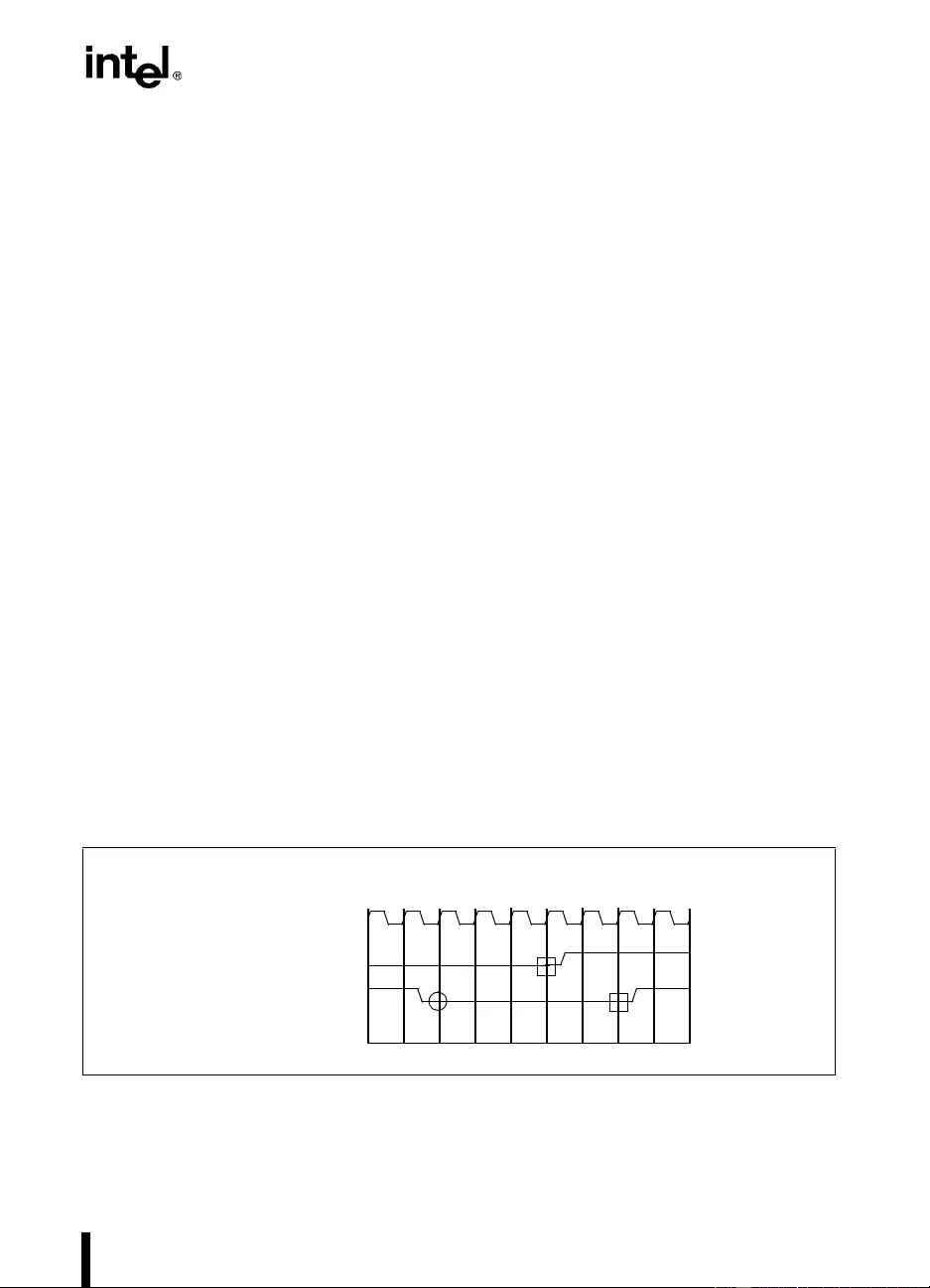

Figure 10-2. TAP Controller Finite State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-2

Figure 10-3. Pentium® Pro Processor TAP instruction Register . . . . . . . . . . . . . . . . . . . . .10-4

xv

TABLE OF FIGURES

PAGE

Figure 10-4. Operation of the Pentium® Pro Processor TAP Instruction Register. . . . . . . 10-5

Figure 10-5. TAP Instruction Register Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-6

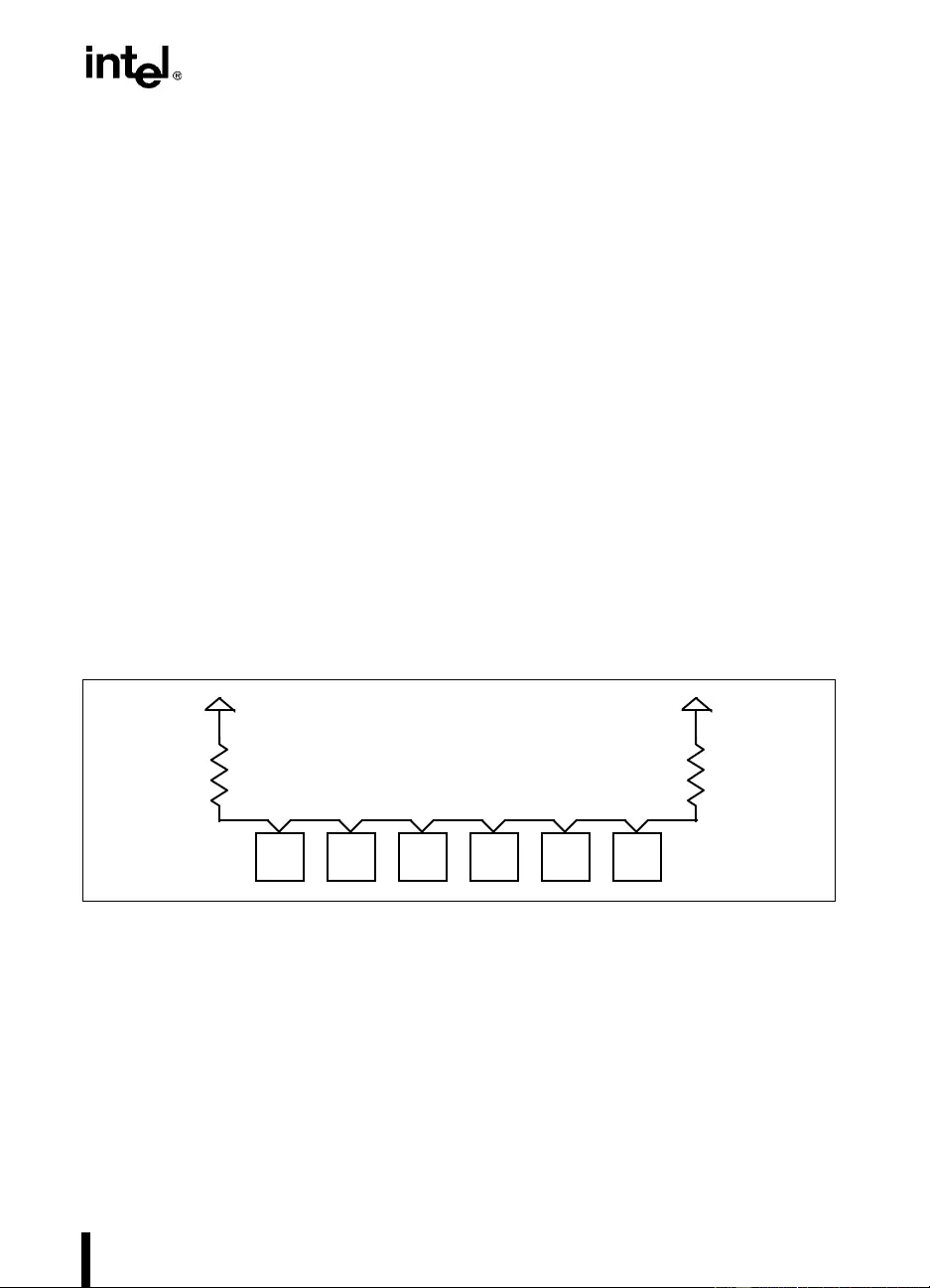

Figure 11-1. GTL+ Bus Topology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

Figure 11-2. Transient Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-3

Figure 11-3. Timing Diagram of Clock Ratio Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-5

Figure 11-4. Example Schematic for Clock Ratio Pin Sharing . . . . . . . . . . . . . . . . . . . . . 11-6

Figure 11-5. PWRGOOD Relationship at Power-On. . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-11

Figure 11-6. 3.3V Tolerant Group Derating Curve . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-21

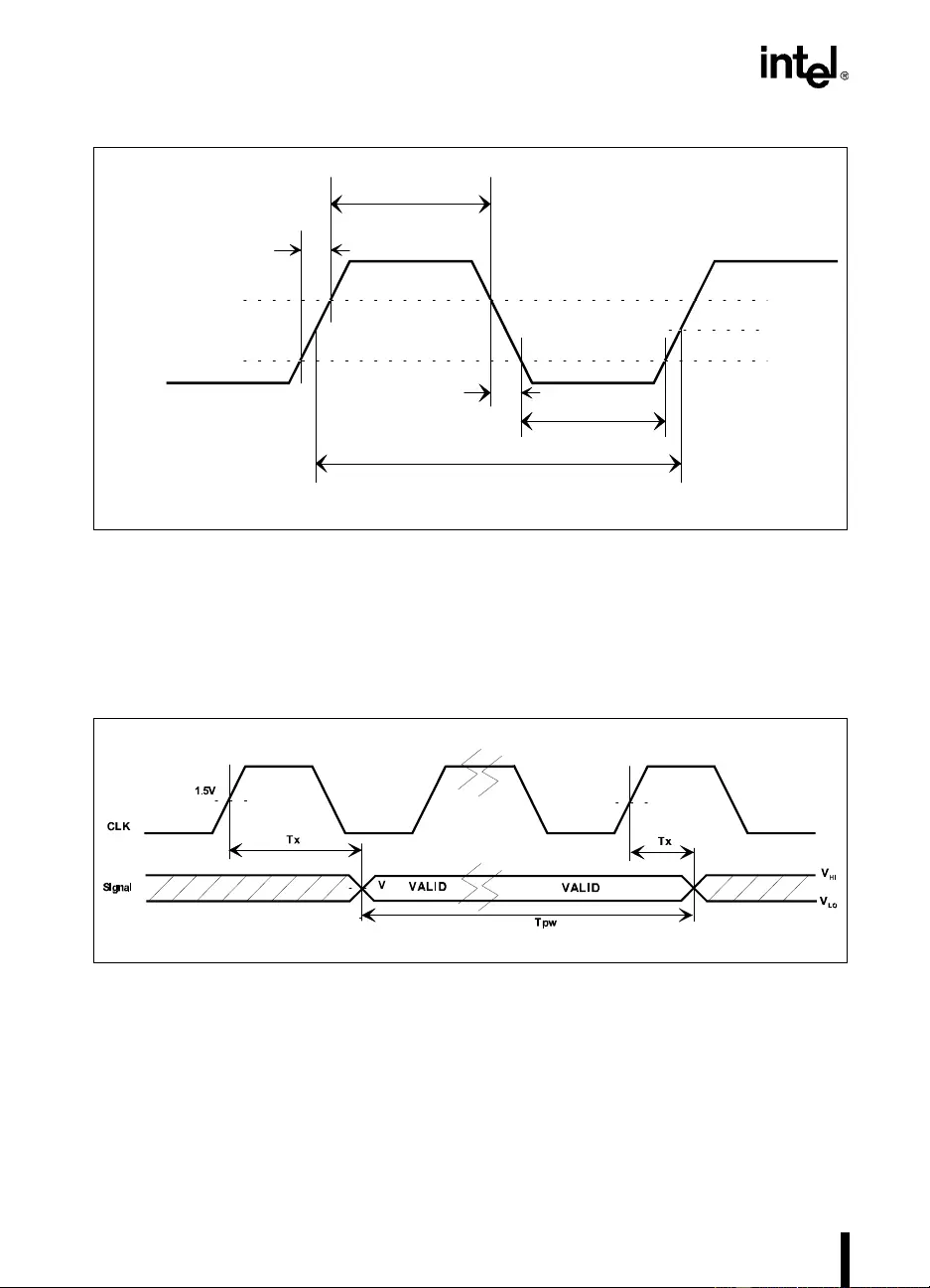

Figure 11-7. Generic Clock Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-24

Figure 11-8. Valid Delay Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-24

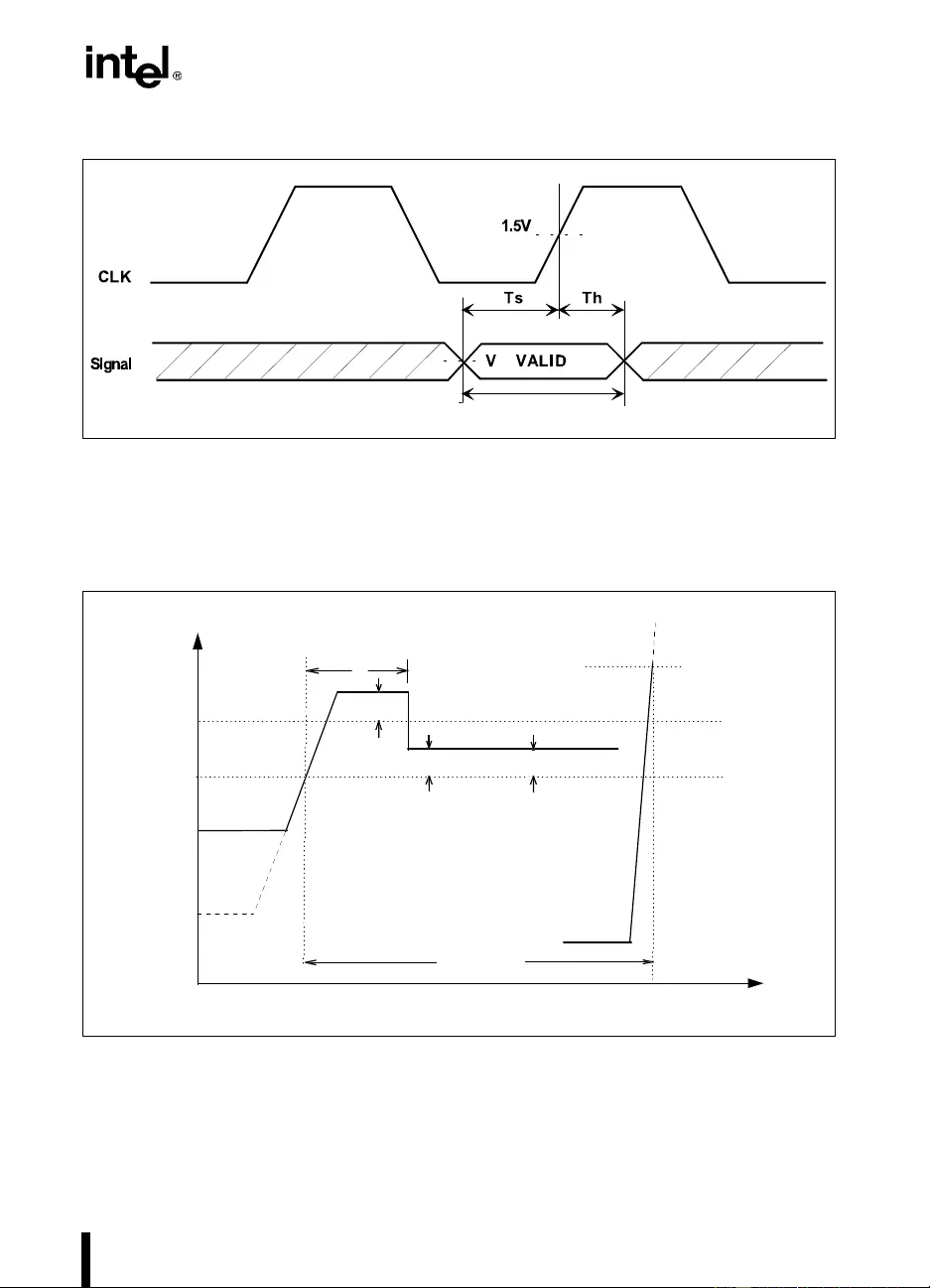

Figure 11-9. Setup and Hold Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-25

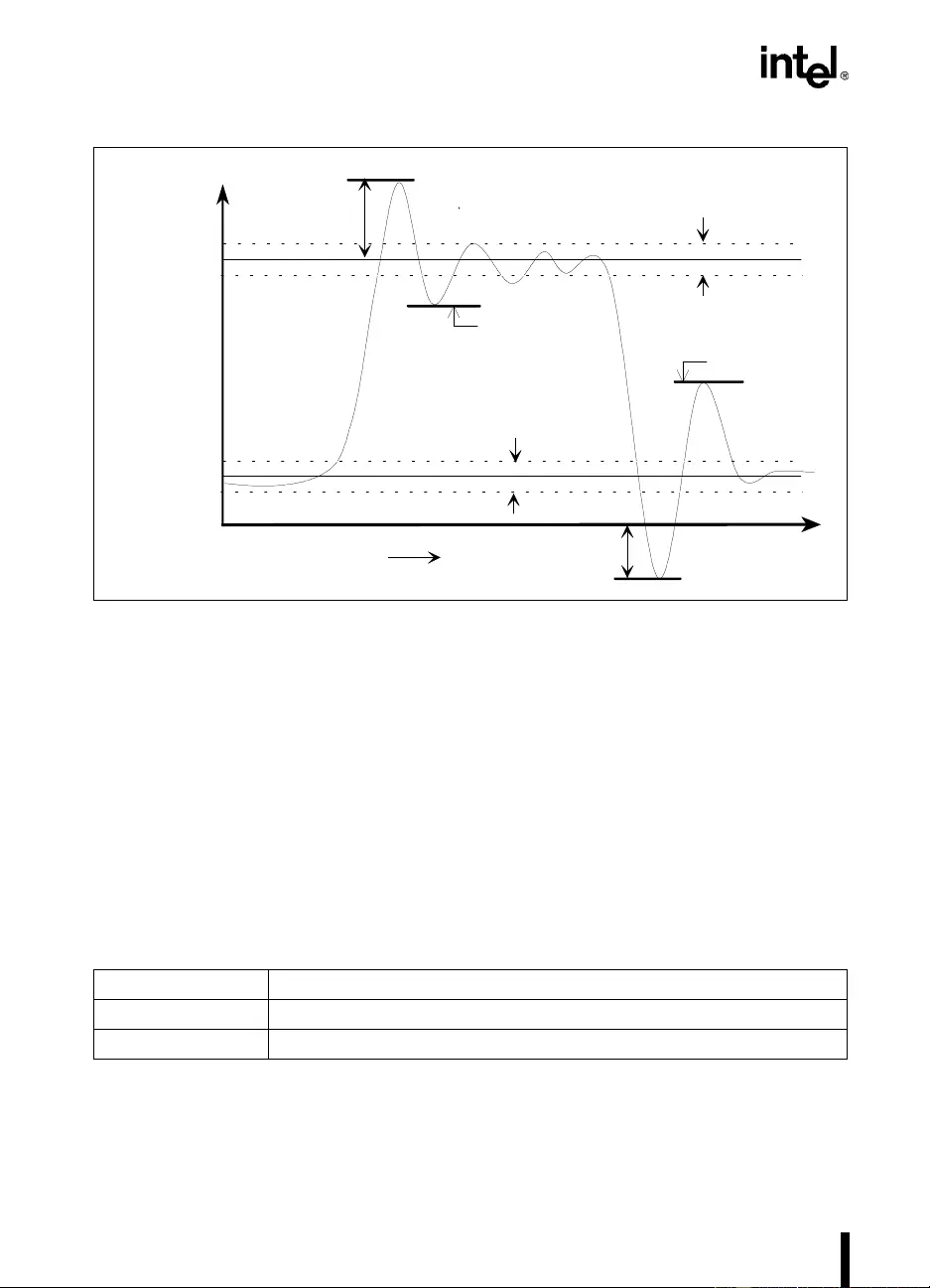

Figure 11-10. Lo to Hi GTL+ Receiver Ringback Tolerance . . . . . . . . . . . . . . . . . . . . . . . 11-25